**Calhoun: The NPS Institutional Archive**

**DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

1996-09

# Low-power high-speed dynamic logic families for complementary gallium arsenide (CGaAs) fabrication processes

Shehata, Khaled Ali

Monterey, California. Naval Postgraduate School

https://hdl.handle.net/10945/8639

Copyright is reserved by the copyright owner

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NAVAL POSTGRADUATE SCHOOL Monterey, California

# **DISSERTATION**

LOW-POWER HIGH-SPEED

DYNAMIC LOGIC FAMILIES FOR

COMPLEMENTARY GALLIUM ARSENIDE (CGaAs)

FABRICATION PROCESSES

by

Khaled Ali Shehata

September 1996

Dissertation Advisor:

Douglas J. Fouts

Thesis \$4387

Approved for public release; distribution is unlimited.

DUDIEY WITE LUTTERY

LEFE CA 93343-5101

### REPORT DOCUMENTATION PAGE

Form Approved

OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response including the time reviewing instructions searching existing data sources gathering and palestaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden to Washington. Headquariers Services. Directorate for information, Department and Report. 1215 Jefferson Davis Highway, Suite 1204, Arkington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188), Washington, DC 20503

1. AGENCY USE ONLY (Leave Blank)

2. REPORT DATE

September 1996

3. REPORT TYPE AND DATES COVERED Ph.D. Dissertation

4. TITLE AND SUBTITLE

LOW-POWER HIGH-SPEED DYNAMIC LOGIC FAMILIES FOR COMPLEMENTARY GALLIUM ARSENIDE (CG&As) FABRICATION PROCESSES

6. AUTHOR(S)

Khaled Ali Shehata.

7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)

Naval Postgraduate School Monterey, CA 93943-5000

9. SPONSORING/ MONITORING AGENCY NAME(S) AND ADDRESS(ES)

10. SPONSORING/ MONITORING AGENCY REPORT NUMBER

8. PERFORMING ORGANIZATION

### 11. SUPPLEMENTARY NOTES

The views expressed in this dissertation are those of the author and do not reflect the official policy or position of the Department of Defense or the United States Government.

### 12a. DISTRIBUTION / AVAILABILITY STATEMENT

Approved for public release; distribution is unlimited

12b. DISTRIBUTION CODE

### 13. ABSTRACT (Maximum 200 words)

The design and evaluation of several different low-power, high-speed, high-density complementary gallium arsenide (CGaAs) dynamic logic families that are compatible with existing CGaAs fabrication processes and design tools are documented. Circuits studied include Domino logic, N-P Domino logic and Two-Phase Dynamic FET Logic (TPDL). The TPDL circuits have been implemented and fabricated. The dynamic circuits are evaluated and compared with typical static logic circuits for speed, power consumption and layout area.

Dynamic circuits are non-ratioed logic. Therefore, the transistor sizes can be minimized to reduce the layout area and the power dissipation of the circuits. Furthermore, dynamic circuits are faster than static circuits because they do not use PFETs for evaluation, only for precharging. Dynamic circuits consume less power than the static circuits because they have no short-circuit current and a reduced leakage current (only switching current flows in the dynamic circuits). This means that CGaAs dynamic logic circuits have higher speed than Directly-Coupled FET Logic (DCFL) and lower power consumption than complementary GaAs logic.

#### 15. NUMBER OF PAGES 14. SUBJECT TERMS 281 GaAs, Dynamic Logic, CHIGFET, CGaAs, Two-Phase Dynamic FET Logic, 16. PRICE CODE TPDL, Clock Generator, Domino logic, N-P Domino logic, CLA, static logic. 17. SECURITY CLASSIFICATION 19. SECURITY CLASSIFICATION 20. LIMITATION OF ABSTRACT 18. SECURITY CLASSIFICATION OF REPORT OF THIS PAGE OF ABSTRACT UL Unclassified Unclassified Unclassified

| 13. The TPDL circuits designed for this dissertation are the fastest low-power logic circuits ever reported in this technology. The use of TPDL in CGaAs technology will enhance the CGaAs advantages by increasing the maximum speed and reducing the power dissipation. CGaAs TPDL is an excellent candidate for the next generation of high speed, high density and low power ICs and is ideal for digital signal processing and digital communication ICs. |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

Approved for public release; distribution is unlimited.

# LOW-POWER HIGH-SPEED DYNAMIC LOGIC FAMILIES FOR COMPLEMENTARY GALLIUM ARSENIDE (CGaAs) FABRICATION PROCESSES

Khaled Ali Shehata

Lt. Col., Egyptian Air Force

B.S., Military Technical College, Cairo, Egypt, 1981

M.S., Cairo University, Cairo, Egypt, 1991

# DOCTOR OF PHILOSOPHY IN ELECTRICAL AND COMPUTER ENGINEERING

from the

NAVAL POSTGRADUATE SCHOOL September 1996

### ABSTRACT

The design and evaluation of several different low-power, high-speed, high-density complementary gallium arsenide (CGaAs) dynamic logic families that are compatible with existing CGaAs fabrication processes and design tools are documented. Circuits studied include Domino logic, N-P Domino logic and Two-Phase Dynamic FET Logic (TPDL). The TPDL circuits have been implemented and fabricated. The dynamic circuits are evaluated and compared with typical static logic circuits for speed, power consumption and layout area.

Dynamic circuits are non-ratioed logic. Therefore, the transistor sizes can be minimized to reduce the layout area and the power dissipation of the circuits. Furthermore, dynamic circuits are faster than static circuits because they do not use PFETs for evaluation, only for precharging. Dynamic circuits consume less power than the static circuits because they have no short-circuit current and a reduced leakage current (only switching current flows in the dynamic circuits). This means that CGaAs dynamic logic circuits have higher speed than Directly-Coupled FET Logic (DCFL) and lower power consumption than complementary GaAs logic.

The TPDL circuits designed for this dissertation are the fastest low-power logic circuits ever reported in this technology. The use of TPDL in CGaAs technology will enhance the CGaAs advantages by increasing the maximum speed and reducing the power dissipation. CGaAs TPDL is an excellent candidate for the next generation of high speed, high density and low power ICs and is ideal for digital signal processing and digital communication ICs.

## TABLE OF CONTENTS

| [.  | INTRO | DUCTION                                                                                                                                                                                                                                                                                                              | . 1                                |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|     | A.    | HISTORICAL REVIEW OF GALLIUM ARSENIDE (GaAs)                                                                                                                                                                                                                                                                         | . 1                                |

|     | В.    | COMPARISON BETWEEN GALLIUM ARSENIDE (GaAs) AND SILICON (SI) ELECTRICAL PROPERTIES  1. Electron Mobility 2. Semi-insulating Substrate 3. Radiation Hardness 4. Hole Mobility 5. Other Properties                                                                                                                      | . 2<br>. 3<br>. 3                  |

|     | C.    | GaAs DEVICES  1. Noise in Digital Circuits  2. Power Dissipation in GaAs Circuits  3. Depletion-Mode Logic Circuits  4. Enhancement/Depletion Mode Logic Circuits                                                                                                                                                    | . 5<br>. 6<br>. 6                  |

|     | D.    | GaAs MESFET STATIC LOGIC CIRCUITS  1. Directly-Coupled FET Logic (DCFL)  2. Buffered FET Logic (BFL)  3. Schottky Diode FET Logic (SDFL)  4. Source-Coupled FET Logic (SCFL)  5. Alternative Logic Families  a. Capacitor-Coupled Logic (CCL)  b. Capacitor Diode FET Logic (SBFL)  c. Super-Buffer FET Logic (SBFL) | . 8<br>. 9<br>10<br>11<br>12<br>12 |

|     | E.    | DYNAMIC LOGIC CIRCUITS  1. CMOS Dynamic Logic  a. Domino Logic  b. N-P Domino Logic  c. Two-Phase Dynamic Logic  2. GaAs MESFET Dynamic Logic Families                                                                                                                                                               | 16<br>16<br>18<br>19               |

|     | F.    | OUTLINE OF DISSERTATION                                                                                                                                                                                                                                                                                              | 24                                 |

| II. | COMP  | LEMENTARY GALLIUM ARSENIDE (CGaAs) TECHNOLOGY                                                                                                                                                                                                                                                                        | 27                                 |

|     | A.    | OVERVIEW OF COMPLEMENTARY GaAs                                                                                                                                                                                                                                                                                       | 27                                 |

|     | B. | APPLICATIONS FOR COMPLEMENTARY GaAs                                                                                                                                                                                                        | 29                   |

|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

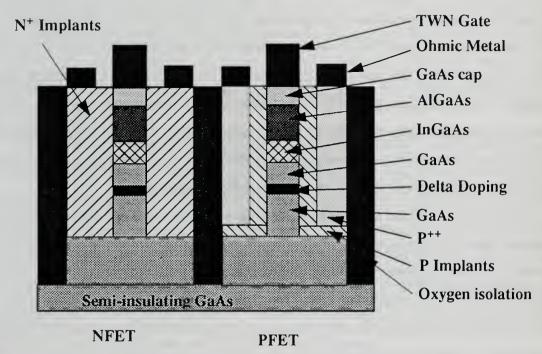

|     | C. | GaAs CHIGFET STRUCTURE AND FABRICATION                                                                                                                                                                                                     | 29                   |

|     | D. | GaAs CHIGFET GATE CURRENT                                                                                                                                                                                                                  | 30                   |

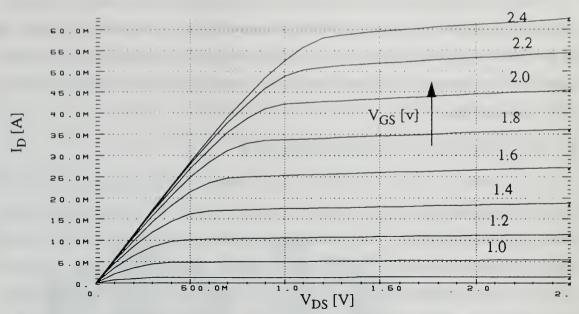

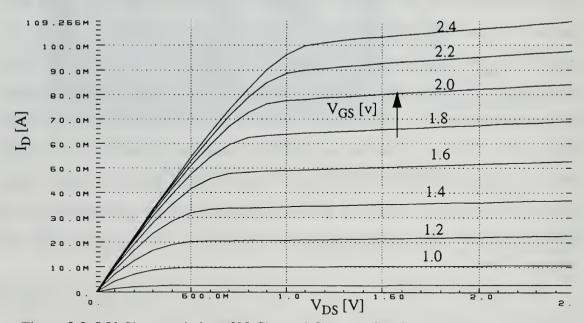

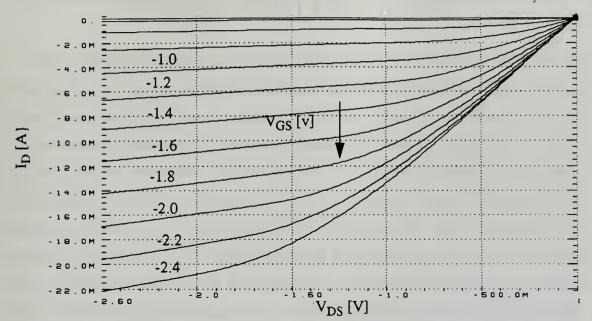

|     | E. | GaAs CHIGFET I-V CHARACTERISTICS                                                                                                                                                                                                           | 31                   |

| IП. |    | N AND ANALYSIS OF CGaAs STATIC AND DYNAMIC INATIONAL LOGIC GATES                                                                                                                                                                           | 35                   |

|     | A. | CGaAs STATIC CIRCUIT DESIGN  1. Static Inverter Circuit Design  2. Static NAND and NOR Gates Circuit Design  3. Static XOR Gate Circuit Design  4. Static XNOR Gate Circuit Design  5. CGaAs Ring Oscillator Design Using Static NOR Gates | 36<br>39<br>44<br>46 |

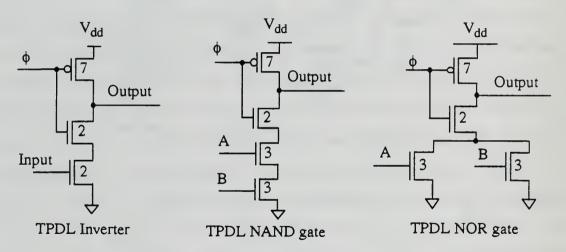

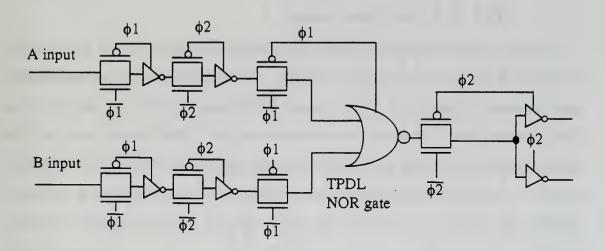

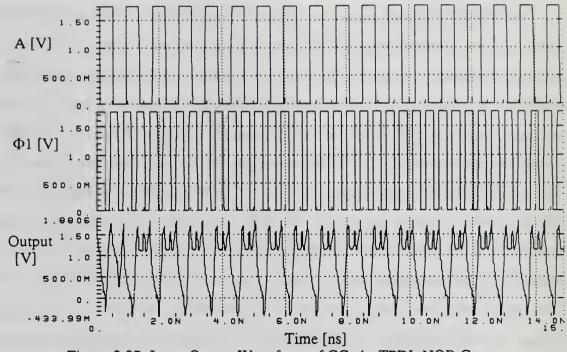

|     | В. | CGaAs TPDL CIRCUIT DESIGN  1. TPDL Inverter Circuit Design  2. TPDL NAND Gate Circuit Design  3. TPDL NOR Gate Circuit Design  4. TPDL XOR Gate Circuit Design  5. TPDL XNOR Gate Circuit Design                                           | 51<br>53<br>57       |

|     | C. | DESIGN OF CGaAs TWO PHASE NON-OVERLAPPING CLOCK GENERATOR                                                                                                                                                                                  | 61                   |

|     | D. | COMPARISON BETWEEN CGaAs STATIC AND TPDL COMBINATIONAL LOGIC CIRCUIT DESIGNS                                                                                                                                                               | 66                   |

| IV. |    | N AND ANALYSIS OF COMPLEMENTARY GaAs STATIC AND MIC SEQUENTIAL CIRCUITS                                                                                                                                                                    | 71                   |

|     | A. | CGaAs STATIC SEQUENTIAL CIRCUITS  1. D-Latch Circuit  2. D Flip Flop (D-FF) Circuit Design  3. Divide-By-Two Circuit Using D Flip Flops  4. Linear Feedback Shift Registers (LFSRs)  a. Three-Bit LFSR.  b. Four-Bit LFSR.                 | 71<br>73<br>74<br>76 |

|     | B. | CGaAs TPDL SEOUENTIAL CIRCUITS                                                                                                                                                                                                             | 81                   |

|      |    | <ol> <li>D Flip Flop (DFF) Circuit</li> <li>Linear Feedback Shift Registers (LFSR)</li> <li>a. Three-Bit LFSR</li> <li>b. Four-Bit LFSR</li> </ol> | 3  |

|------|----|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | C. | COMPARISON BETWEEN STATIC AND TPDL SEQUENTIAL CIRCUIT SIMULATION RESULTS                                                                           | 6  |

| V.   |    | N OF TWO-LEVEL LOGIC FUNCTIONS USING COMPLEMENTARY TATIC AND DYNAMIC LOGIC FAMILIES                                                                | 9  |

|      | A. | CGaAs STATIC LOGIC CIRCUIT DESIGN9                                                                                                                 | 0  |

|      | B. | CGaAs DOMINO LOGIC CIRCUIT DESIGN                                                                                                                  | 6  |

|      | C. | CGaAs N-P DOMINO LOGIC CIRCUIT DESIGN                                                                                                              | 3  |

|      | D. | CGaAs TWO-PHASE DYNAMIC LOGIC (TPDL) CIRCUIT DESIGN 10                                                                                             | 9  |

|      | E. | COMPARISON BETWEEN CGaAs LOGIC FAMILIES                                                                                                            | 6  |

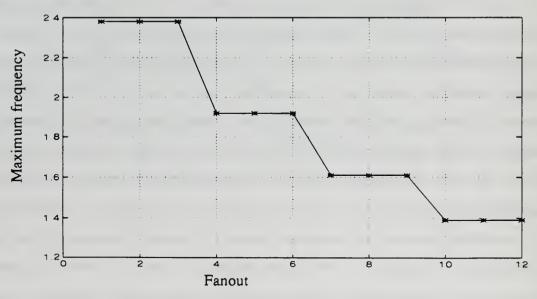

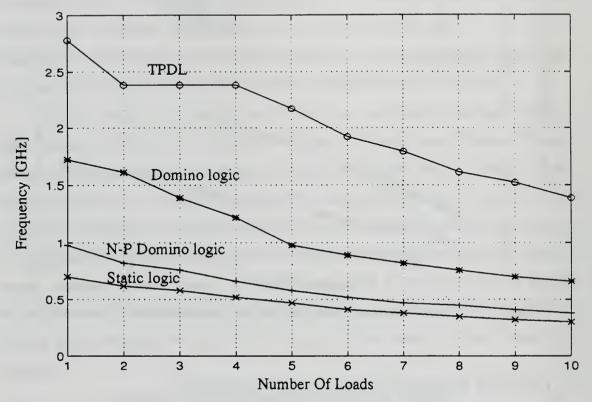

|      | F. | LOADING EFFECTS ON CGaAs LOGIC FAMILIES                                                                                                            | 9  |

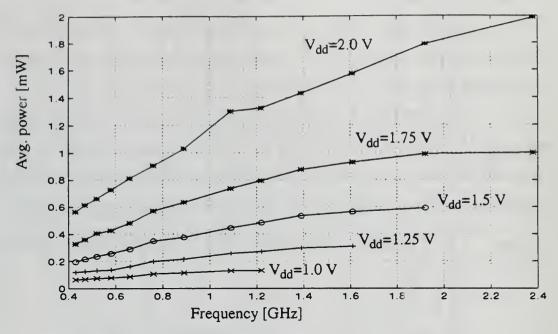

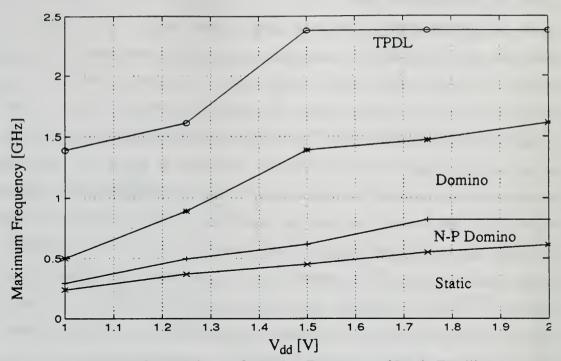

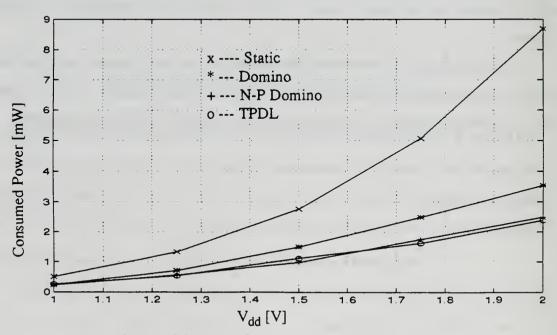

|      | G. | EFFECT OF POWER SUPPLY VOLTAGE ON CGaAs LOGIC FAMILIES                                                                                             | 0  |

| VI.  |    | N OF COMPLEMENTARY GaAs MULTI-LEVEL TPDL AND STATIC CIRCUITS                                                                                       | 3  |

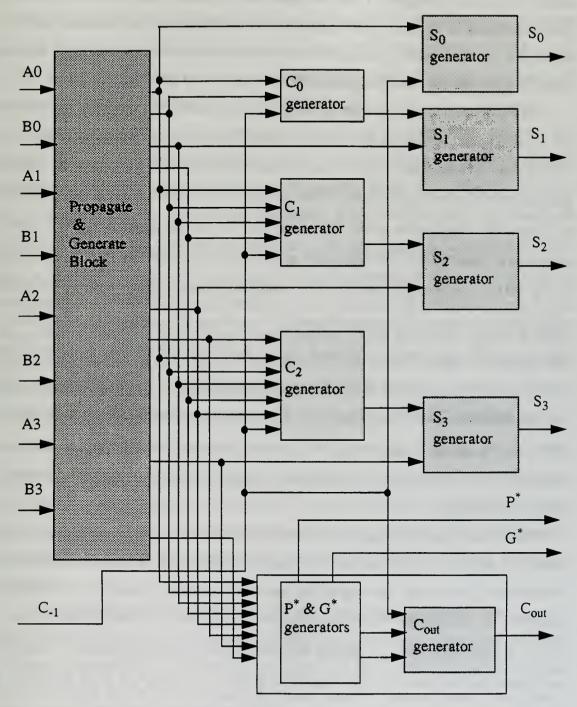

|      | A. | CARRY-LOOKAHEAD ADDER OVERVIEW 12  1. Basic Add/Subtract logic 12  2. Carry Generate, Propagate and Lookahead Functions 12                         | 4  |

|      | B. | CGaAs STATIC 4-Bit CLA CIRCUIT DESIGN                                                                                                              | 8  |

|      | C. | CGaAs TPDL 4-Bit CLA CIRCUIT DESIGN                                                                                                                | 5  |

|      | D. | COMPARISON BETWEEN CGaAs STATIC, PIPLINED STATIC AND TPDL 4-Bit CLA                                                                                | 2  |

| VII. |    | LEMENTARY GaAs CIRCUIT IMPLEMENTATIONS AND TEST TS                                                                                                 | .7 |

|        | A.          | CGaAs INPUT RECEIVER AND OUTPUT DRIVER CIRCUITS | . 148 |

|--------|-------------|-------------------------------------------------|-------|

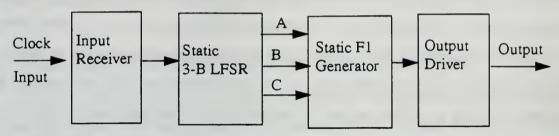

|        | B.          | CGaAs STATIC 3-BIT LFSR CIRCUIT                 | . 149 |

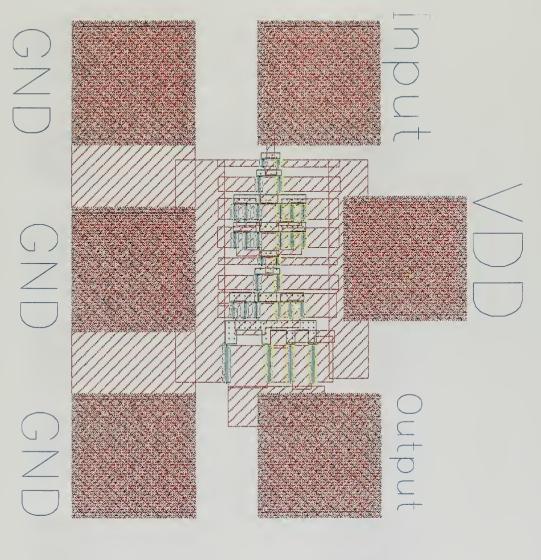

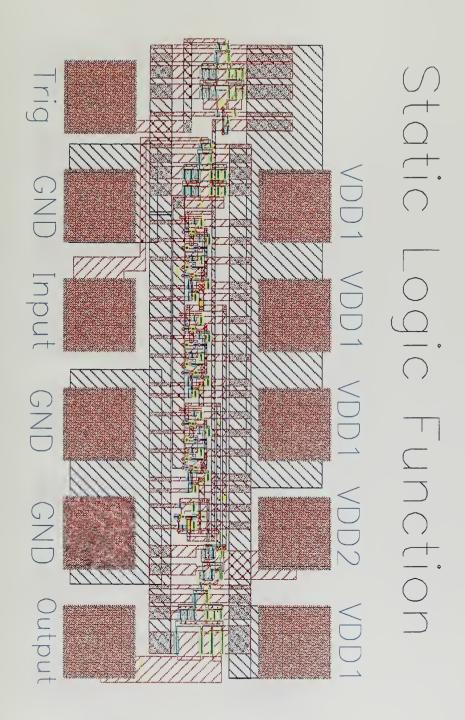

|        | C.          | CGaAs STATIC TWO-LEVEL FUNCTION GENERATION      | . 149 |

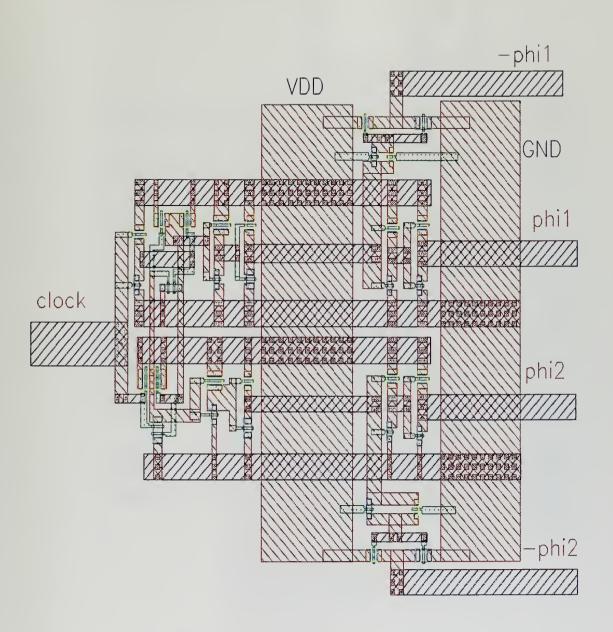

|        | D.          | CGaAs NON-OVERLAPING TWO-PHASE CLOCK GENERATOR  | . 150 |

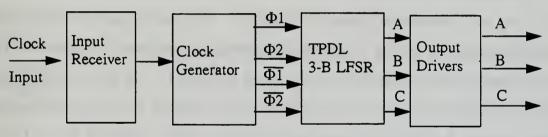

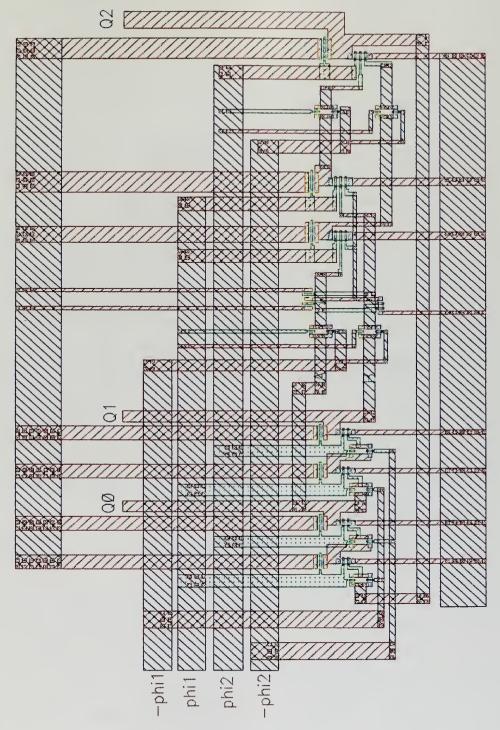

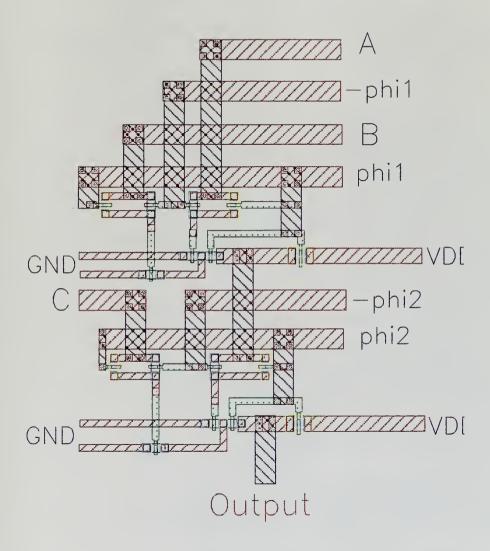

|        | E.          | CGaAs TPDL 3-BIT LFSR CIRCUIT                   | . 150 |

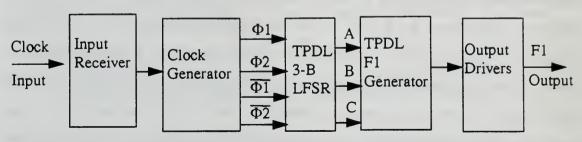

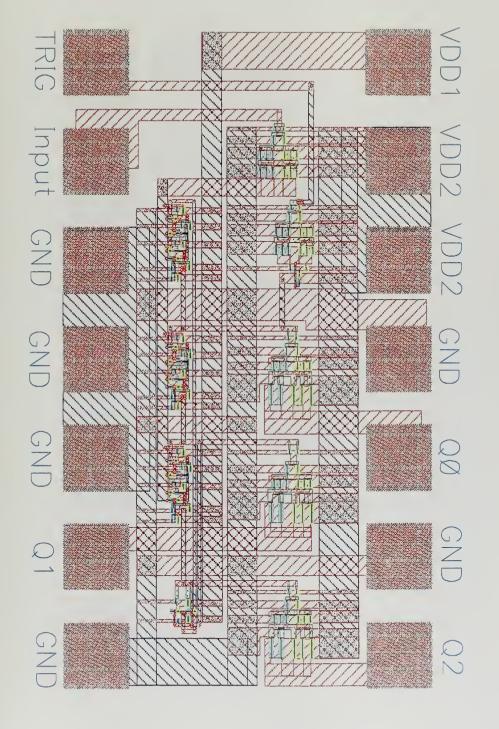

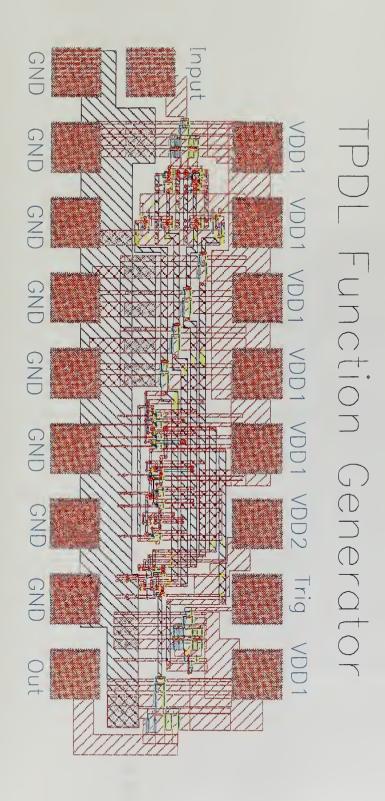

|        | F.          | CGaAs TPDL TWO-LEVEL FUNCTION GENERATION        | . 151 |

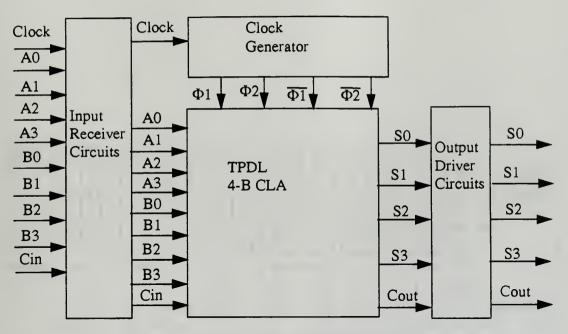

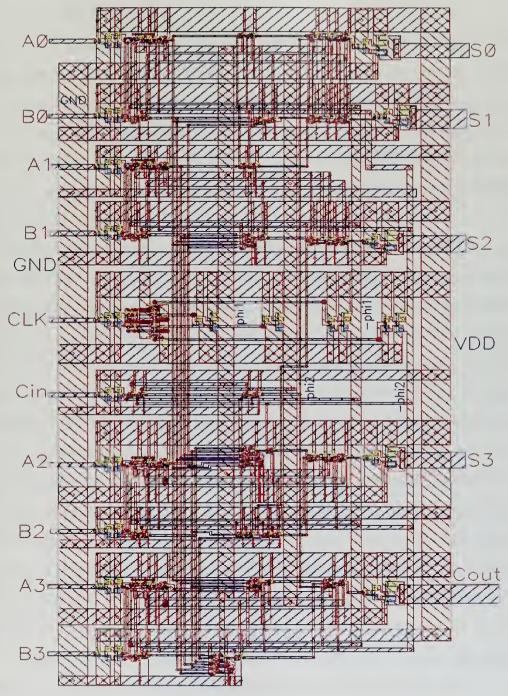

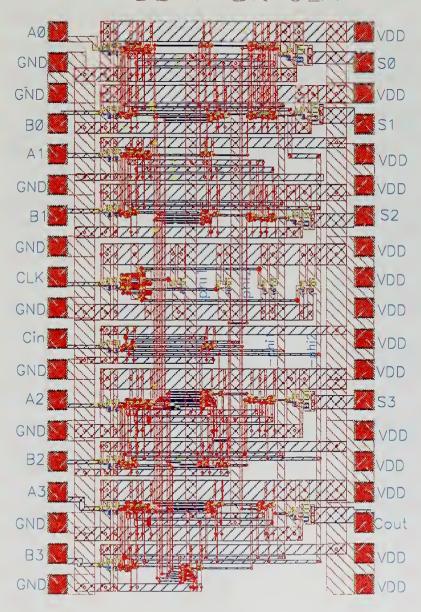

|        | G.          | CGaAs TPDL 4-BIT CARRY LOOKAHEAD ADDER CIRCUIT  | . 152 |

| VIII.C | ONC         | LUSIONS AND CONTINUATION OF WORK                | . 169 |

|        | A.          | CONCLUSIONS                                     | . 169 |

|        | B.          | CONTINUATION OF WORK                            | . 172 |

| APPE   | NDIX        | A: HSPICE SIMULATION FILES                      | . 173 |

|        | A.1         | CGaAs INPUT/OUTPUT DRIVER IC                    | . 174 |

|        | A.2         | CGaAs STATIC 3-BIT LFSR IC                      | . 179 |

|        | A.3         | CGaAs STATIC F1 GENERATOR IC                    | . 185 |

|        | A.4         | CGaAs TWO-PHASE CLOCK GENERATOR IC              | . 191 |

|        | A.5         | CGaAs TPDL 3-BIT LFSR IC                        | . 200 |

|        | A.6         | CGaAs TPDL F1 GENERATOR IC                      | . 211 |

|        | <b>A</b> .7 | CGaAs STATIC 4-BIT CLA CIRCUIT                  | . 223 |

|        | A.8         | CGaAs TPDL 4-BIT CLA IC                         | . 231 |

| APPE   | NDIX        | B: INTEGRATED CIRCUIT LAYOUTS                   | . 241 |

| LIST   | OF RE       | EFERENCES                                       | . 249 |

| INITI  | AL DI       | STRIBUTION LIST                                 | 255   |

## LIST OF FIGURES

| 1.1  | Directly-Coupled FET Logic (DCFL) Inverter                        | 9  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Buffered FET Logic (BFL) Inverter                                 | 10 |

| 1.3  | Three-input Schottky Diode FET Logic (SDFL) NOR Gate              | 11 |

| 1.4  | Source-Coupled FET Logic (SCFL) Inverter (Differential Inputs)    | 12 |

| 1.5  | Capacitor-Coupled Logic (CCL) Inverters                           | 13 |

| 1.6  | Capacitor Diode FET Logic (CDFL) Inverter                         | 13 |

| 1.7  | Super-Buffer FET Logic (SBFL) Inverter                            | 14 |

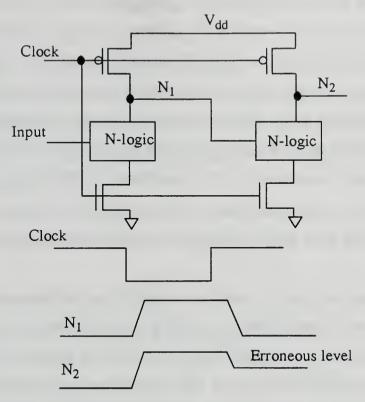

| 1.8  | Erroneous Evaluation in Cascaded Dynamic CMOS Gates               | 16 |

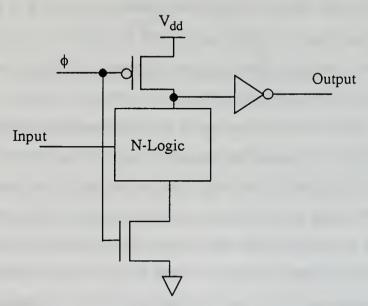

| 1.9  | Dynamic Domino Logic Gate                                         | 17 |

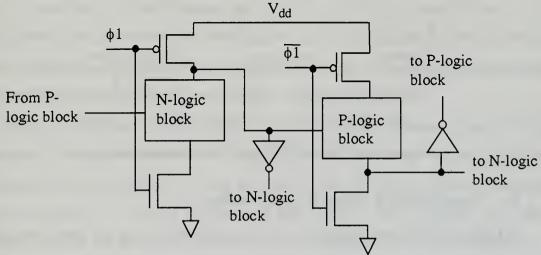

| 1.10 | N-P Domino Dynamic Logic Gate                                     | 19 |

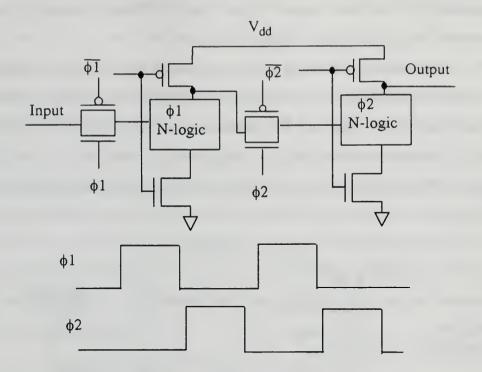

| 1.11 | Clocking of Two-Phase Dynamic Logic                               | 20 |

| 1.12 | GaAs MESFET Domino 3-Input AND Gate                               | 22 |

| 1.13 | GaAs MESFET CCDL 3-Input AND Gate                                 | 22 |

| 1.14 | GaAs MESFET TTDL 3-Input AND Gate                                 | 23 |

| 1.15 | Two GaAs MESFET TDFL Inverters in Series                          | 23 |

| 2.1  | GaAs CHIGFET Transistor Structure                                 | 30 |

| 2.2  | I-V Characteristics of N-Channel GaAs HIGFET Transistor (W=10 μm) | 32 |

| 2.3  | I-V Characteristics of N-Channel GaAs HIGFET Transistor (W=20 μm) | 32 |

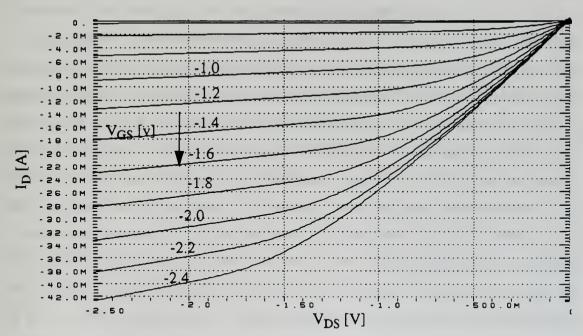

| 2.4  | I-V Characteristics of P-Channel GaAs HIGFET Transistor (W=10 μm) | 33 |

| 2.5  | I-V Characteristics of P-Channel GaAs HIGFET Transistor (W=20 μm) | 33 |

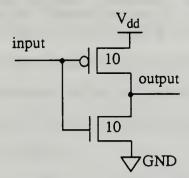

| 3.1  | CGaAs Static Inverter                                             | 37 |

| 3.2  | CGaAs Static Inverter Test Circuit                                | 37 |

| 3.3  | DC Transfer Characteristics of CGaAs Static Inverter              | 38 |

| 3.4  | Transient Analysis of CGaAs Static Inverter                       | 39 |

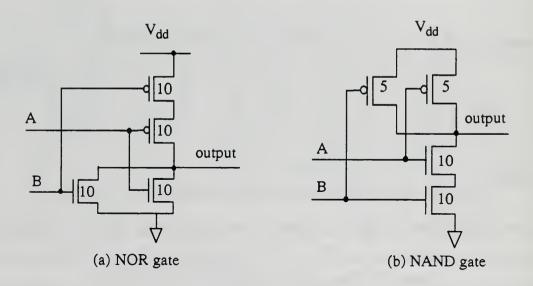

| 3.5  | CGaAs Static NAND and NOR Gates                                   | 40 |

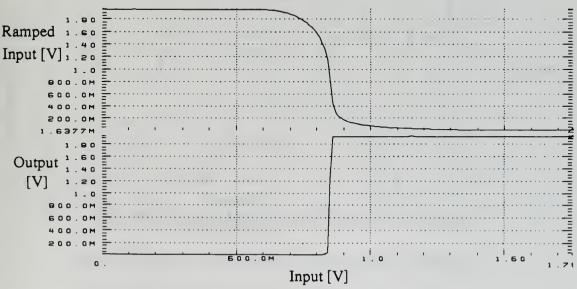

| 3.6  | DC Transfer Curve of CGaAs Static NAND Gate                       | 41 |

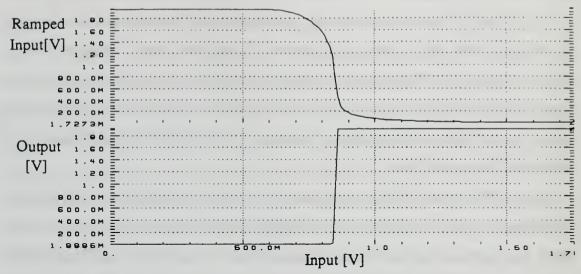

| 3.7  | DC Transfer Curve of CGaAs Static NOR Gate                        | 42 |

| 3.8  | Transient Analysis of CGaAs Static NAND Gate              | 42 |

|------|-----------------------------------------------------------|----|

| 3.9  | Transient Analysis of CGaAs Static NOR Gate               | 43 |

| 3.10 | Power Consumption of CGaAs Static NAND Gate               | 43 |

| 3.11 | Loading Effects on CGaAs Static NAND Gate                 | 44 |

| 3.12 | CGaAs Static Six-Transistor XOR Gate                      | 45 |

| 3.13 | CGaAs Static Eight-Transistor XOR Gate                    | 46 |

| 3.14 | CGaAs Static Ten-Transistor XNOR Gate                     | 47 |

| 3.15 | CGaAs Static Eight-Transistor XNOR Gate                   | 47 |

| 3.16 | CGaAs Eleven NOR Gate Ring Oscillator                     | 48 |

| 3.17 | Output Waveforms of CGaAs Eleven NOR Gate Ring Oscillator | 49 |

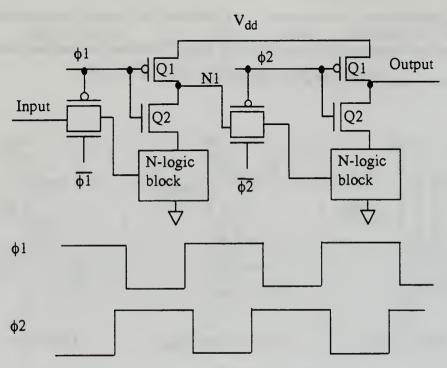

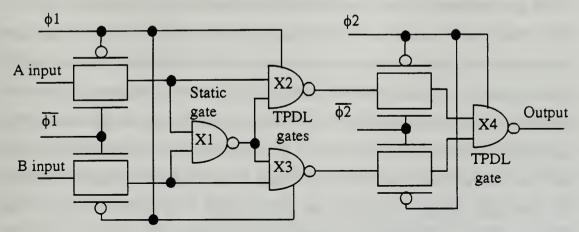

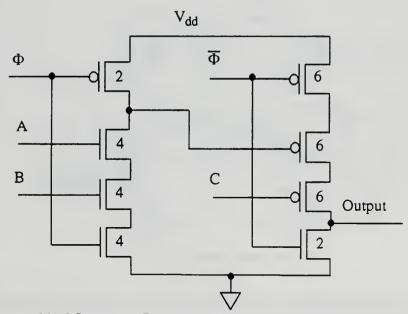

| 3.18 | Basic Circuit Topology of CGaAs TPDL Gate                 | 51 |

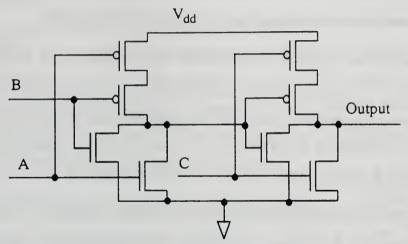

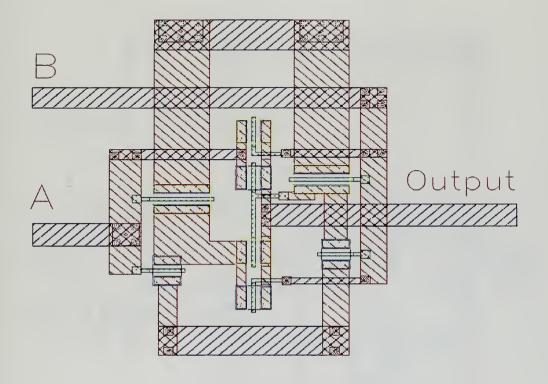

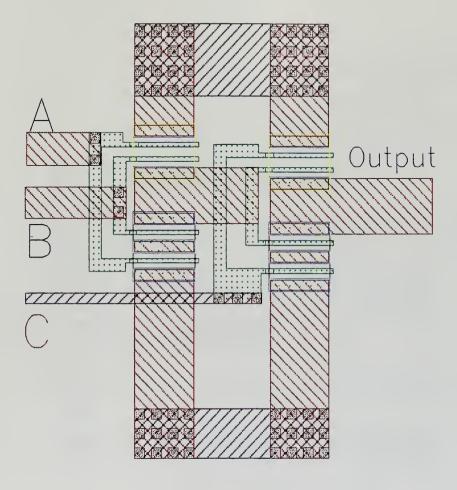

| 3.19 | CGaAs TPDL Combinational Logic Gates                      | 52 |

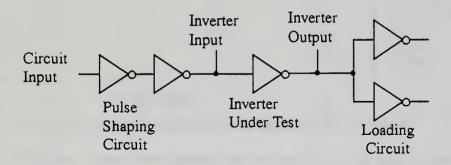

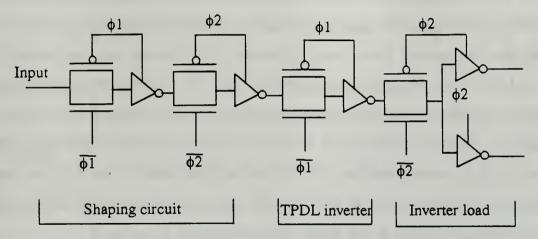

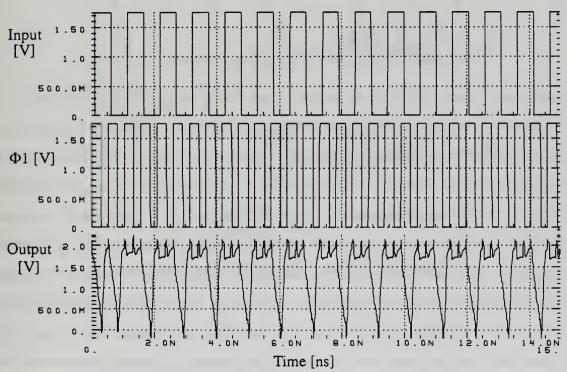

| 3.20 | CGaAs TPDL Inverter Test Circuit                          | 53 |

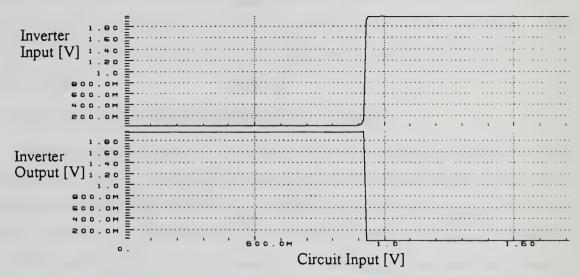

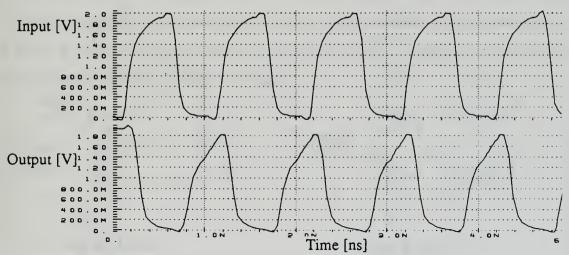

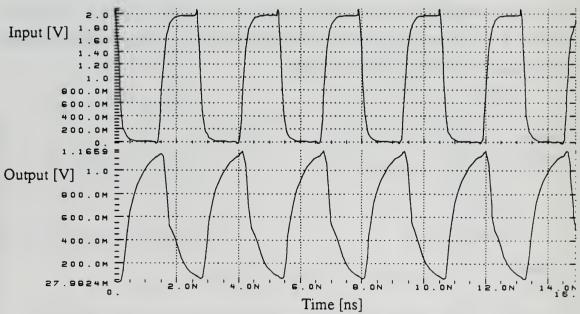

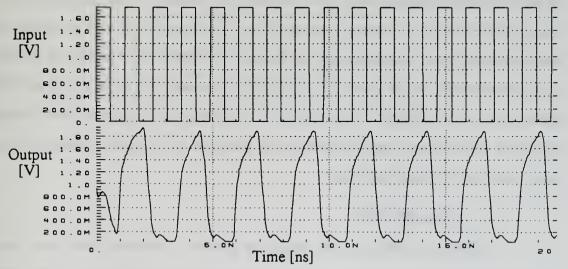

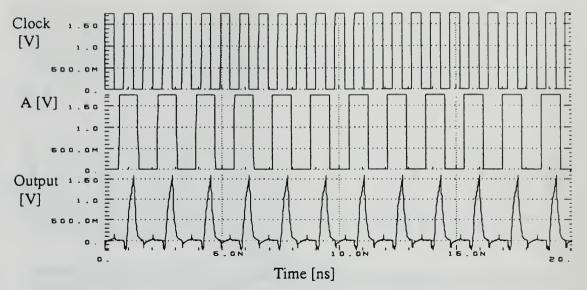

| 3.21 | Input-Output Waveforms of CGaAs TPDL Inverter             | 53 |

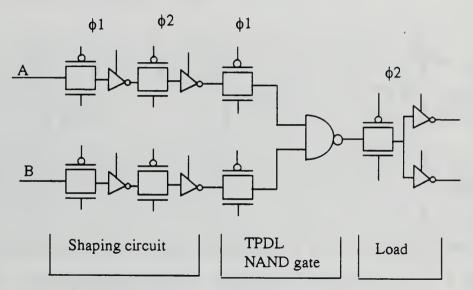

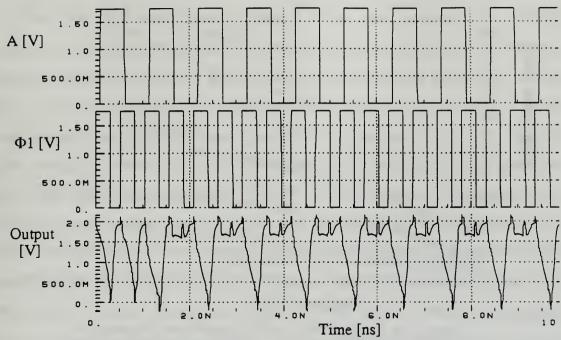

| 3.22 | CGaAs TPDL NAND Gate Test Circuit                         | 54 |

| 3.23 | Transient Analysis of CGaAs TPDL NAND Gate                | 55 |

| 3.24 | CGaAs TPDL NAND Gate Power Consumption                    | 56 |

| 3.25 | Loading Effects on CGaAs TPDL NAND Gate                   | 56 |

| 3.26 | CGaAs TPDL NOR Gate Test Circuit                          | 57 |

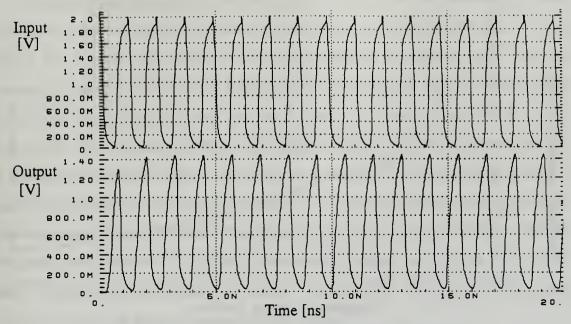

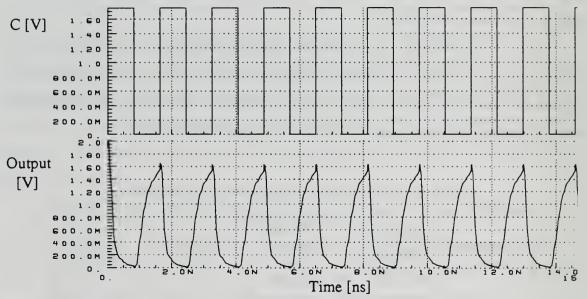

| 3.27 | Input-Output Waveform of CGaAs TPDL NOR Gate              | 58 |

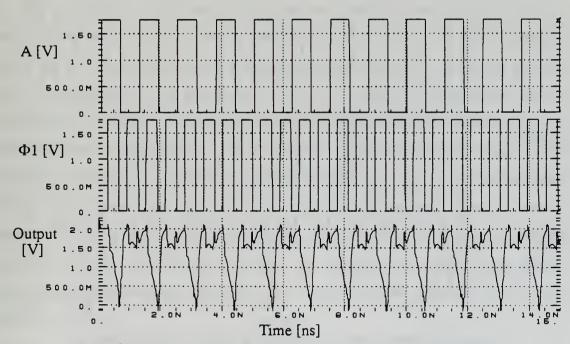

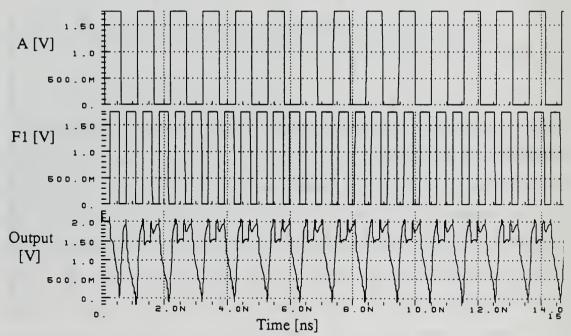

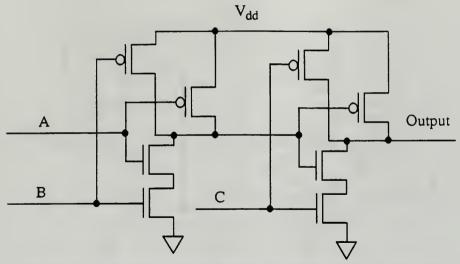

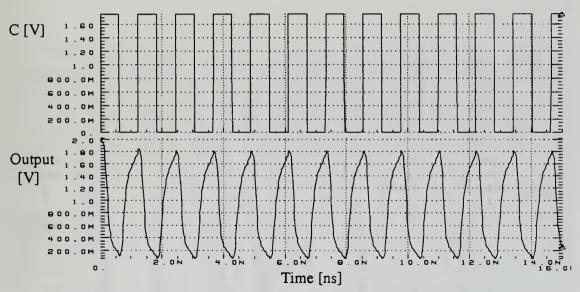

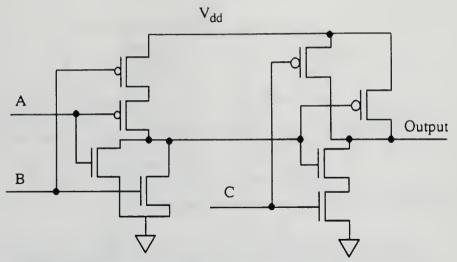

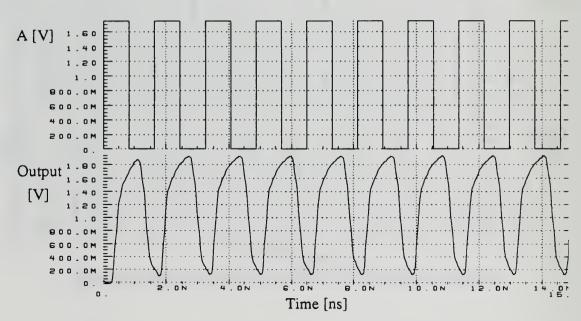

| 3.28 | CGaAs TPDL XOR Gate                                       | 59 |

| 3.29 | Input-Output Waveforms of CGaAs TPDL XOR Gate             | 59 |

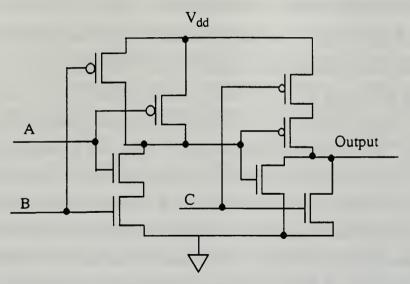

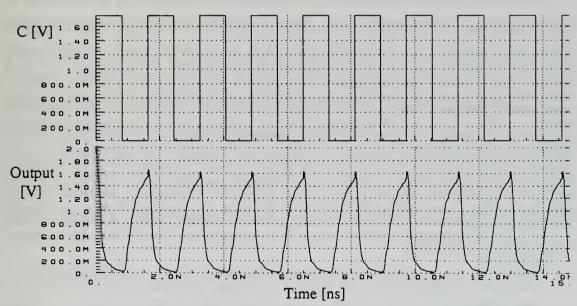

| 3.30 | Input-Output Waveforms of CGaAs TPDL XNOR Gate            | 60 |

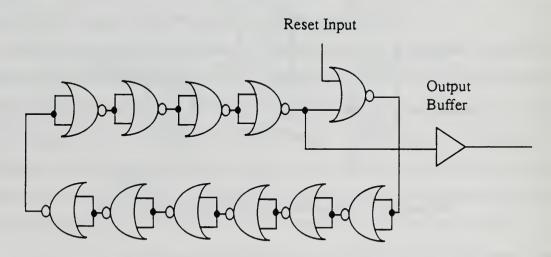

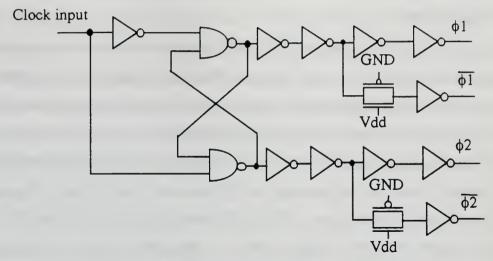

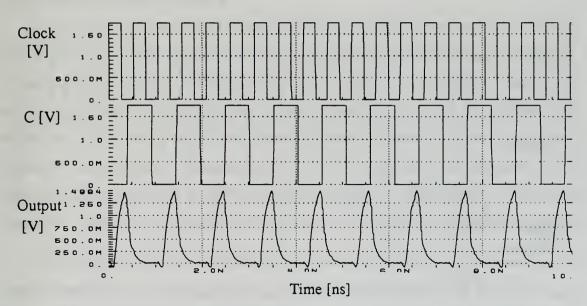

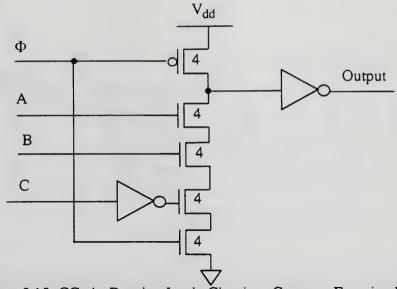

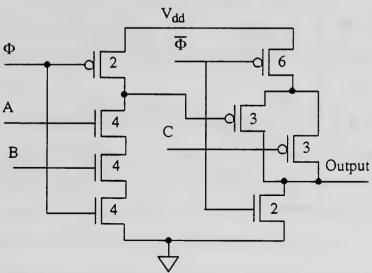

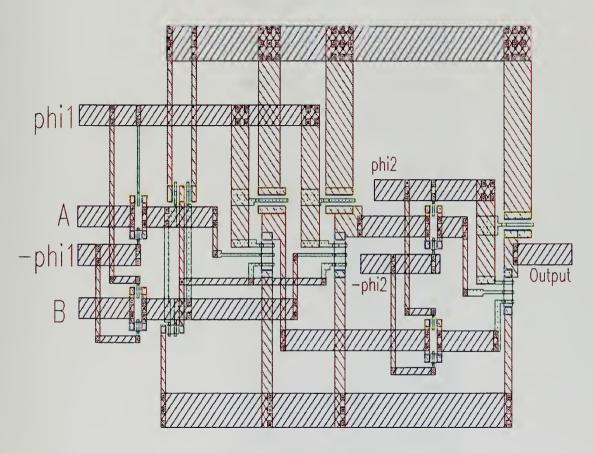

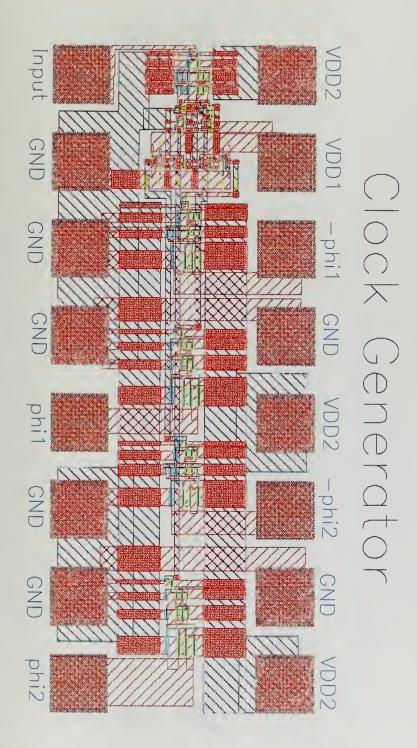

| 3.31 | Logic Diagram of Two-Phase Clock Generator                | 62 |

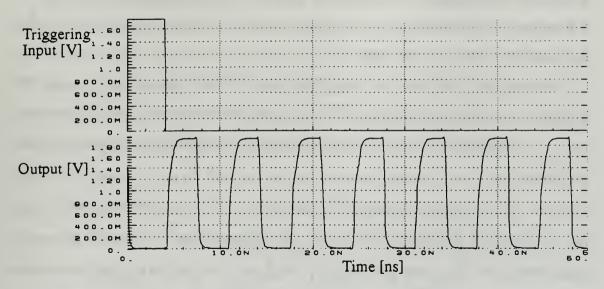

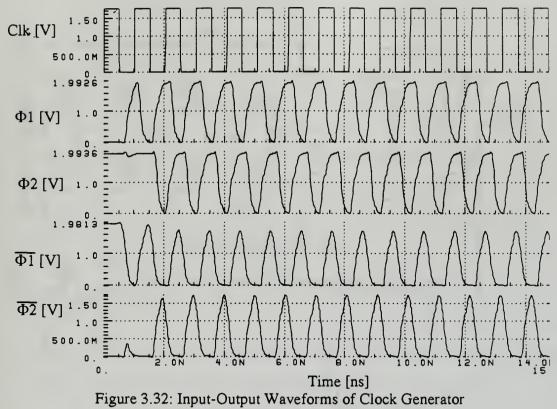

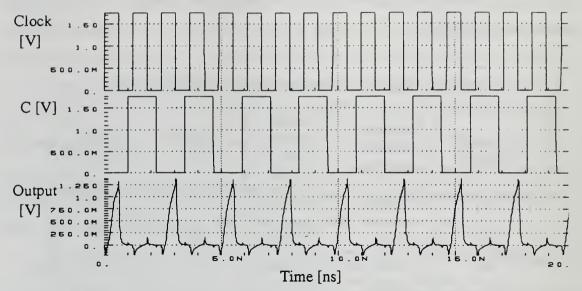

| 3.32 | Input-Output Waveforms of Clock Generator                 | 63 |

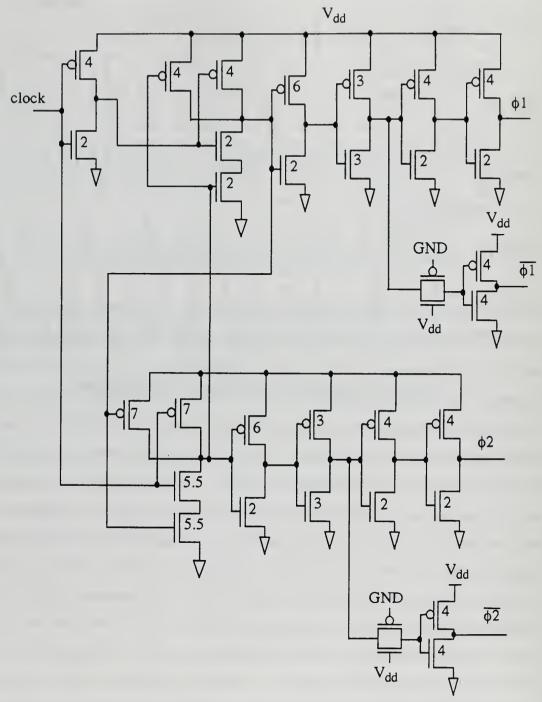

| 3.33 | Circuit Diagram of Two-Phase Clock Generator              | 64 |

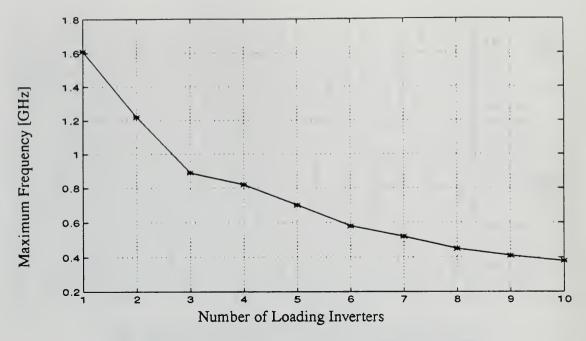

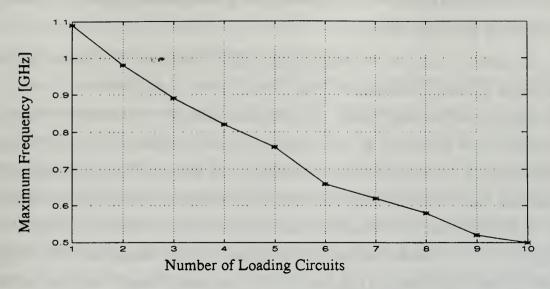

| 3.34 | Loading Effects on Clock Generator                        | 65 |

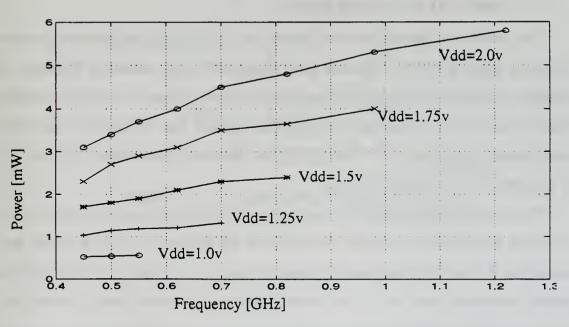

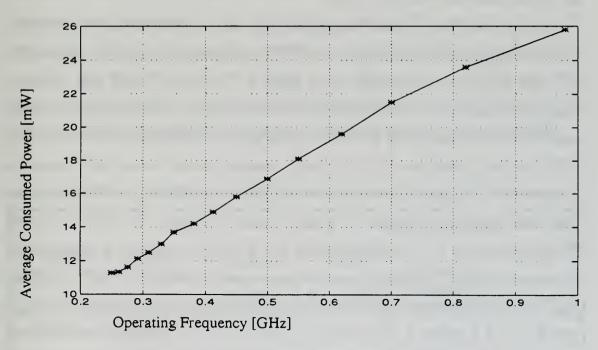

| 3.35 | Power Consumption of Clock Generator                      | 65 |

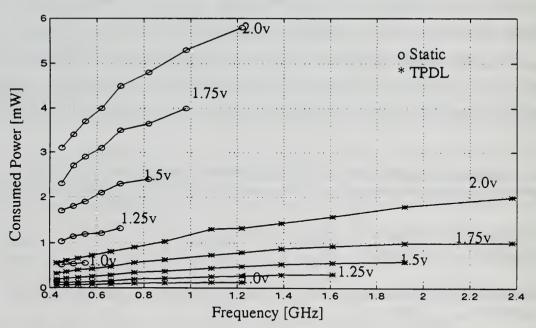

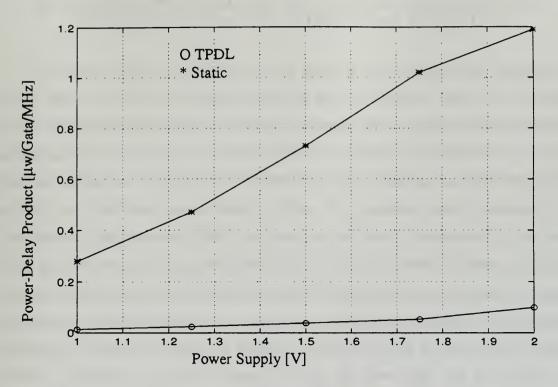

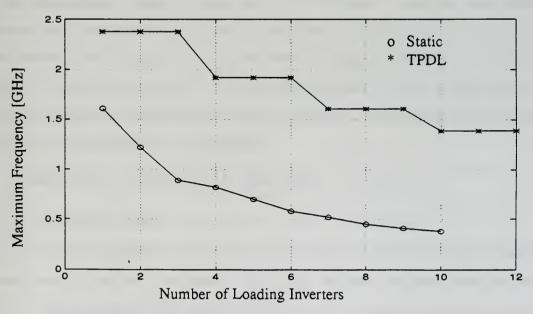

| 3.36 | CGaAs Static and TPDL NAND Gate Power Consumption         | 68 |

| 3.37 | CGaAs Static and TPDL NAND Gate Power-Delay Product                  | 69 |

|------|----------------------------------------------------------------------|----|

| 3.38 | Loading Effects on CGaAs Static and TPDL NAND Gates                  | 69 |

| 4.1  | CGaAs Static D-Latch Circuit                                         | 72 |

| 4.2  | Input-Output Waveform of CGaAs Static D-Latch                        | 73 |

| 4.3  | CGaAs Static Negative-Edge Triggered D Flip Flop                     | 74 |

| 4.4  | Input-Output Waveforms of CGaAs Static D Flip Flop                   | 74 |

| 4.5  | CGaAs Static Divide-By-Two Circuit                                   | 75 |

| 4.6  | Input-Output Waveform of CGaAs Static Divide-By-Two Circuit          | 75 |

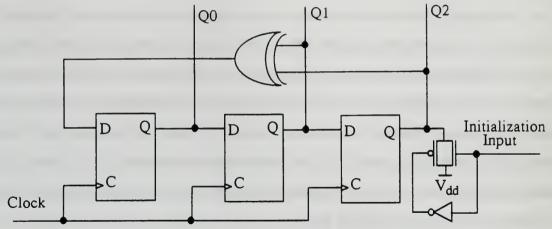

| 4.7  | CGaAs Static 3-Bit LFSR Circuit                                      | 78 |

| 4.8  | Input-Output Waveforms of CGaAs Static 3-Bit LFSR                    | 78 |

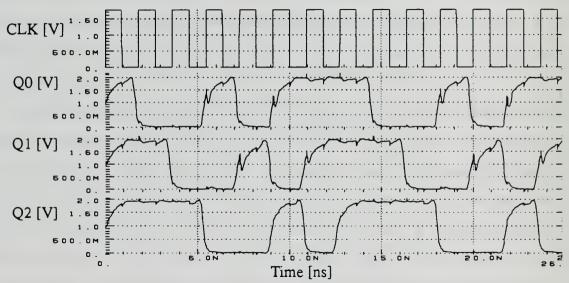

| 4.9  | CGaAs Static 4-Bit LFSR Circuit                                      | 80 |

| 4.10 | Input-Output Waveforms of CGaAs Static 4-Bit LFSR                    | 80 |

| 4.11 | CGaAs Static 4-Bit LFSR Power Consumption                            | 81 |

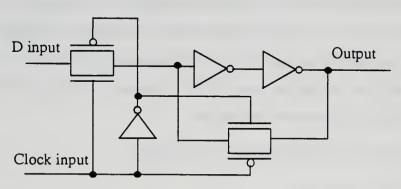

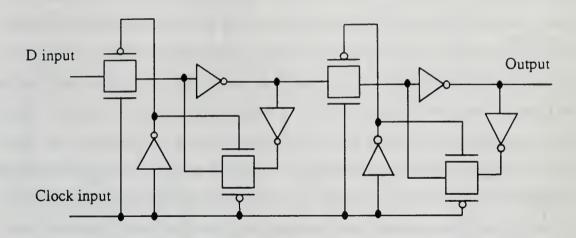

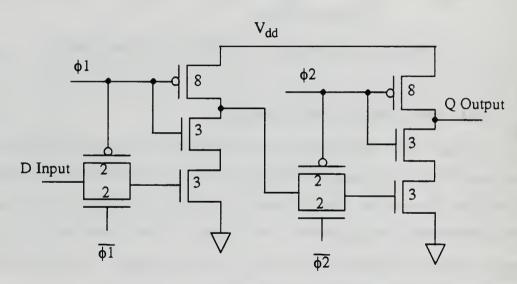

| 4.12 | CGaAs TPDL D Flip Flop Circuit                                       | 82 |

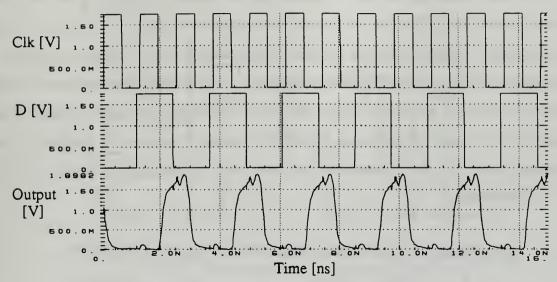

| 4.13 | Input-Output Waveform of CGaAs TPDL D Flip Flop                      | 83 |

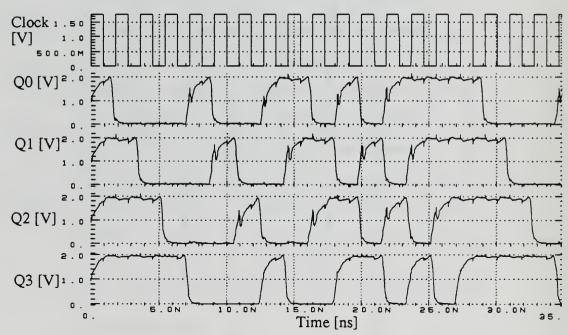

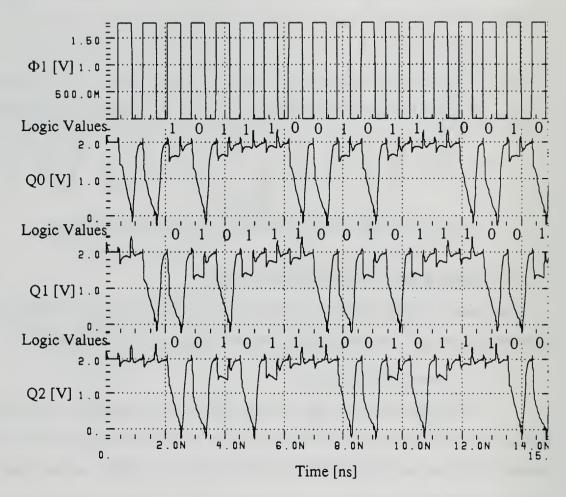

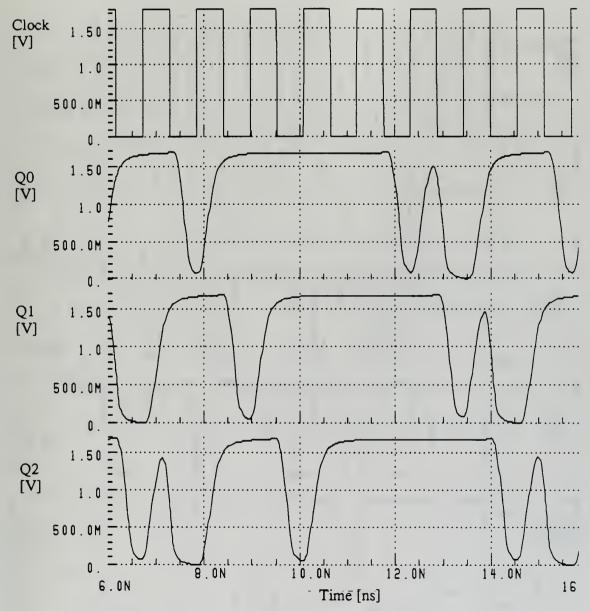

| 4.14 | Input-Output Waveform for CGaAs 3-Bit LFSR                           | 84 |

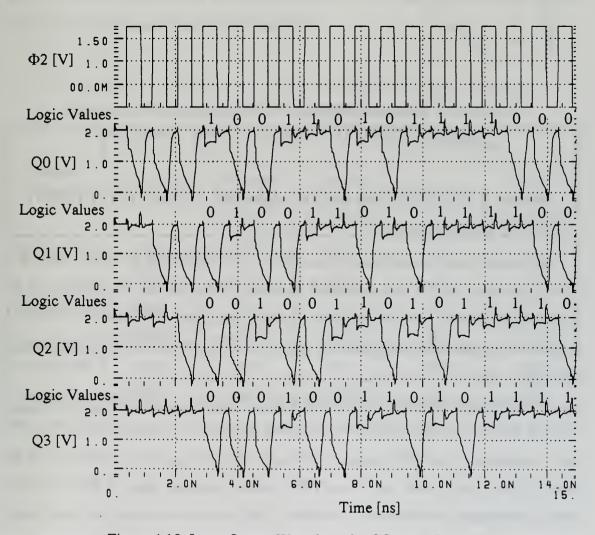

| 4.15 | Input-Output Waveform for CGaAs 4-Bit LFSR                           | 85 |

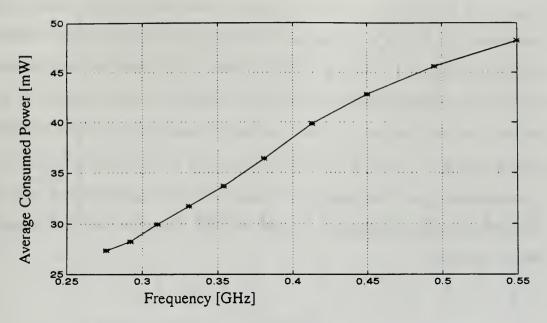

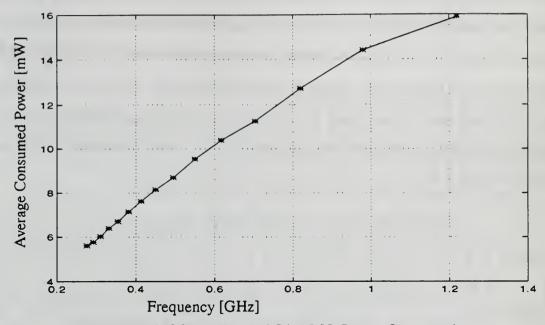

| 4.16 | CGaAs TPDL 4-Bit LFSR Power Consumption                              | 86 |

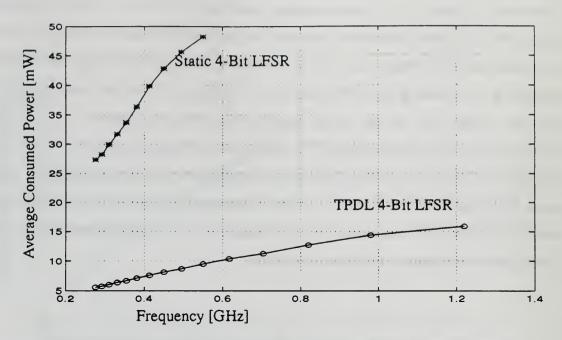

| 4.17 | CGaAs TPDL and Static 4-Bit LFSR Power Consumption                   | 88 |

| 5.1  | CGaAs Static Logic Circuit to Generate Function F1                   | 92 |

| 5.2  | Input-Output Waveform of CGaAs Static F <sub>1</sub> Generator       | 92 |

| 5.3  | CGaAs Static Logic Circuit to Generate Function F2                   | 93 |

| 5.4  | Input-Output Waveform of CGaAs Static F <sub>2</sub> Generator       | 93 |

| 5.5  | CGaAs Static Logic Circuit to Generate Function F3                   | 94 |

| 5.6  | Input-Output Waveform of CGaAs Static F <sub>3</sub> Generator       | 94 |

| 5.7  | CGaAs Static Logic Circuit to Generate Function F4                   | 95 |

| 5.8  | Input-Output Waveform of CGaAs Static F <sub>4</sub> Generator       | 95 |

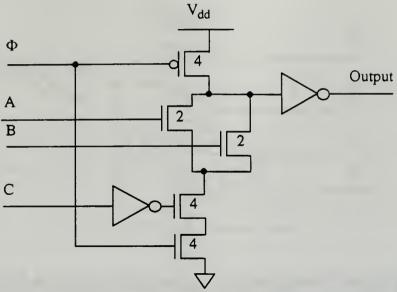

| 5.9  | CGaAs Domino Logic Circuit to Generate Function F1                   | 99 |

| 5.10 | Input-Output Waveform of CGaAs Domino Logic F <sub>1</sub> Generator | 99 |

| 5.11 | CGaAs Domino Logic Circuit to Generate Function F2                       | 100 |

|------|--------------------------------------------------------------------------|-----|

| 5.12 | Input-Output Waveform of CGaAs Domino Logic F2 Generator                 | 100 |

| 5.13 | CGaAs Domino Logic Circuit to Generate Function F3                       | 101 |

| 5.14 | Input-Output Waveform of CGaAs Domino Logic F <sub>3</sub> Generator     | 101 |

| 5.15 | CGaAs Domino Logic Circuit to Generate Function F4                       | 102 |

| 5.16 | Input-Output Waveform of CGaAs Domino Logic F <sub>4</sub> Generator     | 102 |

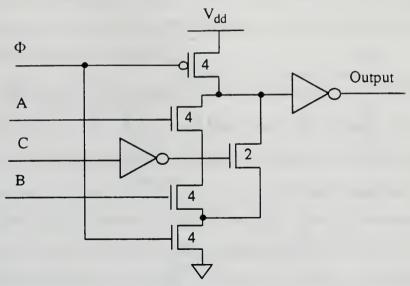

| 5.17 | CGaAs N-P Domino Logic Circuit to Generate Function F1                   | 105 |

| 5.18 | Input-Output Waveform of CGaAs N-P Domino F <sub>1</sub> Generator       | 106 |

| 5.19 | CGaAs N-P Domino Logic Circuit to Generate Function F2                   | 106 |

| 5.20 | Input-Output Waveform of CGaAs N-P Domino Logic F <sub>2</sub> Generator | 107 |

| 5.21 | CGaAs N-P Domino Logic Circuit to Generate Function F3                   | 107 |

| 5.22 | Input-Output Waveform of CGaAs N-P Domino Logic F <sub>3</sub> Generator | 108 |

| 5.23 | CGaAs N-P Domino Logic Circuit to Generate Function F4                   | 108 |

| 5.24 | Input-Output Waveform of CGaAs N-P Domino Logic F <sub>4</sub> Generator | 109 |

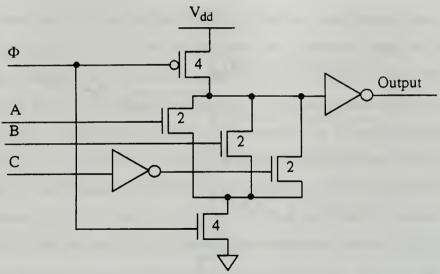

| 5.25 | CGaAs TPDL Circuit to Generate Function F1                               | 112 |

| 5.26 | Input-Output Waveform of CGaAs TPDL F <sub>1</sub> Generator             | 112 |

| 5.27 | CGaAs TPDL Schematic Circuit To Generate Function F2                     | 113 |

| 5.28 | Input-Output Waveform of CGaAs TPDL F <sub>2</sub> Function Generator    | 113 |

| 5.29 | CGaAs TPDL Logic Circuit to Generate Function F3                         | 114 |

| 5.30 | Input-Output Waveform of CGaAs TPDL F <sub>3</sub> Function Generator    | 114 |

| 5.31 | CGaAs TPDL Logic Circuit to Generate Function F4                         | 115 |

| 5.32 | Input-Output Waveform of CGaAs TPDL F <sub>4</sub> Function Generator    | 115 |

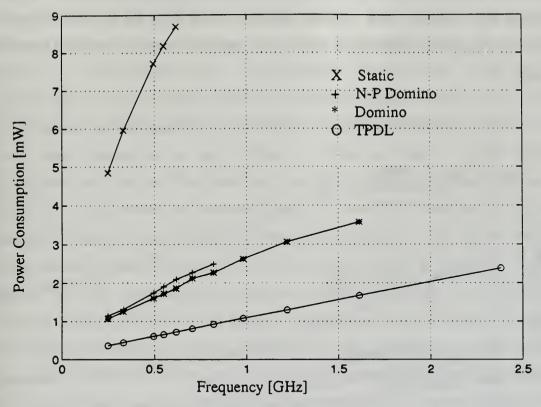

| 5.33 | Power Consumption of Logic Circuits Implementing Function F1             | 119 |

| 5.34 | Loading Effects on the Logic Families                                    | 120 |

| 5.35 | Maximum Operating Frequency of Logic Families                            | 122 |

| 5.36 | Power Consumption of Logic Families                                      | 122 |

| 6.1  | CGaAs 4-Bit Blocked CLA Logic Diagram                                    | 127 |

| 6.2  | Input-Output Waveforms of CGaAs 4-Bit Static CLA                         | 130 |

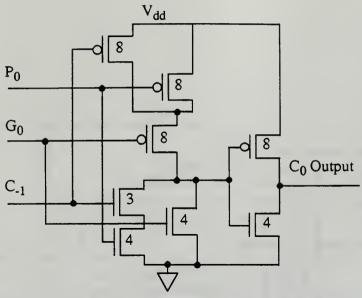

| 6.3  | CGaAs Static Circuit for Generating the Function C0                      | 131 |

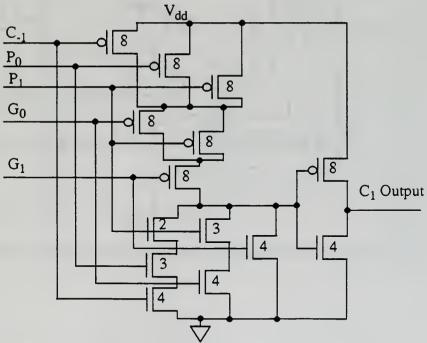

| 6.4  | CGaAs Static Circuit for Generating the Function C1           | 131 |

|------|---------------------------------------------------------------|-----|

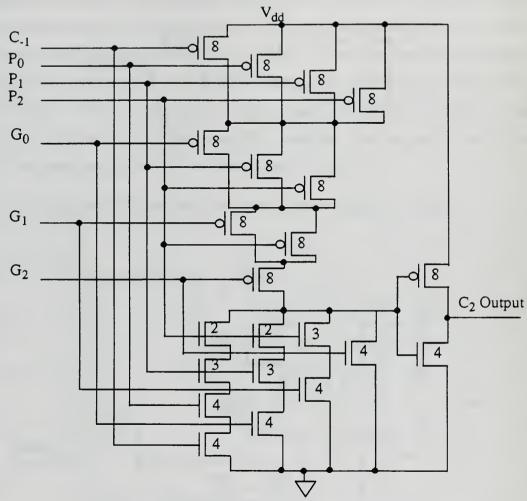

| 6.5  | CGaAs Static Circuit for Generating the Function C2           | 132 |

| 6.6  | CGaAs Static Circuit for Generating the Function P*           |     |

| 6.7  | CGaAs Pipelined Static 4-Bit CLA Logic Diagram                | 134 |

| 6.8  | Input-Output Waveforms of CGaAs Pipelined Static 4-Bit CLA    | 135 |

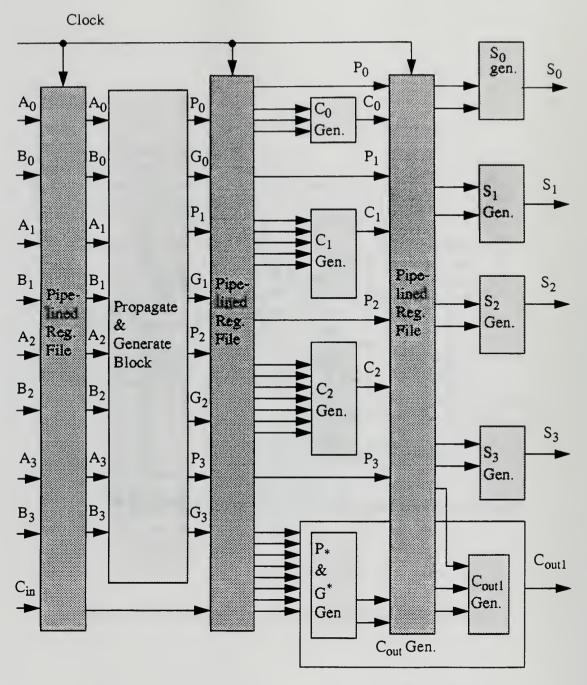

| 6.9  | CGaAs TPDL 4-Bit CLA Logic Diagram                            | 138 |

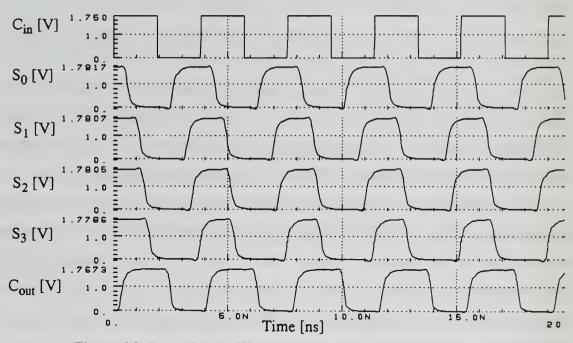

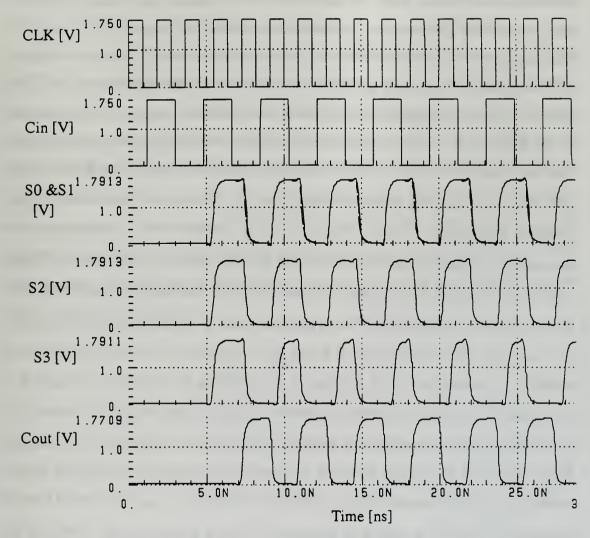

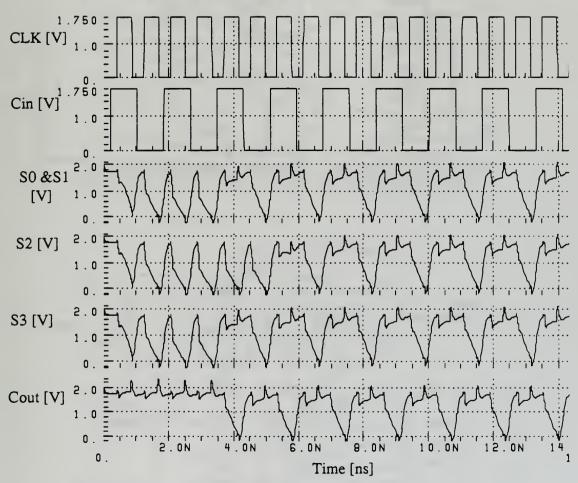

| 6.10 | Input-Output Waveforms of CGaAs TPDL 4-Bit CLA                | 139 |

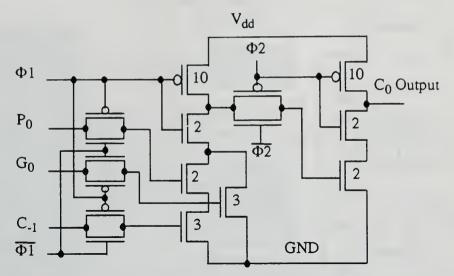

| 6.11 | CGaAs TPDL Circuit for Generating Function C0                 | 140 |

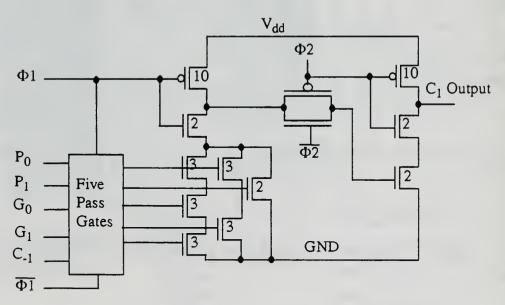

| 6.12 | CGaAs TPDL Circuit for Generating Function C1                 | 140 |

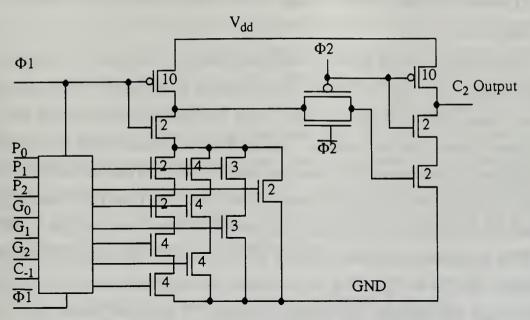

| 6.13 | CGaAs TPDL Circuit for Generating Function C2                 | 141 |

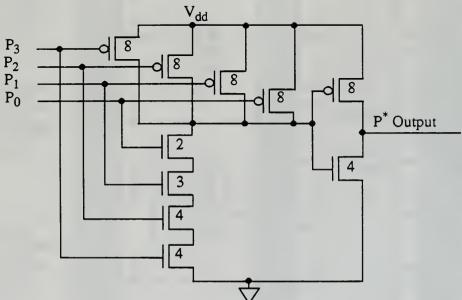

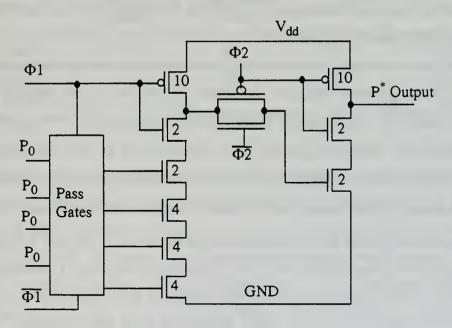

| 6.14 | CGaAs TPDL Circuit for Generating Function P*                 | 141 |

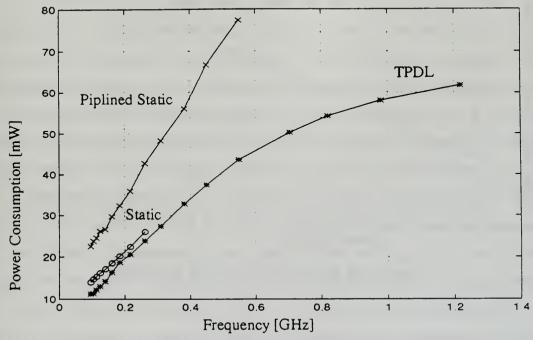

| 6.15 | Power Consumption of 4-Bit CLAs                               | 145 |

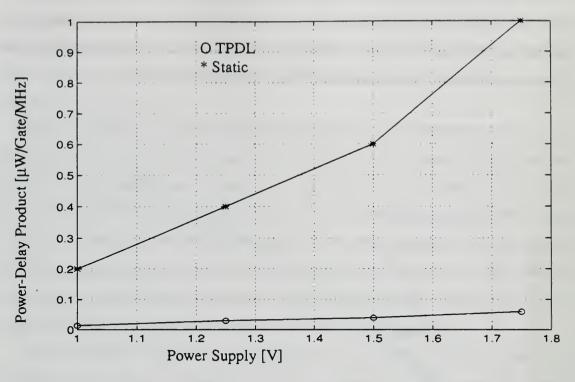

| 6.16 | Power-Delay Product of 4-Bit CLAs                             | 146 |

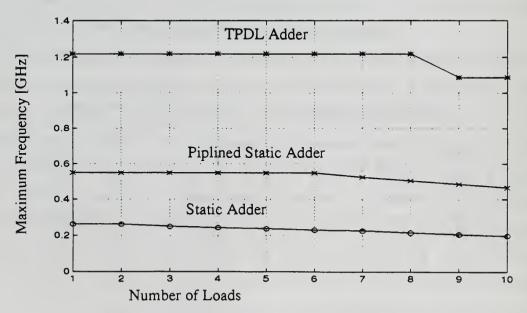

| 6.17 | Loading Effects on CGaAs 4-Bit CLAs                           | 146 |

| 7.1  | Logic Diagram of Static Logic Function F1 Generator           |     |

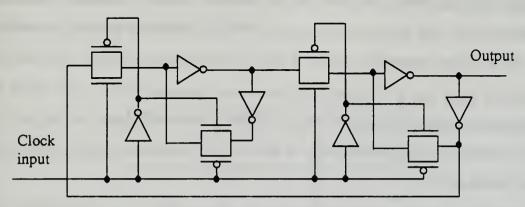

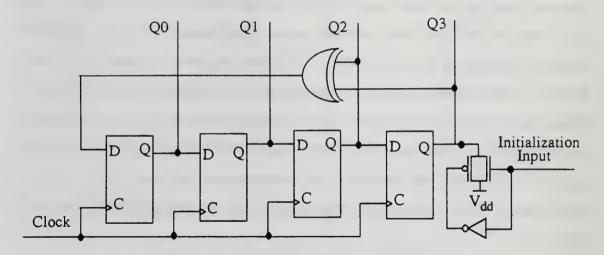

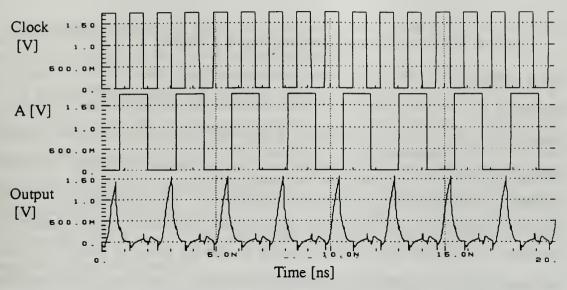

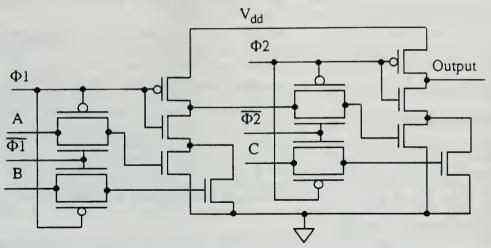

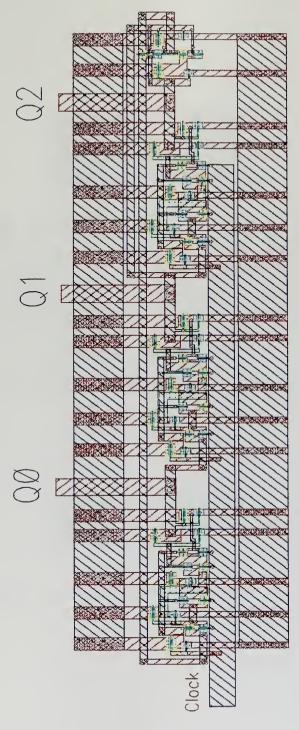

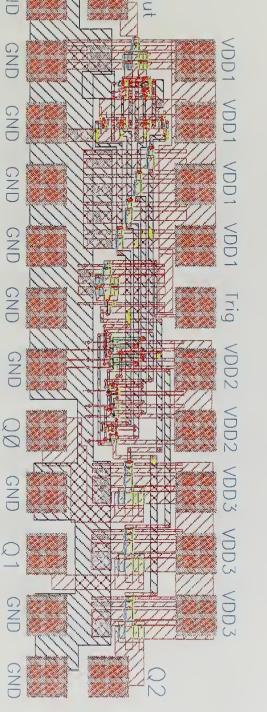

| 7.2  | Logic Diagram of TPDL 3-Bit LFSR                              | 151 |

| 7.3  | Logic Diagram of TPDL Logic Function F1 Generator             | 152 |

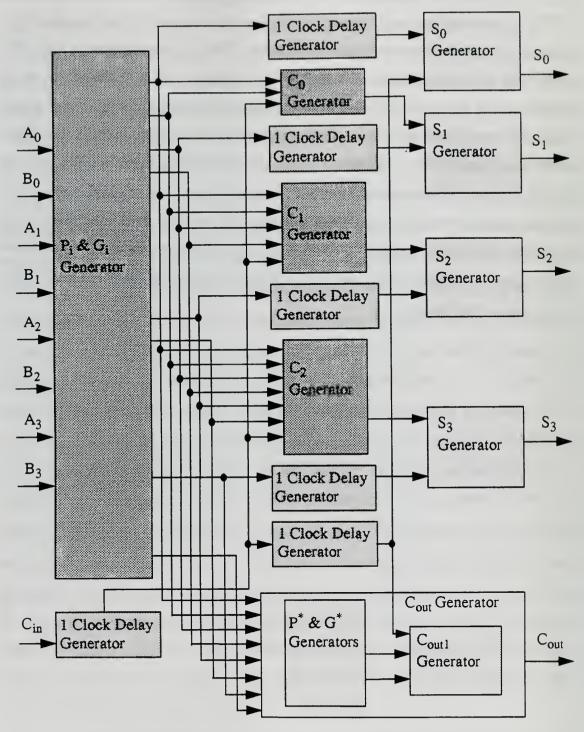

| 7.4  | Logic Diagram of TPDL 4-Bit CLA                               | 153 |

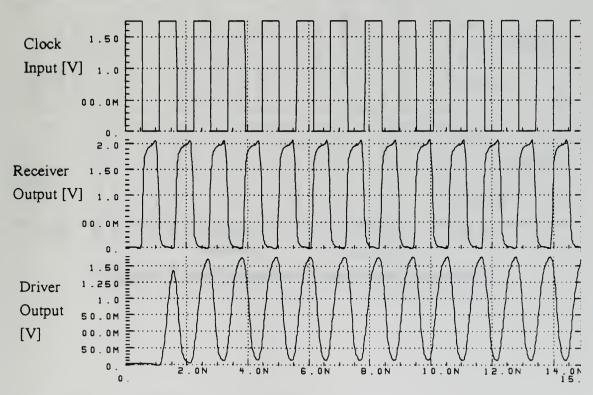

| 7.5  | Input-Output Waveforms of Input Receiver and Output Driver IC | 153 |

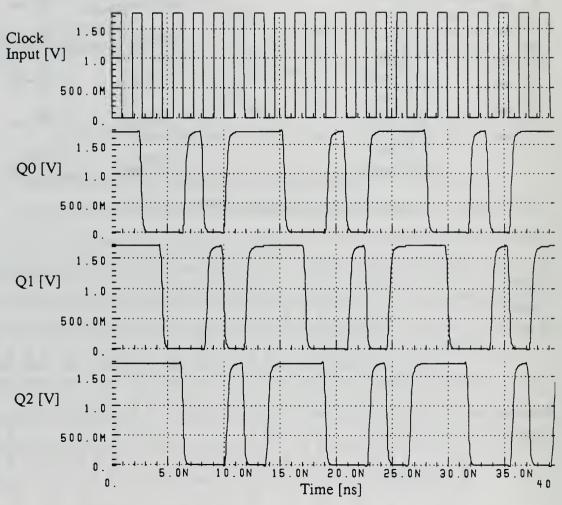

| 7.6  | Input-Output Waveforms of Static 3-Bit LFSR IC                | 154 |

| 7.7  | Input-Output Waveforms of Static Function F1 IC               | 155 |

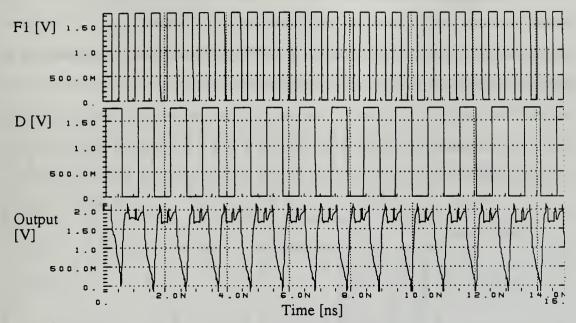

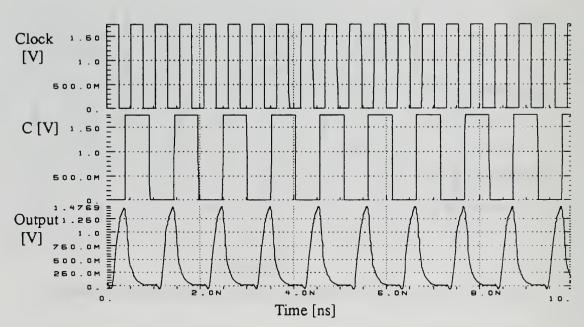

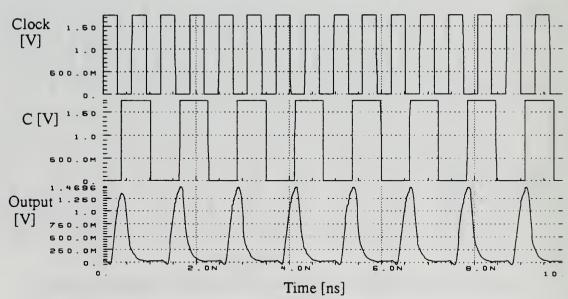

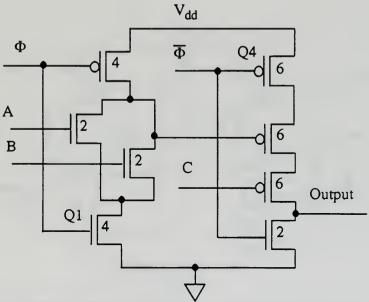

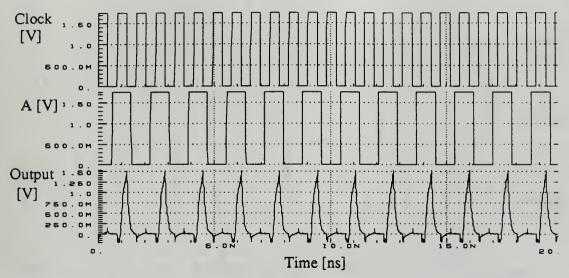

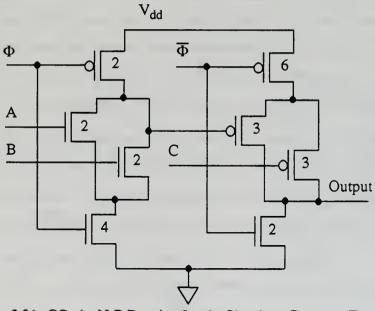

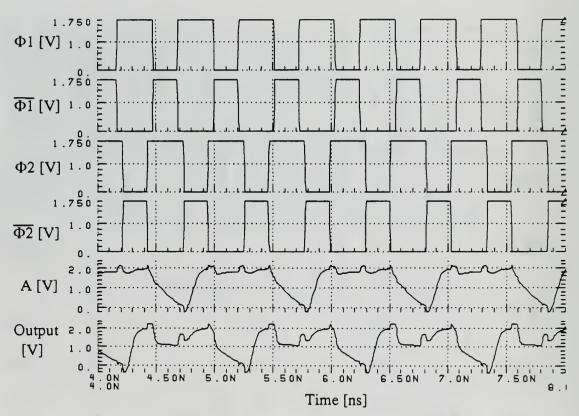

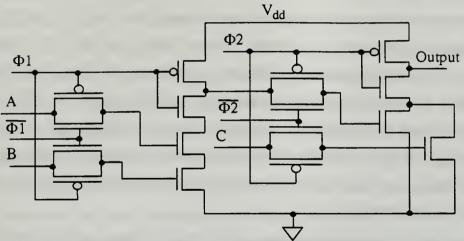

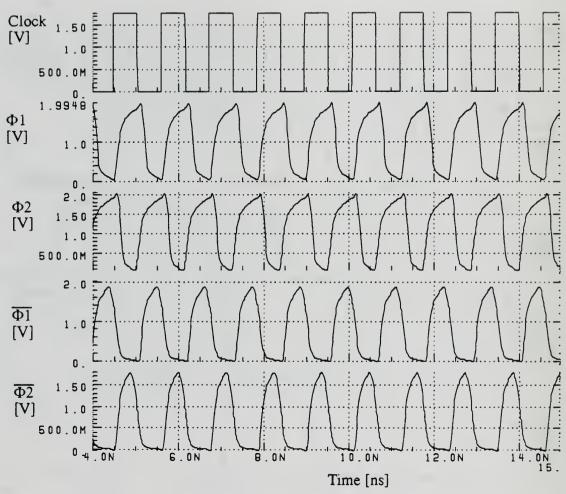

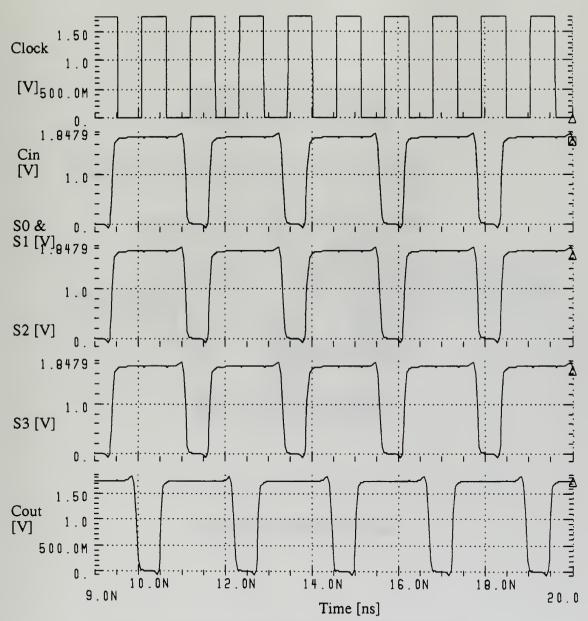

| 7.8  | Input-Output Waveforms of Two-Phase Clock Generator IC        | 156 |

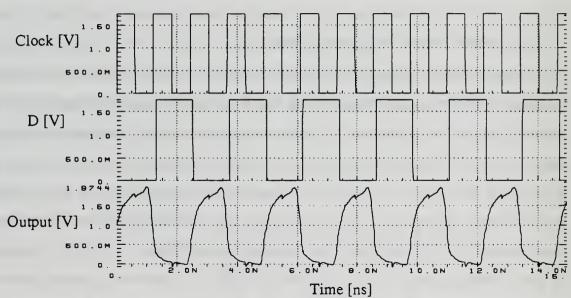

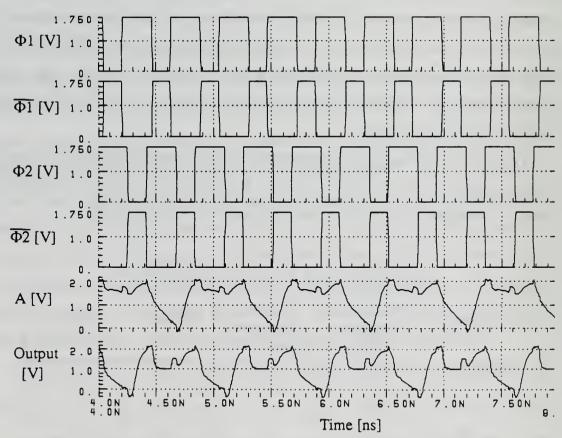

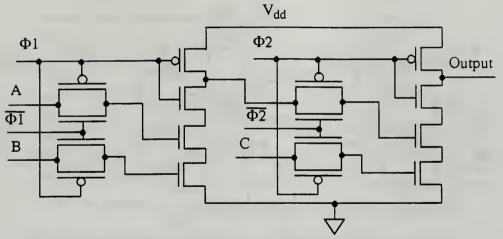

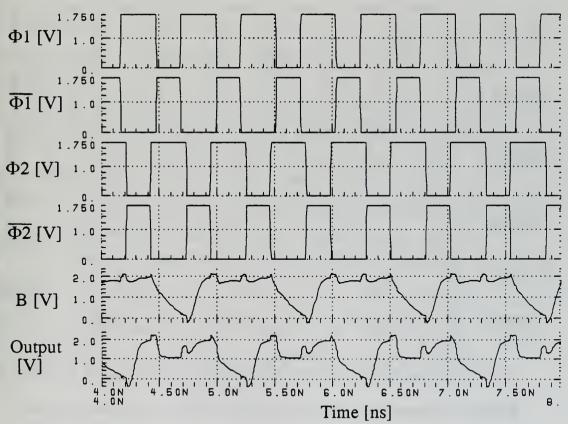

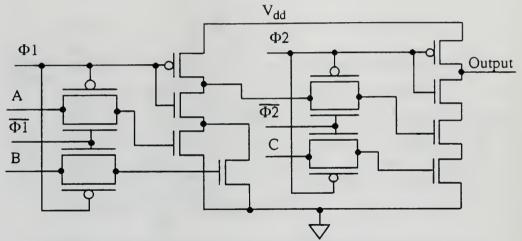

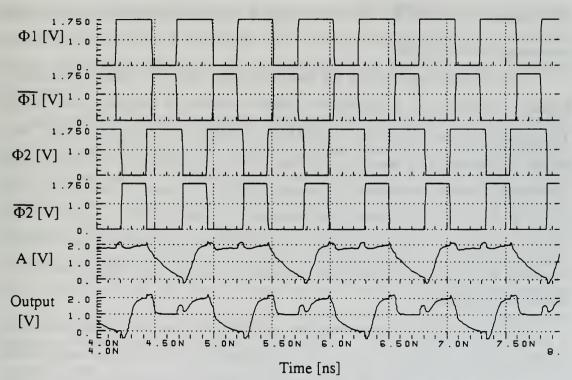

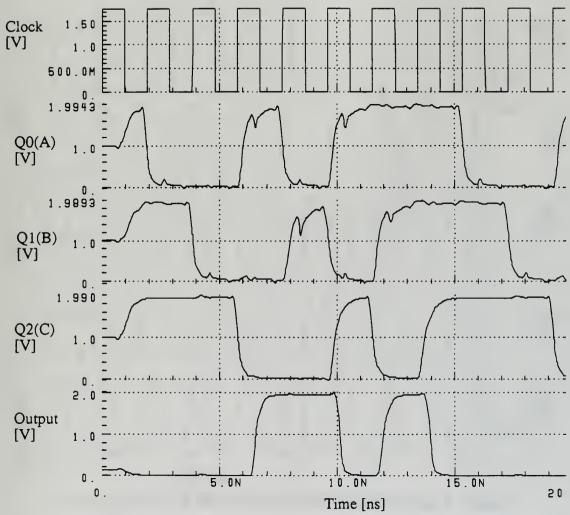

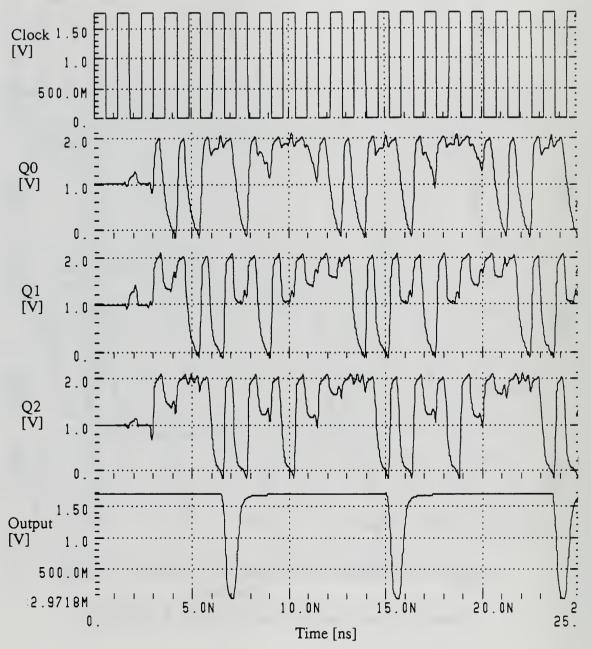

| 7.9  | Input-Output Waveforms of TPDL 3-Bit LFSR IC                  | 157 |

| 7.10 | Input-Output Waveforms of TPDL Function F <sub>1</sub> IC     | 158 |

| 7.11 | Input-Output Waveforms of TPDL 4-Bit CLA                      | 159 |

| 7.12 | Static XOR Gate                                               | 160 |

| 7.13 | TPDL XOR Gate                                                 | 161 |

| 7.14 | Static 3-Bit LFSR                                             | 162 |

| 7.15 | Static Function F1 Generator                                  | 163 |

| 7.16 | Two-Phase Clock Generator  | 164 |

|------|----------------------------|-----|

| 7.17 | TPDL 3-Bit LFSR            | 165 |

| 7.18 | TPDL Function F1 Generator | 166 |

| 7 19 | TPDL 4-Bit CLA             | 167 |

### LIST OF TABLES

| 3.1 | CGaAs Static and TPDL Combinational Circuit Performance | 67  |

|-----|---------------------------------------------------------|-----|

| 4.1 | 3-Bit LFSR Generated Sequence                           | 77  |

| 4.2 | 4-Bit LFSR Generated Sequence                           | 79  |

| 4.3 | CGaAs Static and TPDL Sequential Circuit Performance    | 87  |

| 5.1 | CGaAs Static Logic Circuit Performance                  | 91  |

| 5.2 | CGaAs Domino Logic Circuit Performance                  | 98  |

| 5.3 | CGaAs N-P Domino Logic Circuit Performance              | 105 |

| 5.4 | CGaAs TPDL Circuit Performance                          | 111 |

| 5.5 | Comparison of CGaAs Logic Families                      | 118 |

| 6.1 | Comparison of CGaAs 4-Bit CLA Designs                   | 143 |

| 6.2 | Performances of CGaAs 4-Bit CLA Designs                 | 145 |

### LIST OF SYMBOLS AND ACRONYMS

BFL Buffered FET Logic

CCL Capacitor-Coupled FET Logic

CDFL Capacitor-Diode FET Logic

CGaAs Complementary Gallium Arsenide

CLA Carry Lookahead Adder

CMOS Complementary Metal Oxide Semiconductor

DCFL Directly-Coupled FET Logic

DFET Depletion-Mode FIeld Effect Transistor

ECL Emitter Coupled Logic

EFET Enhancement-Mode Field Effect Transistor

FET Field Effect Transistor

GaAs Gallium Arsenide

HFET Hetrostructure Field Effect Transistor

HIGFET Hetrostructure Isolated Gate Field Effect Transistor

IC Integrated Circuit

JFET Junction Field Effect Transistor

LSI Large Scale of Integration

MESFET Metal Semiconductor Field Effect Transistor

MODFET Modulation Doped Field Effect Transistor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MSI Medium Scale of Integration SBFL Super-Buffer FET Logic SCFL Source-Coupled FET Logic SDFL Schottky Diode FET Logic SSI Small Scale of Integration **TPDL** Two-Phase Dynamic Logic  $V_{DS}$ Drain to Source Voltage  $V_{GS}$ Gate to Source Voltage

VLSI Very Large Scale of Integration

VTN Threshold Voltage of PFET

VTP Threshold Voltage of PFET

Wn NFET Gate Width Wp PFET Gate Width

### **ACKNOWLEDGEMENTS**

The work presented in this dissertation is the culmination of support from many institutions and people. First of all, I am indebted to the Egyptian Ministry of Defense for financially supporting my scholarship.

I am especially fortunate to have been able to work with one of the most dedicated, hard working and patient men I have known, my advisor, Douglas Fouts. His ability to keep me focussed and willingness to do whatever was necessary was instrumental in my completion of this document. I am grateful for his guidance, insight and friendship.

I gratefully acknowledge the support of our sponsors, David Foster and Motorola Semiconductor, the National Security Agency, and LCDR Bill Schneider and the U.S. Naval Space and Warfare Systems Command. Without their technical and financial support, this research would not have been possible.

I would like to thank my committee members, Professors Sherif Michael, Hersch Loomis, Yutaka Kanayama and Rick Haward for their patience, thoroughness and perseverance.

Finally, I would like to acknowledge the omnipresent support, without which, I could never have attained my goal. That support came from my father, my mother, my loving wife Wafaa and my family, Walaa, Mohamed and Heba. Words cannot express the gratitude I have for their patience, support and love.

### I. INTRODUCTION

The objective of the research documented in this dissertation is to investigate different static and dynamic logic families that can be implemented in a GaAs Complementary Hetrostructure Isolated Gate (CHIGFET) process. Key points in the analysis of different designs are to maximize speed and minimize both consumed power and layout area. In addition, the logic circuits should be suitable for VLSI implementations. The dynamic logic families discussed in this dissertation include Domino logic, N-P Domino logic and Two-Phase Dynamic Logic (TPDL).

In this chapter, the history of the development of GaAs is introduced in Section A. A comparison between the electrical properties of GaAs and silicon is discussed in Section B. Section C discusses different GaAs devices. Section D discusses static logic families, while Section E explains well-known dynamic logic families. Section F outlines the rest of the dissertation.

### A. HISTORICAL REVIEW OF GALLIUM ARSENIDE (GaAs)

Gallium Arsenide (GaAs) is a compound semiconductor that has been used since the 1960's for microwave amplifiers and optical-electronic devices. In the opto-electronic area, GaAs is used for light emitting diodes, solid state lasers, and optical sensors. GaAs transistors, both FET (Field Effect Transistor) and HBT (Hetrostructure Bipolar junction Transistor), are used for digital integrated circuits, primarily when the application requires very high speed and the delay and power requirements of silicon CMOS or bipolar ICs are too high. The high-frequency performance of GaAs digital ICs is excellent. The high electron velocity at moderate electric fields improves the high-frequency performance of GaAs transistors. The fast switching capabilities of these devices is based on their low internal capacitances and on their high electron velocity.

The use of GaAs for digital applications began in 1974 with some relatively high-power, high-speed SSI divider circuits and has developed over the years into a well-established LSI technology, with some inroads into the VLSI arena. Initially, GaAs

integrated circuits appeared in digital fiber-optic communication systems [1, 2, 3, 4, 5]. However, the demand for faster computers requires faster logic circuits. The feasibility of using GaAs technology to build the next generation of computers has been demonstrated. Experimental GaAs RAMs, parallel multipliers, microprocessors and other computer circuits with a cycle time of a few nanoseconds or less have been reported [6, 7, 8, 9].

# B. COMPARISON BETWEEN GALLIUM ARSENIDE (GaAs) AND SILICON (SI) ELECTRICAL PROPERTIES

### 1. Electron Mobility

The resistivity of a doped semiconductor is dependent upon the doping density (the number of charge carriers present within the material) and also upon the ease with which these carriers can move under the application of an electric field. This later property is known as the carrier mobility, which is defined as the ratio of the carrier velocity to the electric field strength. The primary advantage of GaAs over Si is that the electron mobility of GaAs is approximately five times that of Si, which offers a higher speed of operation than that achievable using Si devices [3, 10, 11, 12, 13, 14]. The disadvantage of GaAs is the relatively high power dissipation per logic gate during low-speed operation, small logic swing and correspondingly narrow noise margins. Low logic density, as a result of layout restrictions and low manufacturing yield, are also disadvantages of GaAs logic.

Digital IC technologies are usually compared using a "power-delay product" parameter which is calculated by multiplying the logic gate delay by the power dissipated per gate. A high power delay product implies that either the gate power dissipation is high (limiting the integration density and increasing power consumption), or that the gate delay is high (limiting the speed performance of the technology). GaAs has a power-delay product advantage over Si in the vicinity of four to five times, which is principally determined by the high electron mobility.

### 2. Semi-insulating Substrate

When semiconductor devices are fabricated together on an IC, it is important that any interaction between them which might negatively affect the performance of the complete circuit be kept to a minimum. Thus, the integrated components must be electrically isolated from each other. The resistivity of a semiconductor is dependent on the doping level. Silicon technologies generally use a doped N-type or P-type substrate with devices fabricated in oppositely doped "wells" to provide sufficient device isolation at relatively small separations. In comparison, the intrinsic resistivity of GaAs is several orders of magnitude higher, falling into the "semi-insulating" range [13, 15, 16]. This property allows GaAs devices to be fabricated in wells in un-doped substrate while still maintaining good isolation. The principal advantage of this is the reduced parasitic capacitance in GaAs ICs compared to that of silicon ICs [12, 13].

### 3. Radiation Hardness

The immunity of an IC to damage from exposure to radiation is important for many applications. Military, space, and nuclear systems have certain requirements for radiation hardness. Other applications may also be affected if the IC is sensitive to radiation naturally occurring radiation from sources in the environment or packaging. GaAs has an advantage over silicon, depending on the type of radiation concerned. Radiation can ionize the atoms in a material. The total ionized charge produced depends on the total radiation dose. GaAs FETs have higher immunity than silicon ICs to total dose effects from ionizing radiation and only undergo a small change in their operating parameters [17]. GaAs has a high density of energy states at the surface which absorbs charge produced by radiation and thus minimizes changes in device parameters such as threshold voltage and parasitic resistance. It also prevents large surface leakage currents from occurring. The sensitivity of device characteristics to a radiation pulse is defined as the transient radiation hardness. The resulting transient radiation current may occur in two regions, within the active device or in the substrate [18]. In GaAs ICs, the dominant effects are due to substrate current. The

wider band gap of GaAs over that of Si (excluding Silicon On Sapphire-SOS) makes it harder to generate carriers and thus the sensitivity of GaAs to transient radiation is relatively low, provided that high quality, un-doped substrates are used.

### 4. Hole Mobility

The hole mobility of GaAs is lower than that of silicon by a factor of approximately five. Therefore, devices based upon the use of P-type GaAs will be slower than those based upon P-type silicon. Also, P-channel GaAs FETs have a higher channel resistance which degrades speed compared to silicon [13].

### 5. Other Properties

One of the major disadvantages of Complementary GaAs, compared to silicon, is the cost factor. This high cost occurs for several reasons. The biggest cause of the relatively high cost of Complementary GaAs ICs is the fact that yields are low and wafer sizes are small compared to silicon [13]. This means that there are fewer working devices per wafer over which the processing costs can be shared. The material costs are higher (GaAs crystals are difficult to grow and IC production sometimes uses gold-based metallization). In practice, this means the use of Complementary GaAs is restricted to high speed applications where high cost can be tolerated in order to obtain a degree of performance that is not available from silicon ICs.

Thermal conductivity is also an important property. High thermal conductivity is required to dissipate the heat generated by an IC during operation. GaAs has lower thermal conductivity than silicon. Thus, a GaAs IC runs hotter than a silicon IC when dissipating the same power. Also, thermal gradients across the surface of a GaAs chip are more severe. Thinning the substrate of GaAs ICs will aid in reducing this problem.

### C. GaAs DEVICES

The Gallium Arsenide transistor with a diffusion gate structure, which was first reported in 1967, yields useful gain in the low megahertz frequency band. In 1969, the

silicon field effect transistor (FET) was developed with a 1  $\mu$ m gate length. In 1971, a significant step was made when 1  $\mu$ m gate length FETs on GaAs were developed with a useful gain up to 18 GHz.

Oxide growth has been tried on GaAs surfaces for more than 20 years. The quality of oxide grown on GaAs has been poor, and a high density of surface states results at the GaAs-insulator interface. These effects make it difficult to fabricate GaAs MOSFETs. Schottky barrier MESFETs and Junction Field Effect transistors (JFET) are examples of practical GaAs FETs. In many cases, these devices are fabricated by direct implantation into a GaAs semi-insulating substrate. Both enhancement and depletion MESFETs can be fabricated and each has advantages, depending on the application. The JFET is basically a voltage controlled resistor that employs a p-n junction as a gate to control the resistance, and thus the current that flows, between two ohmic contacts. The JFET has a lower switching speed than the MESFET because of the higher input edge capacitances in a planner JFET processes. The advantage of JFETs is that complementary logic is possible because n-p and p-n junctions can be fabricated on the same wafer.

The development of advanced epitaxial growth techniques such as Molecular Beam Epitaxy (MBE) in the 1970s has enabled the fabrication of useful high quality semiconductor hetrostructures. The original concept of hetrojunction FETs (HFETs) came from experimental observation of enhanced electron mobility in modulation-doped hetrostructures. The term modulation doping has led to the name MODFET for the first generation of HFETs.

### 1. Noise in Digital Circuits

Noise in a digital circuit can be classified as either internal or external. External noise is generated outside the integrated circuit of interest, such as power supply ripple or electrostatic discharge. Internal noise is generated inside the integrated circuit of interest, such as mutual inductance and/or capacitance (cross-talk) between signal lines, inductive and resistive voltage spikes, power supply and ground leed voltage drop, interconnect

reflections, etc. A practical IC must be able to tolerate both types of noise in order to operate successfully and reliably in the intended application.

The dc noise margins are the parameters that measure the ability of a circuit to operate error-free in a noisy environment. The noise margins of digital logic circuits can be measured in many different ways. Slope = -1 noise margin, intrinsic noise margin and maximum width noise margin are examples of the methods to measure noise margin of digital circuits. The factors that influence the noise margins are the voltage gain and the symmetry of the transfer characteristics of the circuit. As the voltage gain increases, the slope of the output voltage in the transition region increases and consequently the noise margins are increased. When the transfer curve of a digital circuit is symmetric, the noise margin low is equal to the noise margin high.

The dynamic noise margin refers to the ability of a circuit to maintain a constant output when a short-duration noise pulse is present on the input. It depends on both the width and the magnitude of the input pulse. As the width of the input pulse decreases, a greater magnitude will be required to upset the output of the circuit and vise versa.

### 2. Power Dissipation in GaAs Circuits

When designing a GaAs digital circuit, the first parameters optimized are usually the noise margins. Then, the speed and the dissipated power can be optimized. GaAs digital circuits dissipate two types of power, static power and dynamic power. Static power is dissipated due to current flow from supply to ground or supply to supply during at least one logic state. Dynamic power is dissipated during switching due to the charging and discharging of the capacitive load. The total power dissipated by the circuit is the sum of both types.

### 3. Depletion-Mode Logic Circuits

N-type depletion-mode FETs (DFETs) are ON when  $V_{GS}$ = 0 and require a negative  $V_{GS}$  to cut off the flow of drain current.  $V_{DS}$  is usually kept positive all the time. Logic circuits containing only DFETs are characterized by unequal input and output voltage

levels and the need for level shifting networks. Both negative and positive signals are required, thus two power supplies are needed, leading to an increase in power dissipation and system-level design complexity. The use of two power supplies also makes this type of logic more susceptible to backgating effects. The backgating effect is the phenomenon of depleting the back side of the channel from charges when the substrate is negative with respect to the source, causing an increase in the threshold voltage which decreases the drain current and subsequently reduces the switching speed. The main advantage of DFET-only logic is the increased voltage transition which increases both the noise margin and the yield.

### 4. Enhancement/Depletion Mode Logic Circuits

This logic family requires both enhancement and depletion-mode FETs. Its main advantage over DFET-only logic is the equal input and output voltage levels. Therefore, there is no need for level shifting networks, which saves layout area. It also requires only one power supply with a value less than that of depletion-mode only logic circuits. The small logic transition provided by this type of logic leads to a higher speed and lower power dissipation compared to depletion-mode logic families. The main drawback of this family is that the small logic transition makes it sensitive to parameter variations, especially the threshold voltage. Therefore, it requires a uniformity of threshold voltage between components and between wafers.

### D. GaAs MESFET STATIC LOGIC CIRCUITS

MESFET static logic families are ratioed logic, meaning that their high and low logic levels are determined by the width and length ratios of the load and switching FETs. GaAs MESFET static logic families dissipate static power, due to the current flow from the supply voltage to ground. Therefore, their performance is tied to constant power-delay curves. The main property that distinguishes the design of GaAs FET circuits from CMOS circuits is the forward bias gate conduction that results from the Schottky barrier at the gate/channel junction of the FET. This gate conduction clamps the upper value of  $V_{GS}$  (gate to

source voltage) to about 0.7 volts, the voltage required to forward bias the Schottky barrier diode.

The design of GaAs digital logic circuits is a multidimensional problem. The circuit design problem is much more difficult than silicon MOS circuit design because there are few standards established for logic levels and supply voltages, and no preferred or obviously superior circuit topology has dominated design at the present time. The threshold voltages of both depletion and enhancement-mode FETs are different from one foundry to another, and a relatively wide variance from the mean threshold voltage is allowed. Therefore, the GaAs user must utilize a more general set of design methodologies than is necessary to complete the design of a standard NMOS or CMOS silicon IC [12].

The approach taken to optimize the design will depend on the application in which the circuit will be used. Speed and consumed power can be traded off over a range of about five to one for most circuits, without changing the threshold voltage. Speed and circuit tolerance to process variation, supply voltage or ground fluctuations, or temperature variations are also interchangeable to a degree because a circuit with a low logic transition will exhibit less delay than one that is designed with a larger logic transition and therefore is more robust in a digital system application [12]. The highest priority is assigned to the dc functionality of the circuit (noise margin and delay) over the expected range of process parameters and operating temperatures. Without satisfying this prerequisite, the maximum operating speed of the designed circuit has no significance. The following sections describe the relevant design details for the most commonly used static logic gate families.

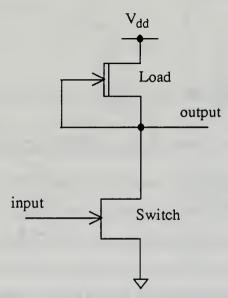

### 1. Directly-Coupled FET Logic (DCFL)

DCFL has the lowest power consumption and highest logic function density. It is also the simplest form of the static logic families. It uses an E-MESFET for the switch device and D-MESFET for the load device. Figure 1.1 shows a DCFL inverter whose output logic high voltage will move towards  $V_{DD}$  when the switch is off, but be clamped by the forward biased gate-channel Schottky diode at the input of the next switch device. This limits the

output high voltage to about 0.7 V ( $V_{OH} = 0.7$  V) and reduces the noise margins of this family. The key point for correct operation is to decrease the output low voltage ( $V_{OL}$ ) below the threshold voltage of the E-MESFET switch device. Design of the inverter involves scaling the device gate widths and lengths so as to get an acceptable logic low and a reasonable noise margin [2, 19, 20].

Due to its low noise margin, only basic logic gates can be reliably fabricated. NAND gates are not recommended in this logic family since they use two series E-MESFETs which degrades the noise margin.

Figure 1.1: Directly-Coupled FET Logic (DCFL) Inverter

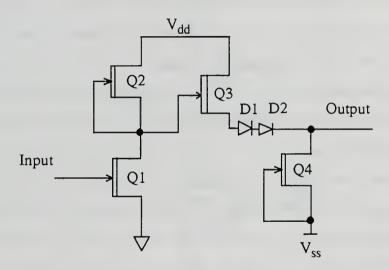

### 2. Buffered FET Logic (BFL)

DCFL circuits are difficult to make due to the need to integrate enhancement and depletion mode MESFETs. The BFL family uses only D-MESFETs, Figure 1.2 shows a BFL inverter. The use of the D-MESFET as a switch device requires that the input voltage transition must be negative (below the threshold voltage) to turn the device off. Because the output of the inverter can not fall below zero, a level shifting stage (D1, D2, Q4) is used to shift the output negatively which requires another power supply  $(V_{ss})$ . Q3 is a source-

follower used to increase the drive capability and increase the speed of this logic family [21]. Unbuffered logic is derived from BFL by eliminating the source follower Q3 and connecting the drain of Q1 directly to D1. This can be done when the drive capability of BFL is not needed.

In comparison to DCFL, BFL has a much higher power dissipation due to the extra level shifting stage and the use of two voltage rails. The buffering circuit provides a lower propagation delay and higher drive capability. Also, fabrication of BFL circuits is easier than that of DCFL because it uses only D-MESFETs and has much better tolerance to variations in MESFET characteristics.

Figure 1.2: Buffered FET Logic (BFL) Inverter

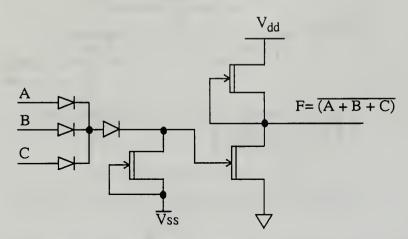

### 3. Schottky Diode FET Logic (SDFL)

When the power dissipation of BFL is too high, the level shifting stage can be moved from the output to the input of the gate. The diodes can be used as switching elements rather than using them only for level shifting purposes, resulting in a new logic family called SDFL. The diodes have low capacitance, low series resistance and there is no minority carrier charge storage problems as with p-n junction diodes. Therefore, if used for switching, a saving in area is also possible. Figure 1.3 shows the circuit of a three inputs

SDFL NOR gate. In this family, the output of the level shifting stage will drive only one logic gate, less drive capability is required, much smaller devices can be used and correspondingly the power dissipation is reduced [22, 23, 24, 25].

Figure 1.3: Three-input Schottky Diode FET Logic (SDFL) NOR Gate

### 4. Source-Coupled FET Logic (SCFL)

Source Coupled FET Logic (SCFL) uses a differential gate topology as shown in Figure 1.4. It is analogous to bipolar emitter coupled logic (ECL). SCFL is the fastest form of GaAs MESFET logic [26]. It uses differential amplifier circuits which provide the benefit of good common-mode rejection. This property is advantageous because any wafer-to-wafer variation in the threshold voltage becomes a common mode voltage and will not affect the switching threshold of the circuit. This leads to a design tolerable to FET threshold variation when compared to DCFL. Another advantage of differential circuits is their high transconductance, g<sub>m</sub>, leading to a high cut-off frequency and a better switching speed than DCFL. SCFL has good noise margins because it is differential. The circuit operates by steering a fixed current through a pair of switches and then using this current to develop a voltage drop across one of a pair of load devices [27]. The main drawback of SCFL is the high power consumption. Also, the differential circuit requires routing of all

variables and their complement, which increases the metallization and wiring area, leading to increases in the parasitic capacitances in the circuit.

Figure 1.4: Source-Coupled FET Logic (SCFL) Inverter (Differential Inputs)

# 5. Alternative Logic Families

There are many families other than DCFL, BFL, SDFL, and SCFL with various levels of performance. In the following sections, these families are discussed very briefly.

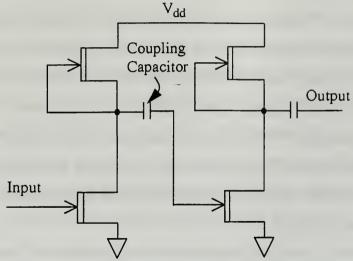

# a. Capacitor-Coupled Logic (CCL)

This logic family uses a coupling capacitor between stages to give the necessary level shifting to drive D-MESFET-only logic. CCFL offers lower power consumption than BFL and SDFL due to the absence of any power consuming level shifting stage [28]. The capacitance in CCL is implemented with a reversed biased Schottky diode [29]. Figure 1.5 shows the circuit diagram of two CCL cascaded inverters.

Figure 1.5: Capacitor-Coupled Logic (CCL) Inverters

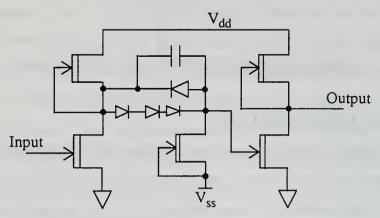

## b. Capacitor Diode FET Logic (CDFL)

In order to overcome the problem of dynamic only operation of the CCL family, capacitor diode FET logic has been devised. The dc level shifting stage is added in parallel with the capacitor. Since this stage is only required to provide coupling at low frequencies, the drive requirements are small and thus a very low power dissipation can be maintained in this extra stage [30]. The circuit diagram for this family is shown in Figure 1.6.

Figure 1.6: Capacitor Diode FET Logic (CDFL) Inverter

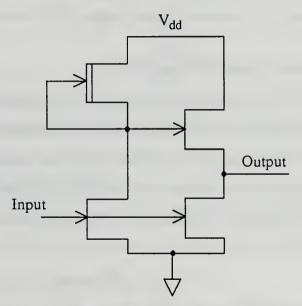

## c. Super-Buffer FET Logic (SBFL)

The use of quasi-complementary output drivers (super-buffers) will give better current drive capability which improves the switching speed of DCFL family, providing a new circuit called super buffer FET logic (SBFL) [2, 31]. This family has a push-pull output stage to provide increased drive capability. The SBFL inverter is shown in Figure 1.7. The disadvantage of SBFL is the power and ground current spikes that occur when the output waveform switches from high to low. The reason for the spikes is that both the source follower and the pull down transistors are ON at the same time. Power consumption for SBFL is also very high.

Figure 1.7: Super-Buffer FET Logic (SBFL) Inverter

#### E. DYNAMIC LOGIC CIRCUITS

Dynamic logic circuits have been used in silicon MOSFET technologies to decrease power dissipation and thus increase logic function complexity and circuit density. The basic dynamic gate consists of a N-channel transistor logic structure whose output node is precharged to  $V_{DD}$  through a clocked P-channel transistor and conditionally discharged to  $V_{SS}$  or ground through a switching N-channel transistor. Dynamic circuits require a clock

for proper operation. Dynamic logic is a non-ratioed logic, meaning that the logic levels are not determined by the width and length ratios of the load and switching transistors. This allows the design of dynamic logic circuits, in most cases, to use minimum device dimensions and results in a small layout area and high fan-in. The use of clocked transistors prevents the flow of current from power supply to ground at the same time, decreasing the static power dissipation. Dynamic circuits have two-phases of operation precharge and evaluation. In the precharge phase, the circuit nodes are charged or discharged to some reference level according to the design. Inputs of the gate can change only during the precharge phase. At the completion of the precharge phase, the path to V<sub>DD</sub> is turned off and the path to ground is conditionally turned on by the clock signal. During the evaluation phase, these precharged nodes either float high or are pulled down according to the gate inputs.

The main drawback of dynamic circuits is the need to route the clock signal to every gate in the circuit which complicates the routing problem and increases the parasitic capacitance. Also, they have a minimum frequency of operation because of the leakage current from the precharged nodes to ground. This drawback can be eliminated in Domino circuits by using a weak pull up P-channel transistor or a feedback transistor. The routing delay of the clock signal across an IC must be considered to prevent clock skew and metastability problems. Finally, charge redistribution problems must be taken care of while designing any dynamic logic circuit. A strong limitation of the simple dynamic structure, which uses only one clock, is the impossibility of cascading the logic blocks to implement complex logic [32]. Figure 1.8 illustrates the situation when cascading two stages of the simple dynamic structure. When the gates are precharged, the output nodes are charged to V<sub>DD</sub>. During the evaluation phase, the output of the first gate will conditionally discharge. Due to the finite pull-down time, the precharged node (N<sub>1</sub>) can discharge the output node of the following gate (N2) before the output of the first stage is correctly evaluated, causing

an erroneous state as shown in Figure 1.8. This problem can be eliminated through careful design of cascaded dynamic logic gates, as explained in the following subsections.

Figure 1.8: Erroneous Evaluation in Cascaded Dynamic CMOS Gates

# 1. CMOS Dynamic Logic

# a. Domino Logic

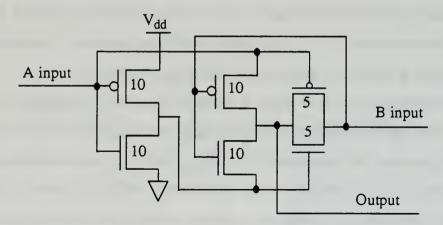

Domino logic modifies the simple dynamic structure by adding a static buffer (inverter) to each logic gate output. This allows a single clock to precharge and evaluate a cascaded set of dynamic domino logic blocks without entering an erroneous state [33]. The basic Domino logic gate is shown in Figure 1.9. The output of the dynamic gate goes only to the buffer and the output of the buffer is the logic gate output. During the precharge phase, the dynamic gate output is a logic high and the buffer output is a logic low. Also, all domino gate outputs are low, thus the transistors they drive are cutoff. During the evaluation phase, the domino logic gate output can only make a transition from low to high.

As a result, there can be no switching hazards at any node in the circuit because nodes can make at most a single transition and then must remain stable until the next precharge cycle. In a cascaded set of logic blocks, each stage evaluates and then causes the next stage to evaluate. Dynamic domino logic circuits have low power consumption because there is no dc path from  $V_{DD}$  to ground, except for the static buffer. Also, the full pull-down current is available to drive the output nodes. At the same time, the load capacitance is much smaller than complementary circuits because most of the P-channel transistors have been eliminated from the load. Domino circuits use a single clock which provides a simple operation and full utilization of the speed of each gate.

The limitation of this circuit technique is that all of the gates are non-inverting, meaning that it does not form a complete logic family. Another limitation is that each gate must be buffered by a static inverter, meaning that this technique is not completely dynamic and dissipates some static power. Finally, in common with all dynamic circuits, charge redistribution can be a problem.

Figure 1.9: Dynamic Domino Logic Gate

To allow a lower frequency of operation and to avoid the risk of storing data on floating nodes, a low current, weak pull-up P-channel transistor can be added, in parallel with the main pull-up transistor. With the gate of the weak pull-up transistor grounded, the buffer input is pulled up during precharge. This will force the buffer output to be low, compensating for the leakage currents. The weak pull-up transistor must be small enough (small W/L) not to fight against discharging of the dynamic logic gate output node during evaluation. There is no significant impact on pull-down current and the power consumed during the evaluation phase is tolerable. In some applications, when the precharge time is long enough, the clocked P-channel transistor can be eliminated and substituted with the weak transistor [32]. Domino gates may also be made latching by including a feedback P-channel transistor from the output of the buffer to its input. This transistor is sometimes called a 'not to forget transistor'.

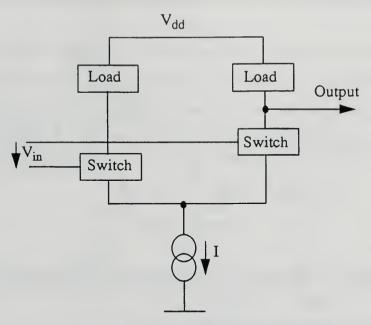

## b. N-P Domino Logic

The limitation of Domino logic is the lack of inverted logic functions. The combination of the dynamic block with a static inverter will give a non-inverted output signal. This decreases the logic flexibility and therefore may require more transistors per logic function. Another limitation in Domino circuits is the difficulty of pipelining multiple stages because all the logic blocks evaluate and precharge together.

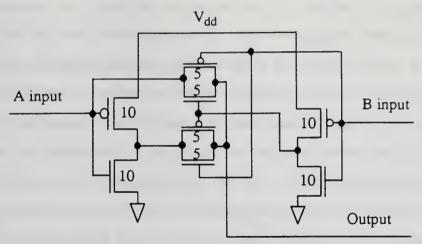

N-P Domino circuits solve the above two problems. The logic functions in N-P Domino circuits are implemented using N-type and P-type dynamic blocks, as shown in Figure 1.10. The output of the N-type is fed to the input of the P-type logic block and the output of the P-type is fed to the input of the N-type logic block, and so on [34, 35]. The static buffer is used only if the output of one type of logic is fed to the input of the same type. This dynamic logic family requires both the clock and its complement to drive N-type and P-type blocks respectively. The N-type logic block will precharge to VDD and the P-type block will pre-discharge to ground during their precharge phase. That is why this

implementation is sometimes called 'zipper logic'[36]. During precharge phase, all the transistors in n-logic and p-logic blocks will be turned off.

The removal of the static inverter will reduce the static power dissipation and also make this family capable of producing inverted output. Zipper implementation make this family suitable for pipelining. The limitation of this logic family is the use of the slow P-channel transistors in evaluating the logic function. This will limit the maximum frequency of operation of the circuit, especially in gallium arsenide implementations.

Figure 1.10: N-P Domino Dynamic Logic Gate

# c. Two-Phase Dynamic Logic

This family uses only N-channel transistors in evaluating the function. As the first stage evaluates its output node, the second stage will be precharging and vise versa. The two successive blocks are fed from two non-overlapping clock phases. A pass gate is used between successive logic blocks to isolate the data stored at the input of the second block from corruption when the output of the first block is precharging. Clocking of two-phase logic is shown in Figure 1.11. The two clock phases  $\phi_1$  and  $\phi_2$  are non-overlapped in the logic high level [32]. The main disadvantage of this family is the use of extra metallization to run the two clock phases and their complements.

Figure 1.11: Clocking of Two-Phase Dynamic Logic

## 2. GaAs MESFET Dynamic Logic Families

In GaAs MESFET static logic circuits, direct current flows at all times from power supply to ground. Also, static logic is usually dependent on width ratios to control logic levels and noise margins. Therefore, these circuits are called 'ratioed logic'. The speed and power dissipation are inversely proportional to the device widths. In static logic circuits, decreasing the power supply voltage will reduce the dissipated power but will reduce the output voltage transition which decreases the noise margin. Also, reducing the supply voltage will reduce the current flow in the circuit which decreases the switching speed. Shrinking the transistor-gate widths will save some layout area but will sacrifice both the drive capability and the speed of the circuit by reducing the current.

Dynamic logic has been relatively un-exploited with GaAs FET technology. Earlier applications were mainly oriented toward very high speed SSI circuits such as divide by two and shift register circuits [37, 38, 39].

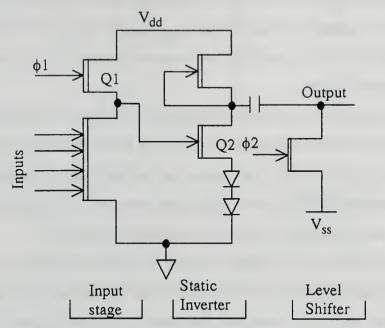

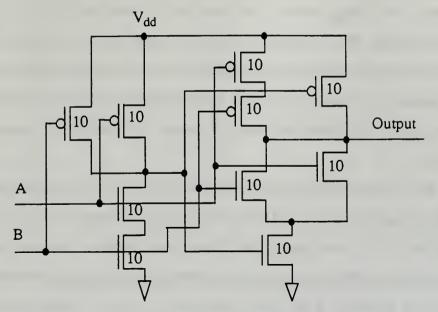

The first Domino circuit was demonstrated in reference 40 and is a four-input AND gate. It is shown in Figure 1.12. It consists of three stages, an input stage, an inverting stage, and a level shifting stage and is composed entirely of depletion mode MESFETs. It requires two power supplies and two in-phase clock signals, level shifted with respect to each other. If Q1 and Q2 are enhancement-mode transistors, there will be only one clock and one power supply required for this circuit. This will decrease the noise margin of the circuit and decrease the consumed power.

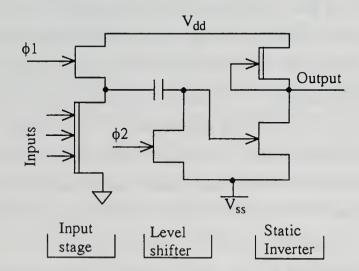

Another Domino circuit is presented in reference 41 and shown in Figure 1.13. It is called Capacitively Coupled Domino Logic (CCDL). It differs from that in Figure 1.12 in two regards. First, the order of the inverting and level shifting stages are reversed. Second, three different threshold MESFETs are required. However, current fabrication technology has enough difficulty controlling two different threshold MESFETs.

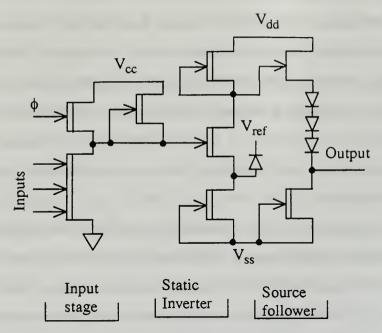

The third Domino circuit is called Trickle Transistor Dynamic Logic (TTDL) presented in reference 42 and shown in Figure 1.14. This Domino topology uses static level shifting rather than capacitive, trading off the need for two clock signals for increased power dissipation. The major drawback of this design is that it requires four power supplies. In all of the above AND gate circuits, the propagation delay was measured to be around 200 ps and the power dissipated per gate was about 0.5 mW. Due to the previously mentioned drawbacks of the Domino circuits, this topology has seen limited use.

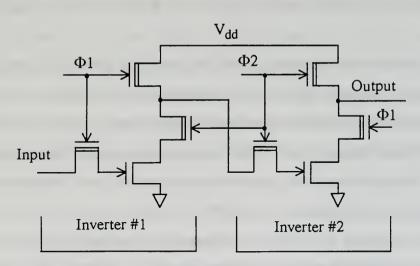

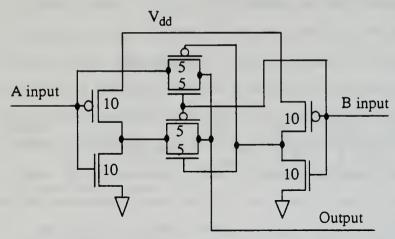

The GaAs implementation of Two-phase Dynamic FET Logic (TDFL) is presented in references 43, 44, 45, 46 and 47. The schematic of two TDFL inverters in series is shown in Figure 1.15. The gates operate from a single power supply and two non-overlapping (in the logic high level) clocks. The precharge phase of the first gate is the evaluation phase of the second stage and vise versa. TDFL circuits are self latching and are suited for pipelined architectures. TDFL gates are non-ratioed which compacts the circuits layout.

Another topology used in GaAs dynamic circuits is pass transistor logic. Application of Si MOS pass transistor topologies in GaAs MESFET circuits is not straight forward. MESFET gate conduction limits the signal levels on control gates and also limits noise

margins. Gate conduction requires different logic transitions on gate nodes than that on drain and source nodes [48]. The circuits used to generate the control signal levels from the data signal levels are both area and power consuming, which limits the use of this topology.

Figure 1.12: GaAs MESFET Domino 3-Input AND Gate

Figure 1.13: GaAs MESFET CCDL 3-Input AND Gate

Figure 1.14: GaAs MESFET TTDL 3-Input AND Gate

Figure 1.15: Two GaAs MESFET TDFL Inverters in Series

### F. OUTLINE OF DISSERTATION

In this dissertation, the possibility of using dynamic digital logic circuits with Complementary GaAs (CGaAs) fabrication processes is explored. Different dynamic circuit configurations are presented. The main problem of exploring these dynamic logic families in NGaAs technology is the gate conduction of GaAs transistors, as well as the absence of the PFETs. This problem is eliminated (partially) when using isolated gate CGaAs technology. In this case, the charge can be stored on the gate capacitor of the transistor for a longer time.