**Calhoun: The NPS Institutional Archive**

**DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

1965

# Control of a real system by a time-shared computer

Browne, Edward R.; Smith, John S.

https://hdl.handle.net/10945/11858

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

NPS ARCHIVE 1965 BROWNE, E.

# CONTROL OF A REAL SYSTEM BY A TIME-SHARED COMPUTER

EDWARD R. BROWNE and JOHN S. SMITH

DUDLEY KNOX LIBRARY

NAVAL POSTGRADUATE SCHOOL

MONTEREY, CA 93943-5101

U.S. NAVYUPO HATE SCHOOL

# CONTROL OF A REAL SYSTEM BY A TIME-SHARED COMPUTER

\* \* \* \* \*

Edward R. Browne and

John S. Smith

### CONTROL OF A REAL SYSTEM

### BY A TIME-SHARED COMPUTER

bу

Edward R. Browne

Captain, United States Marine Corps

and

John S. Smith

Lieutenant, United States Navy

Submitted in partial fulfillment of the requirements for the degree of

> MASTER OF SCIENCE IN ENGINEERING ELECTRONICS

United States Naval Postgraduate School Monterey, California

1 9 6 5

7/---

PRO INF E

CONTROL OF A REAL SYSTEM

BY A TIME-SHARED COMPUTER

Library

U. S. Naval Postgraduate School

Monterey, California

DUDLEY KNOX LIBRARY

NAVAL POSTGRADUATE SCHOOL

MONTEREY, CA 93943-5101

bу

Edward R. Browne

and

John S. Smith

This work is accepted as fulfilling the thesis requirements for the degree of

MASTER OF SCIENCE

IN

ENGINEERING ELECTRONICS

from the

United States Naval Postgraduate School

PARTY OF THE PORT OF THE PROPERTY OF THE PARTY OF T

#### ABSTRACT

Advances in digital computer technology have led to employment of the computer as a control device. Although many theories for utilization of the digital computer as the compensator in a position feedback control system have been proposed, there is little documentation of digital control performance in a hardware environment. This thesis is an investigation of the performance of a real system under sampled-data control. The variable gain amplifier sampled-data control theory is first simulated and then tested on a real system. The hardware and software developments necessary for implementing this control theory are discussed in detail. Additionally, this method is incorporated in a time-sharing computer program for controlling many systems simultaneously from a single computer. Results of the tests are presented and evaluated.

The authors wish to express their appreciation to Professor Robert D. Strum of the U. S. Naval Postgraduate School for his guidance and assistance during this investigation.

# TABLE OF CONTENTS

| CHAPTER I    |       |                                                      | Page |

|--------------|-------|------------------------------------------------------|------|

| Section      | 1.1   | Introduction                                         | 1    |

|              | 1.2   | Digital Controller Design                            | 2    |

|              | 1.3   | Simulation and Results                               | 8    |

| CHAPTER II   |       |                                                      |      |

| Section      | 2.0   | Investigation                                        | 13   |

|              | 2.1   | Theoretical Design                                   | 13   |

|              | 2.2   | Development of Sampled-Data Control<br>Technique     | 16   |

|              | 2.2.1 | Hardware Development                                 | 16   |

|              | 2.2.2 | Software Development                                 | 19   |

|              | 2.3   | Results                                              | 45   |

| CHAPTER III  |       |                                                      |      |

| Section      | 3.1   | Conclusion                                           | 54   |

| BIBLIOGRAPHY |       |                                                      | 58   |

| APPENDIX I   |       | Design of Digital Controllers and Simulation Results | 59   |

| APPENDIX II  |       | Simulation Program                                   | 73   |

| APPENDIX III |       | Continuous Plant                                     | 78   |

| APPENDIX IV  |       | Measurement of Quantization Errors                   | 90   |

| APPENDIX V   |       | Program Flowchart Symbols                            | 96   |

| APPENDIX VI  |       | Programs for the CDC-160 Computer                    | 97   |

# LIST OF ILLUSTRATIONS

| Figure |                                                   | Page |

|--------|---------------------------------------------------|------|

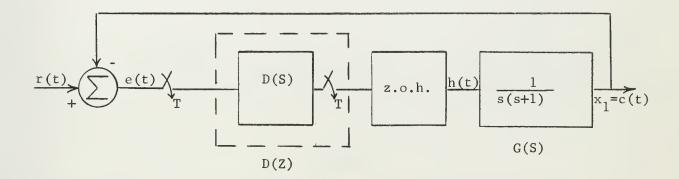

| 1.     | Block Diagram for Type One System                 | 4    |

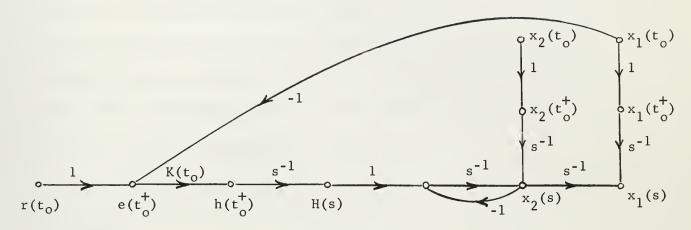

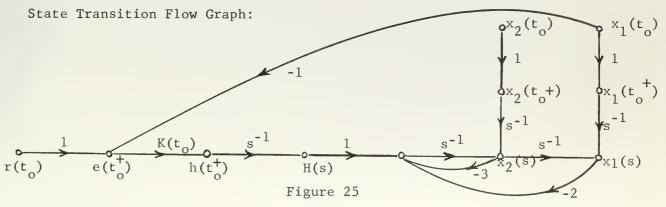

| 2.     | State Transition Flow Graph for Type One System   | 5    |

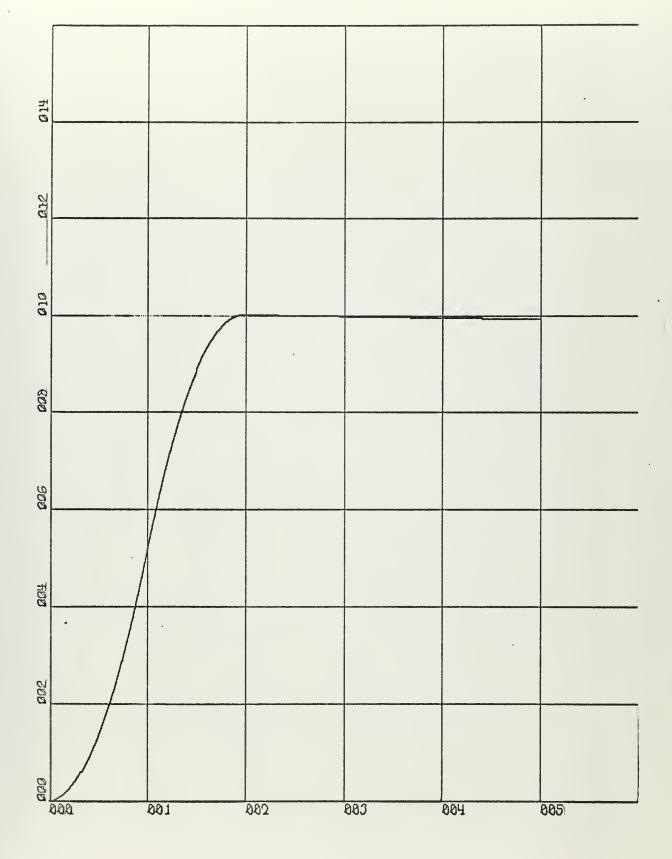

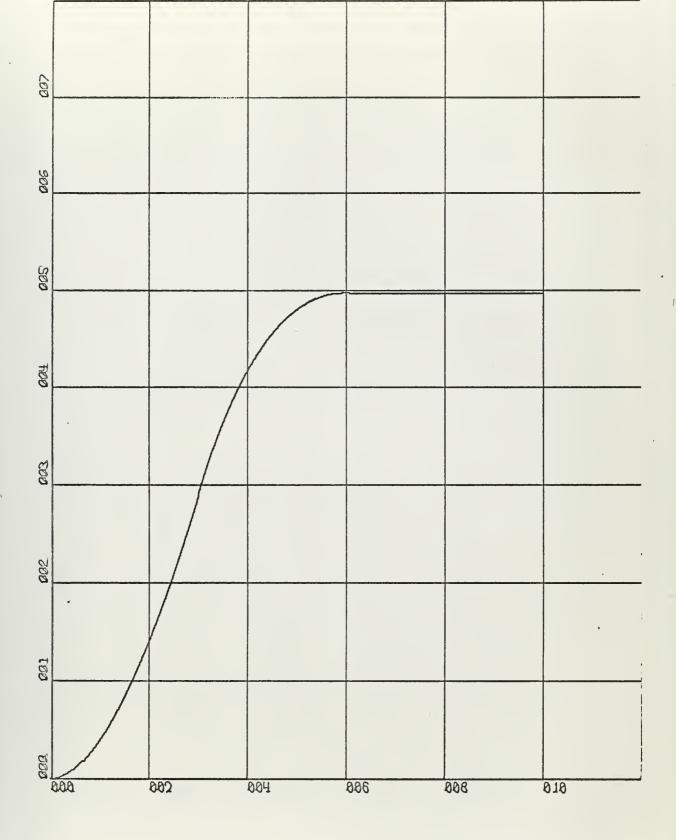

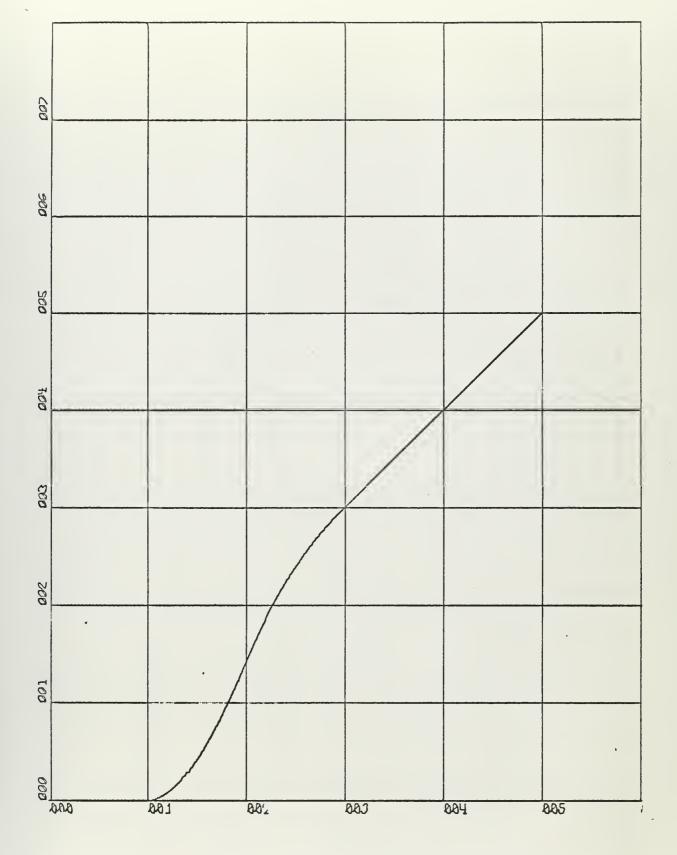

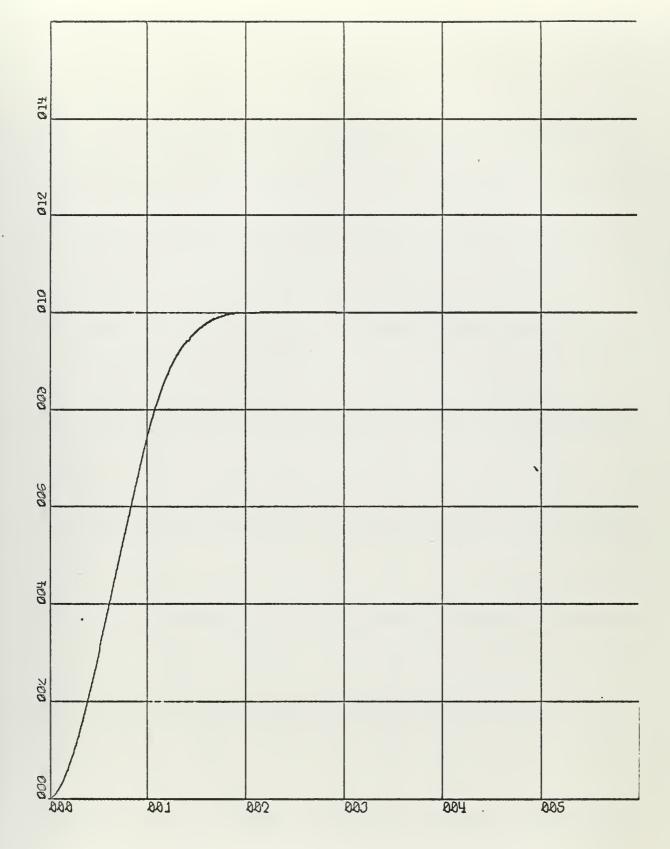

| 3.     | Output vs. Time for Type One System; Step Input   | 10   |

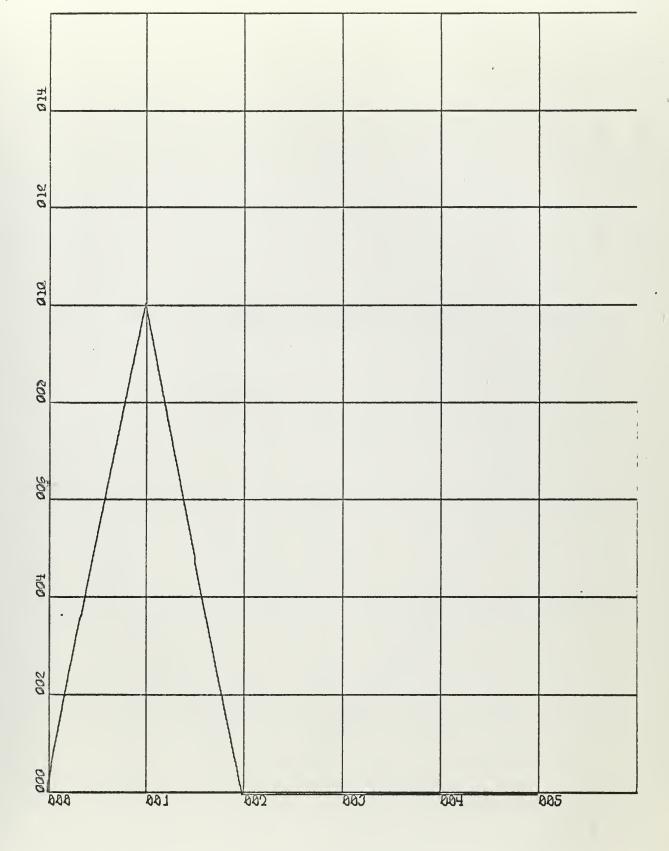

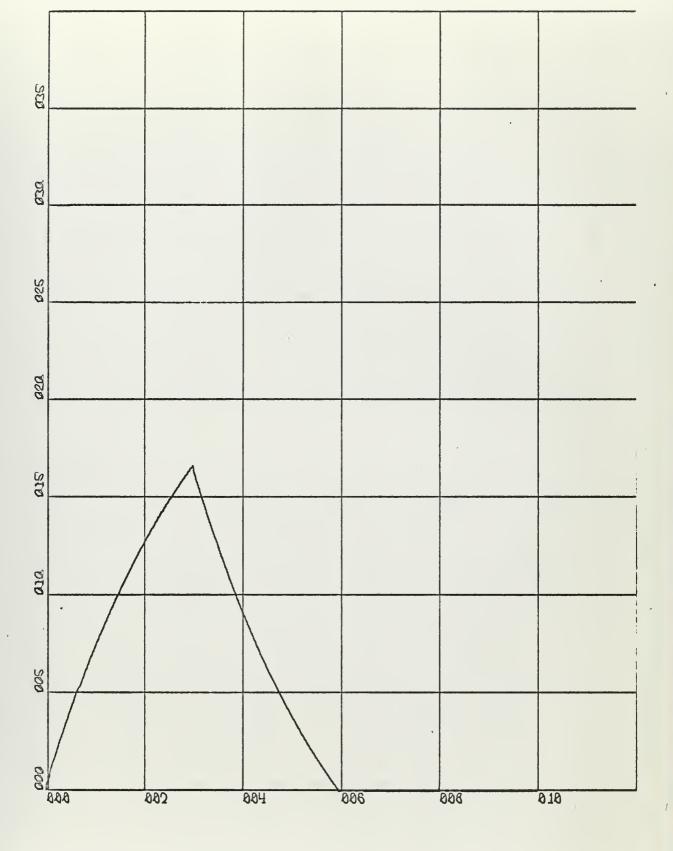

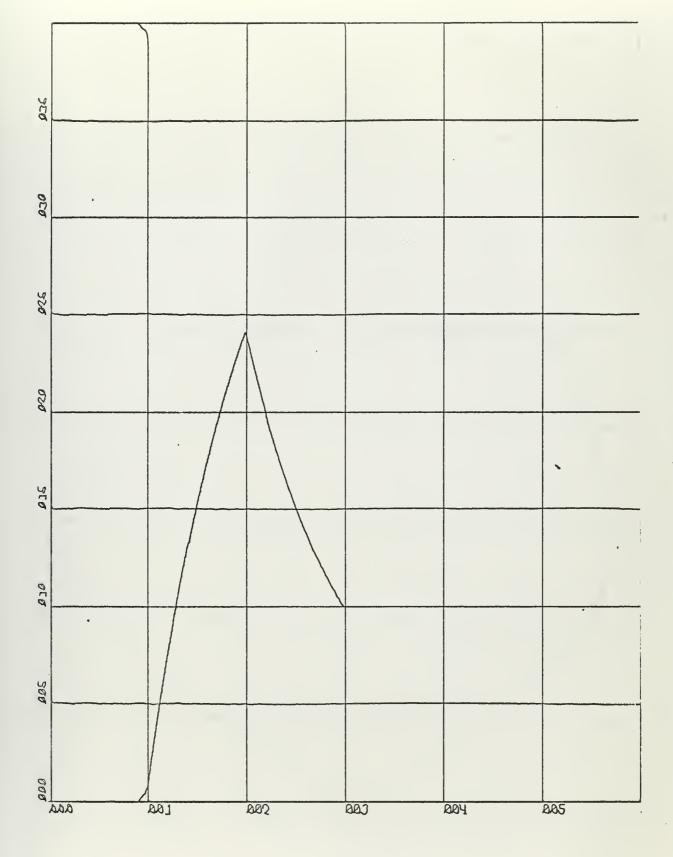

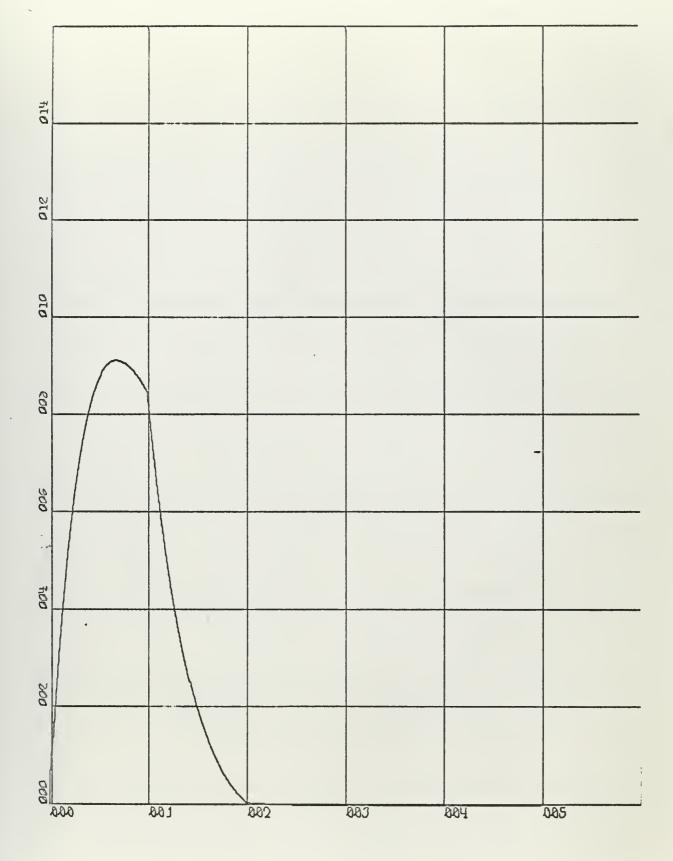

| 4.     | Velocity vs. Time for Type One System; Step Input | 11   |

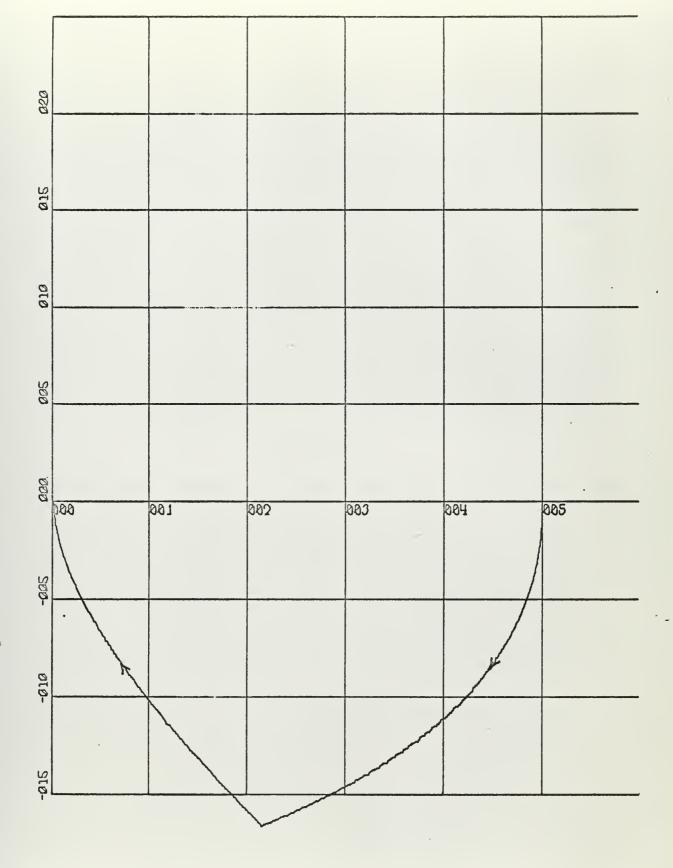

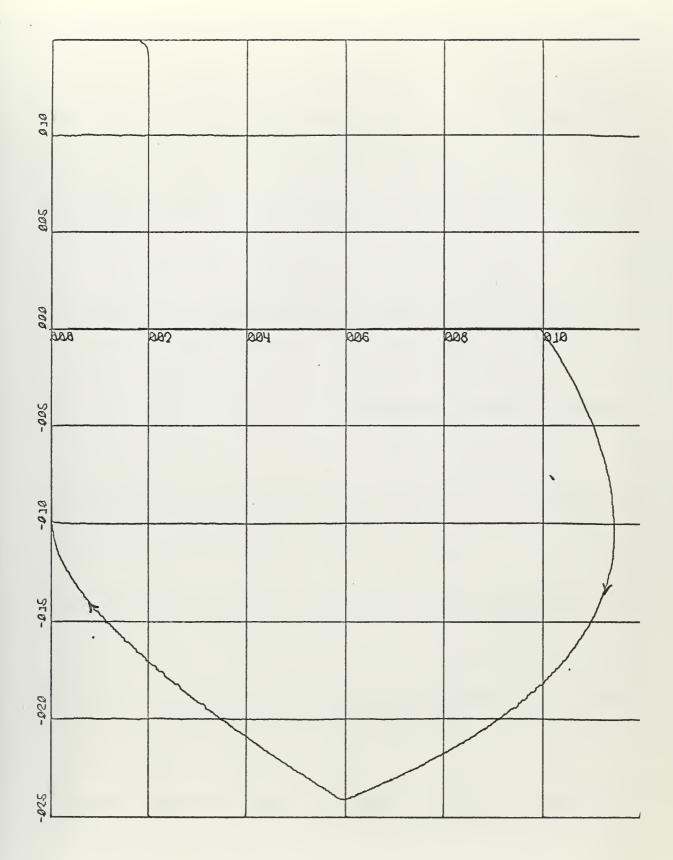

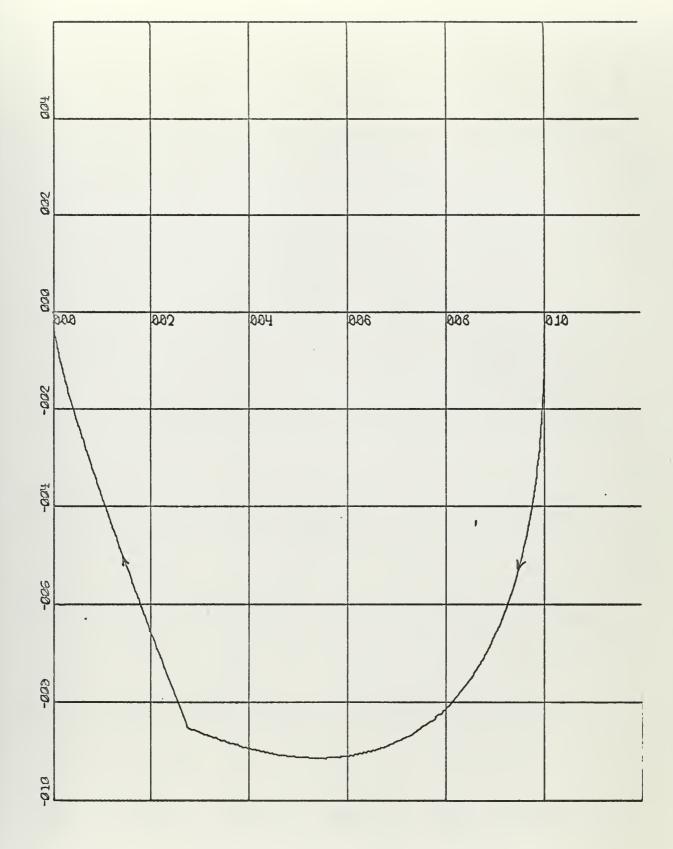

| 5.     | Phase Plane for Type One System; Step Input       | 12   |

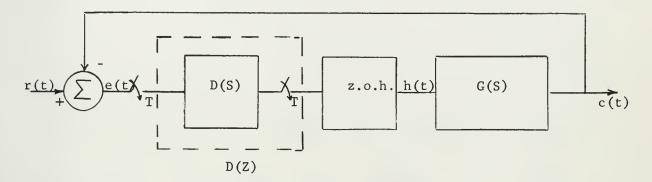

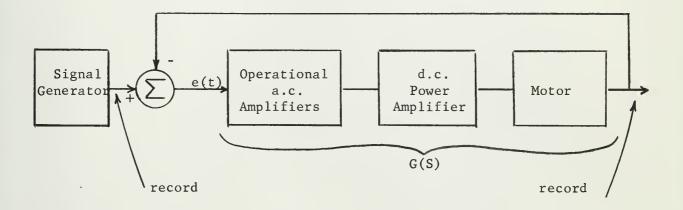

| 6.     | General Block Diagram for Real System             | 13   |

| 7.     | State Transition Flow Graph for Real System       | 14   |

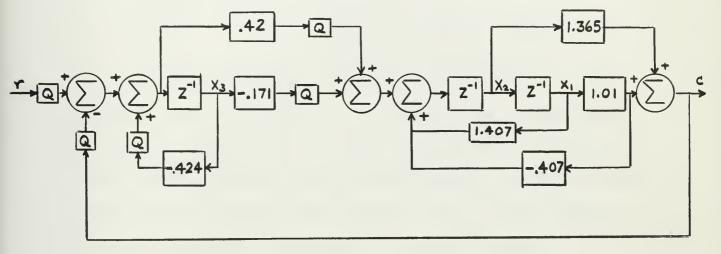

| 8.     | Block Diagram for Implementing D(Z)               | 18   |

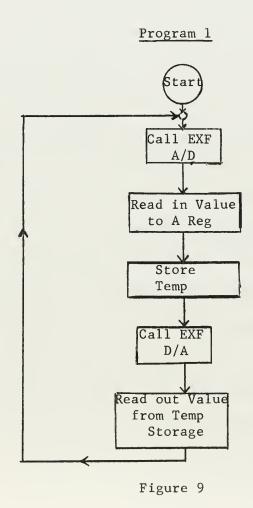

| 9.     | Flow Chart for Program 1                          | 20   |

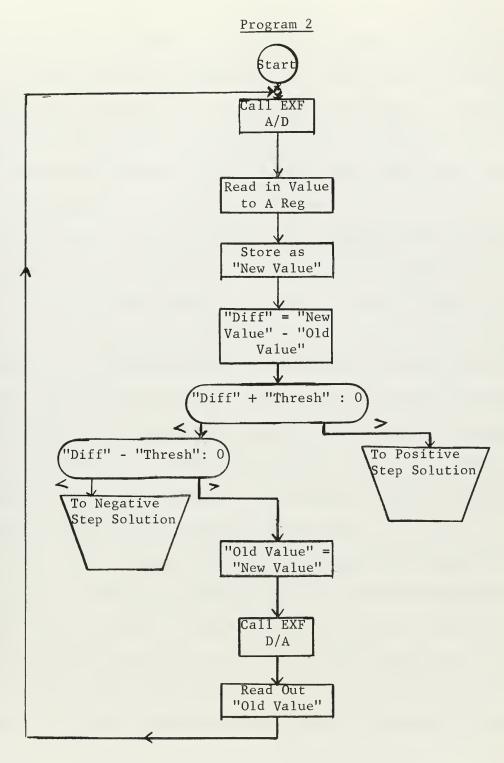

| 10.    | Flow Chart for Program 2                          | 23   |

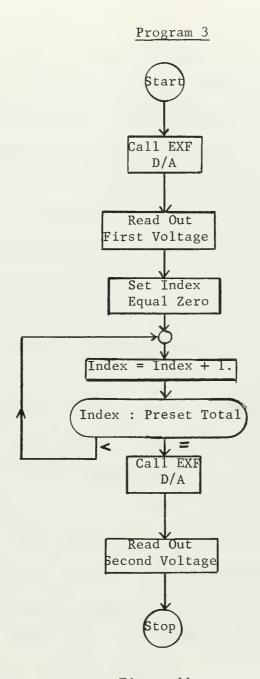

| 11.    | Flow Chart for Program 3                          | 26   |

| 12.    | Flow Chart for Program 4                          | 28   |

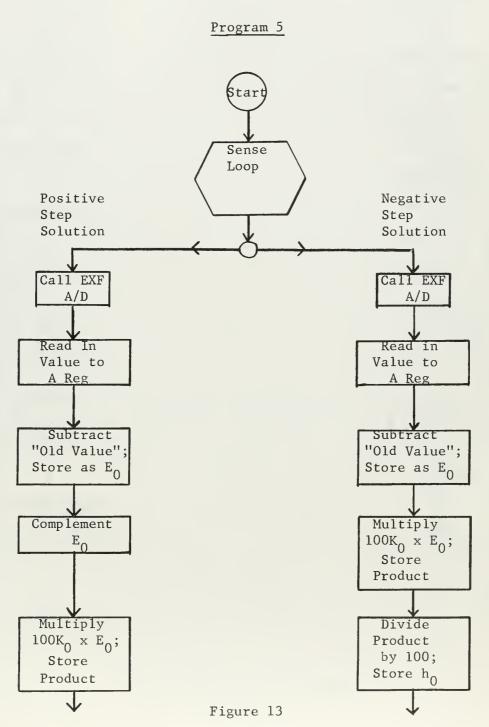

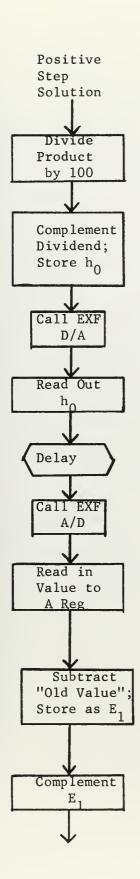

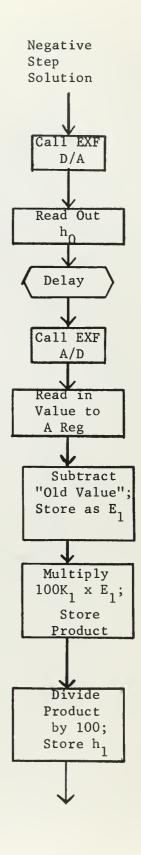

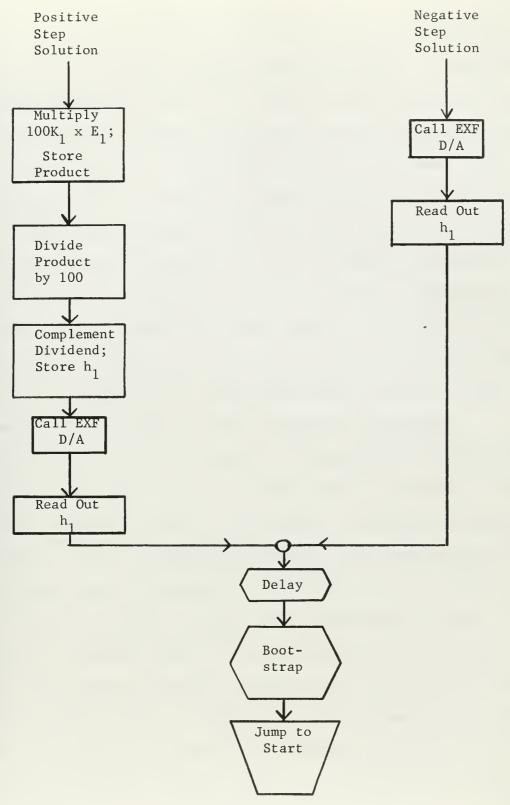

| 13.    | Flow Chart for Program 5                          | 33   |

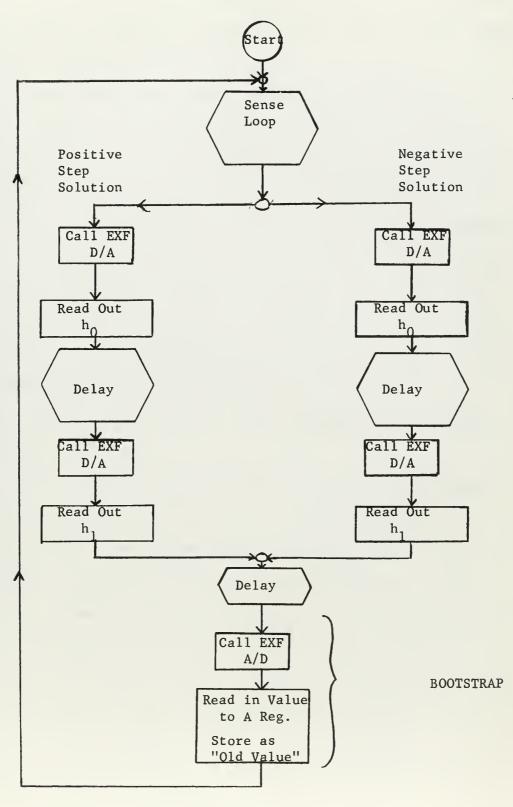

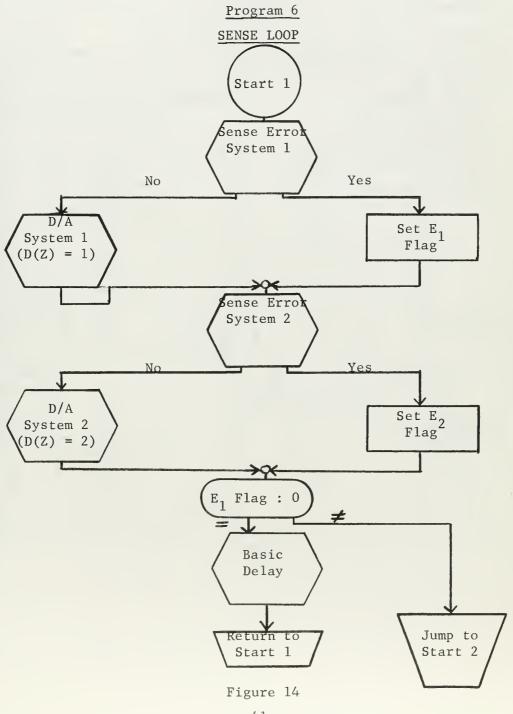

| 14.    | Flow Chart for Sense Loop of Program 6            | 41   |

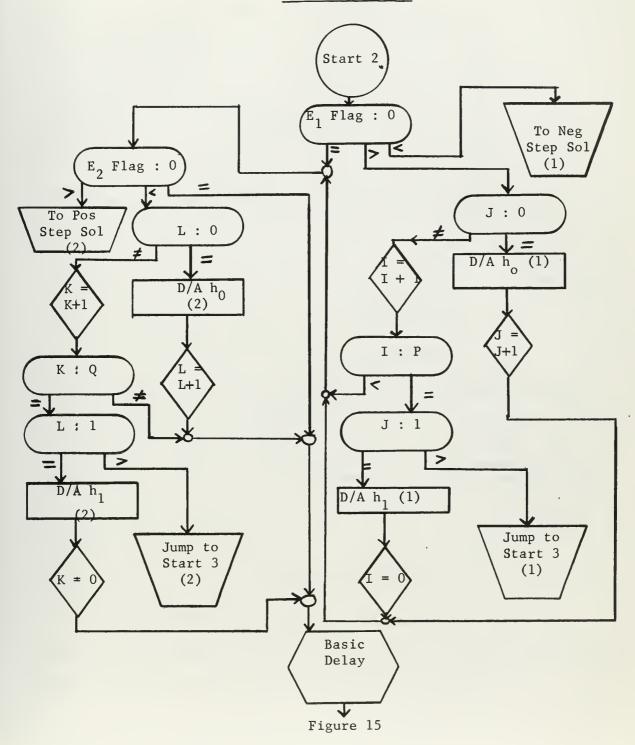

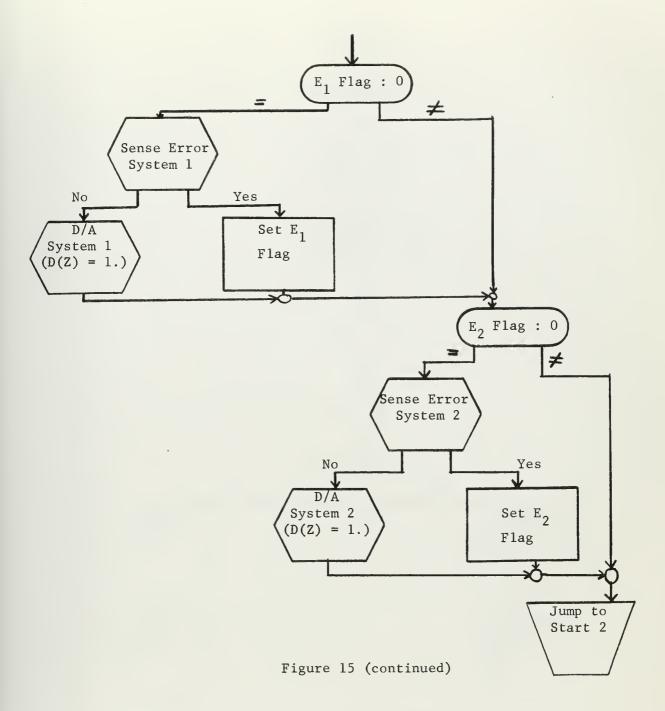

| 15.    | Flow Chart for Solution Routine of Program 6      | 42   |

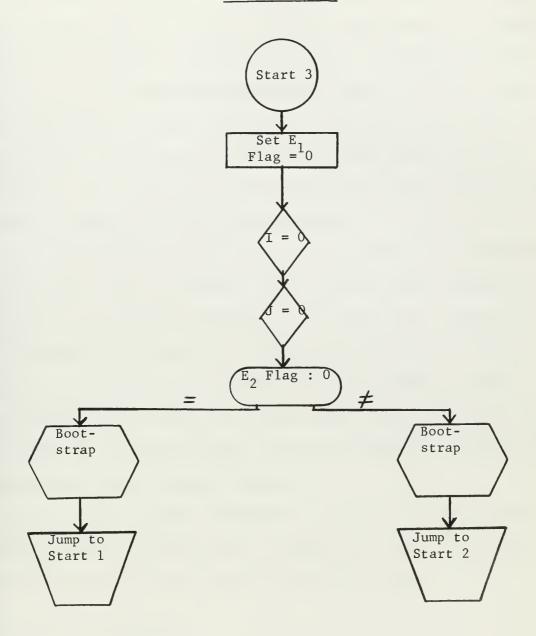

| 16.    | Flow Chart for Return Routine of Program 6        | 44   |

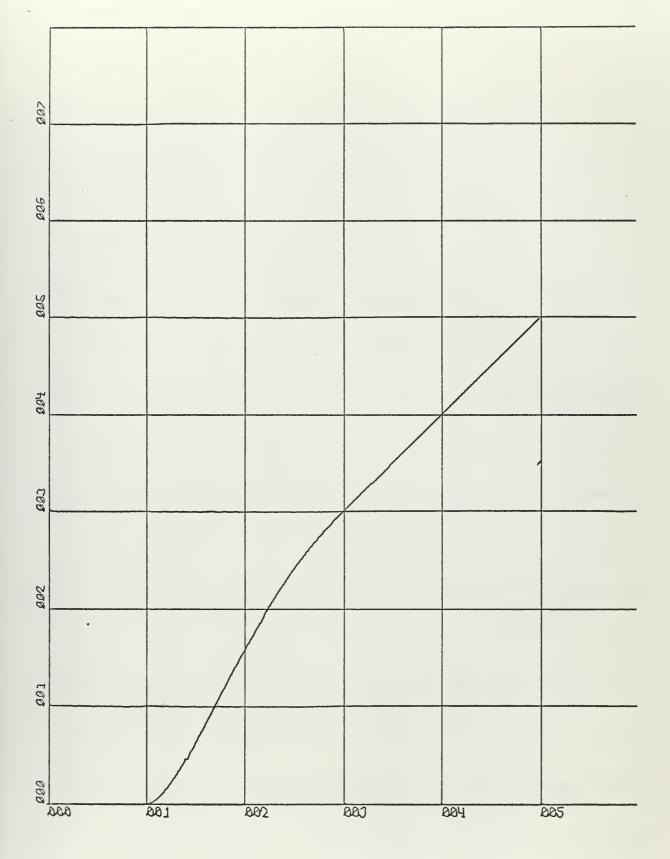

| 17.    | Output vs. Time for Real System Simulation        | 46   |

| 18.    | Velocity vs. Time for Real System Simulation      | 47   |

| 19.    | Phase Plane for Real System Simulation            | 48   |

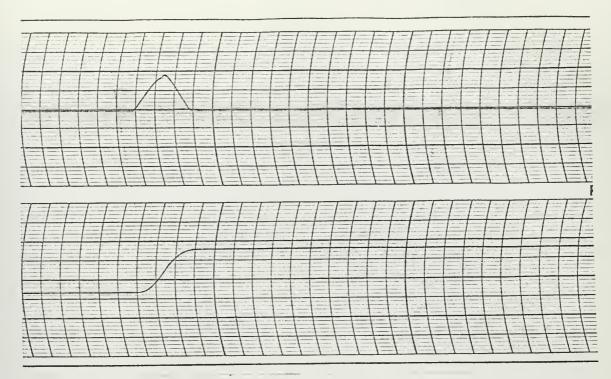

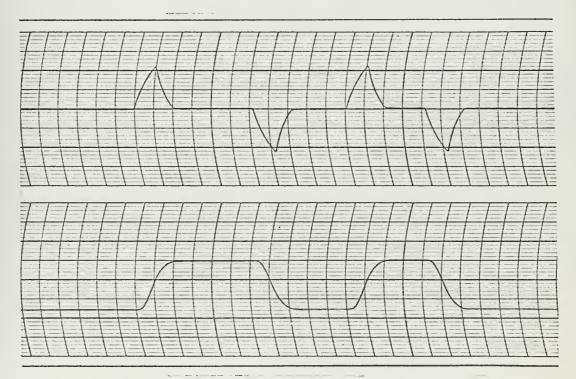

| 20.    | Position and Velocity vs. Time for Real System    | 49   |

| 21.    | Position and Velocity vs. Time for Analog System  | 49   |

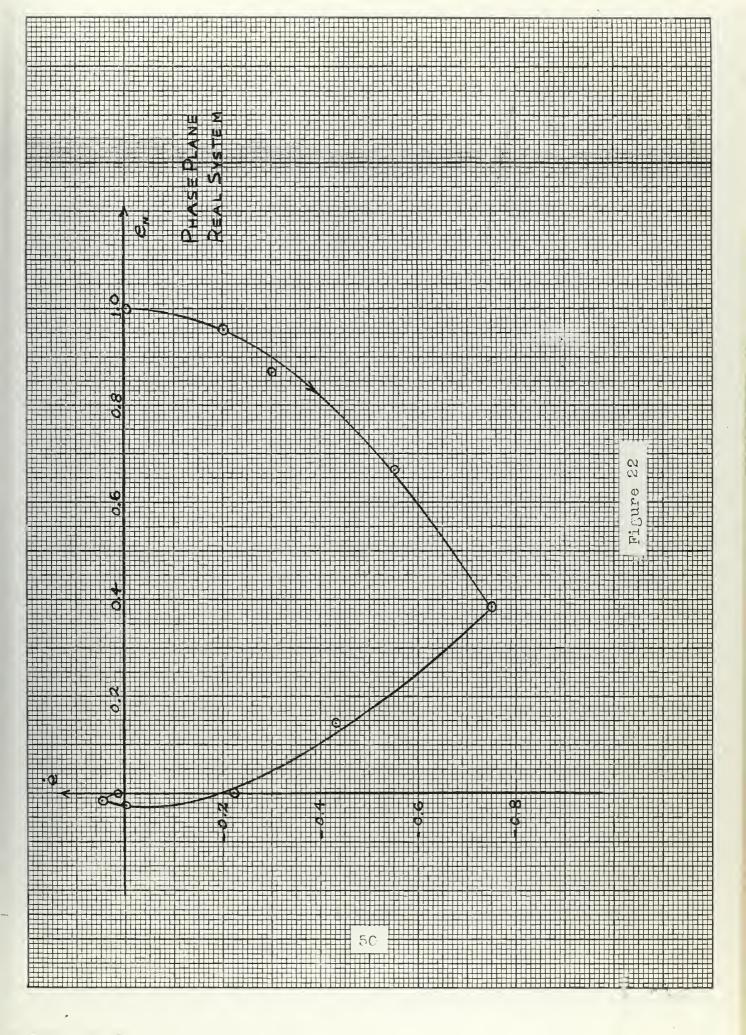

| 22.    | Phase Plane for Real System                       | 50   |

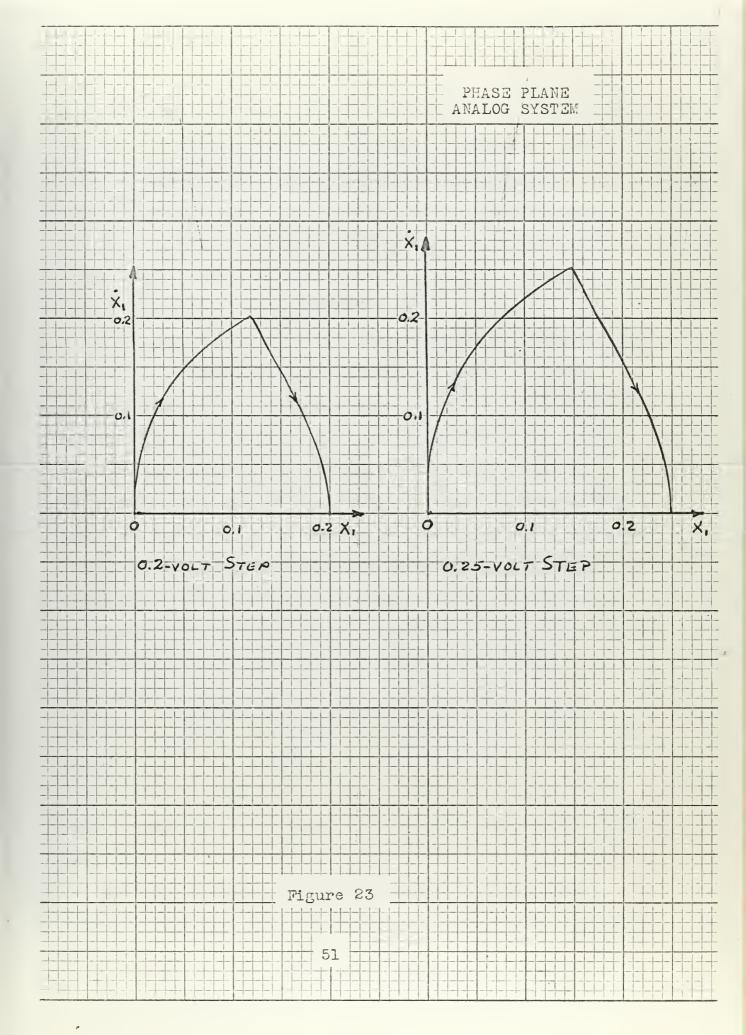

| 23.    | Phase Plane for Analog System                     | 51   |

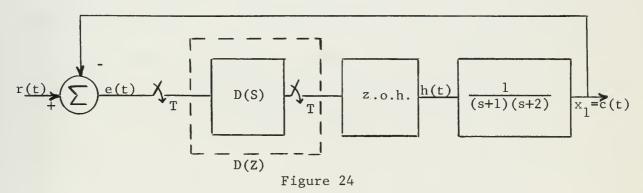

| 24.    | Block Diagram for Type Zero System                | 60   |

| Figure |                                                      | Page |

|--------|------------------------------------------------------|------|

| 25.    | State Transition Flow Graph for Type Zero System     | 60   |

| 26.    | Output vs. Time for Type One System; Ramp Input      | 64   |

| 27.    | Velocity vs. Time for Type One System; Ramp Input    | 65   |

| 28.    | Phase Plane for Type One System; Ramp Input          | 66   |

| 29.    | Output vs. Time for Type Zero System; Step Input     | 67   |

| 30.    | Velocity vs. Time for Type Zero System; Step Input   | 68   |

| 31.    | Phase Plane for Type Zero System; Step Input         | 69   |

| 32.    | Output vs. Time for Type Zero System; Ramp Input     | 70   |

| 33.    | Velocity vs. Time for Type Zero System; Ramp Input   | 71   |

| 34.    | Phase Plane for Type Zero System; Ramp Input         | 72   |

| 35.    | Block Diagram of Amplifier-Motor Combination         | 78   |

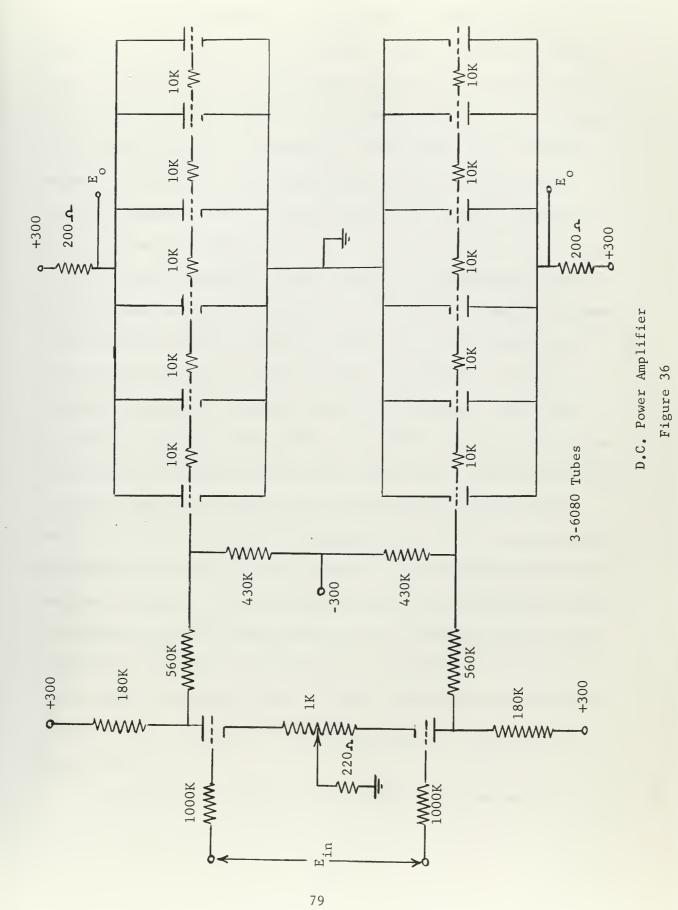

| 36.    | Circuit Diagram of D. C. Power Amplifier             | 79   |

| 37.    | Block Diagram for Determination of Transfer Function | 81   |

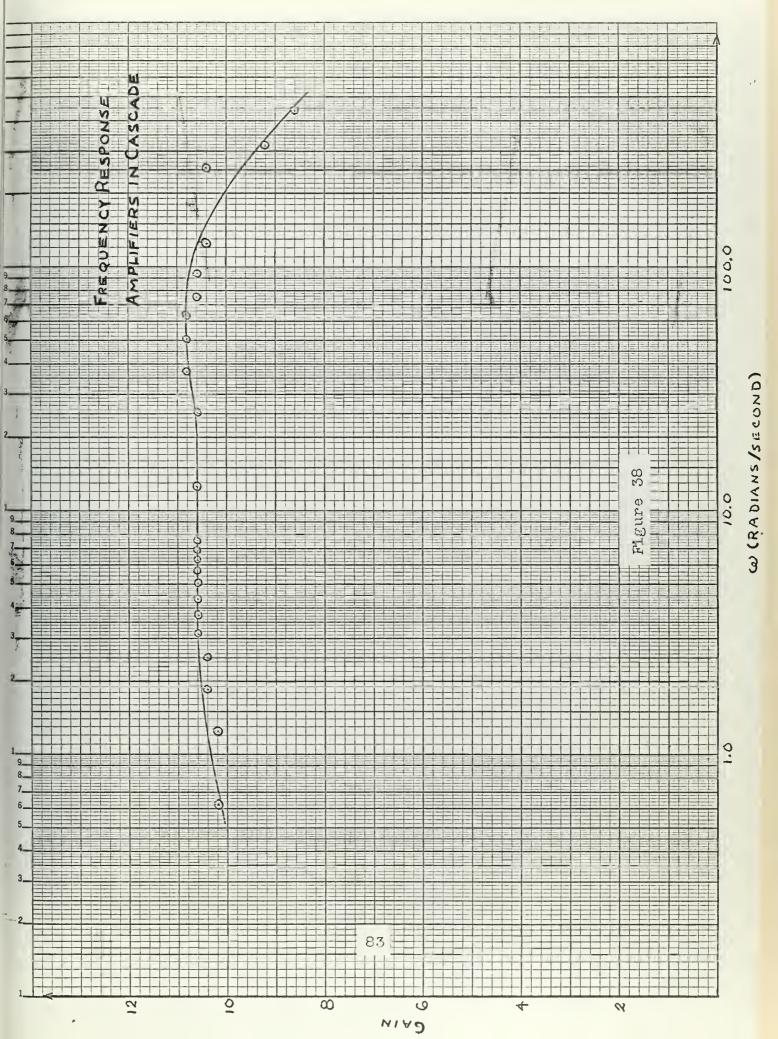

| 38.    | Frequency Response of Amplifiers in Cascade          | 83   |

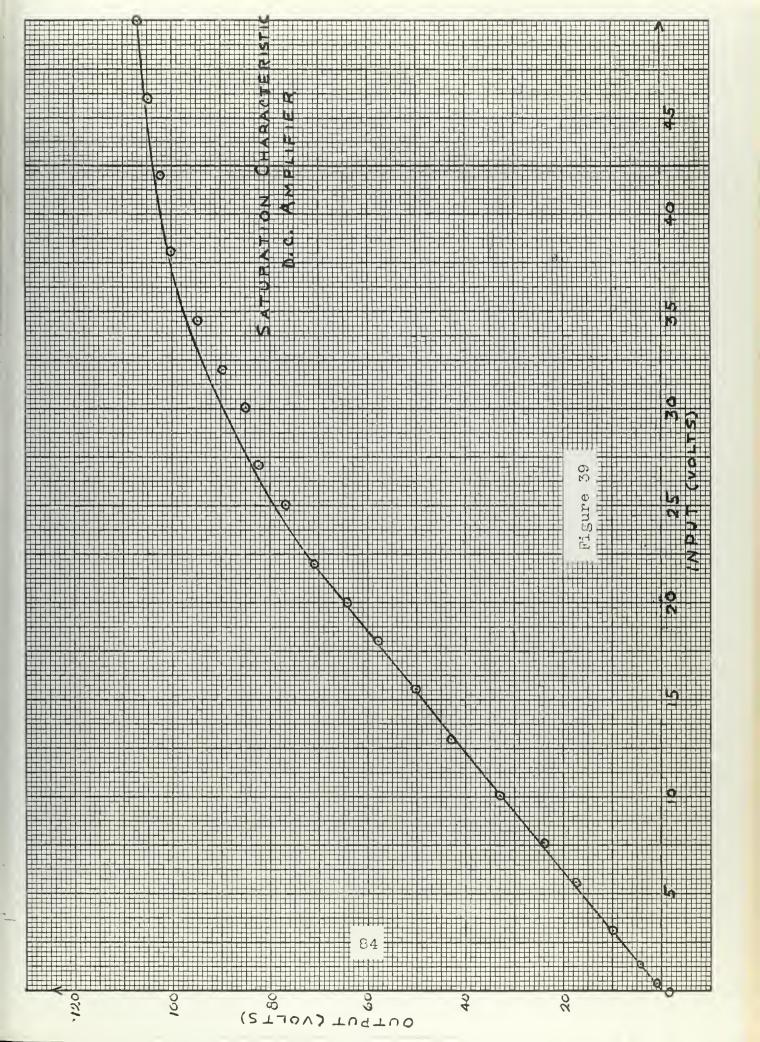

| 39.    | Saturation Characteristic of D. C. Amplifier         | 84   |

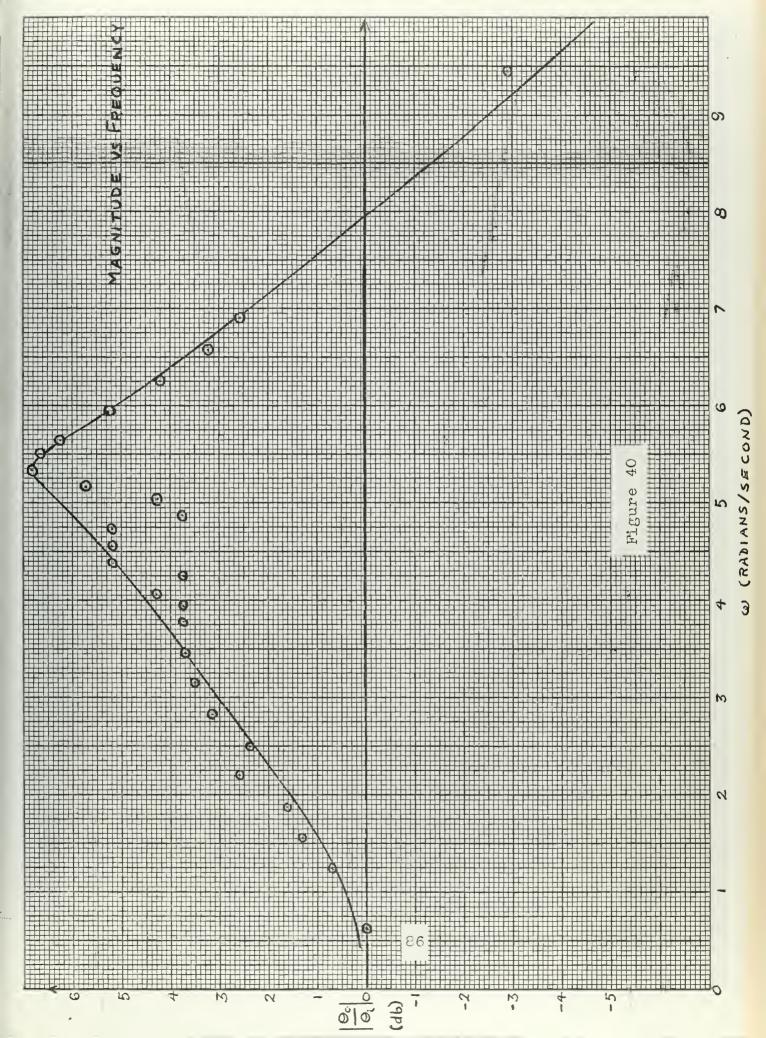

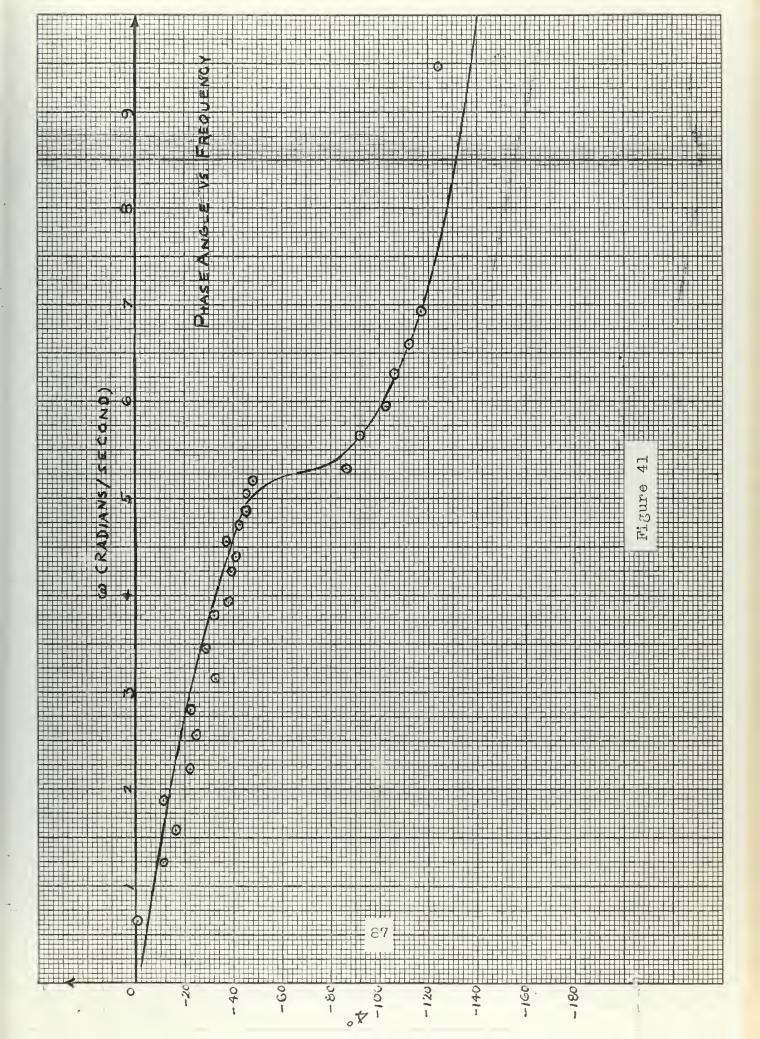

| 40.    | Closed Loop Magnitude vs. Frequency                  | 86   |

| 41.    | Closed Loop Phase Angle vs. Frequency                | 87   |

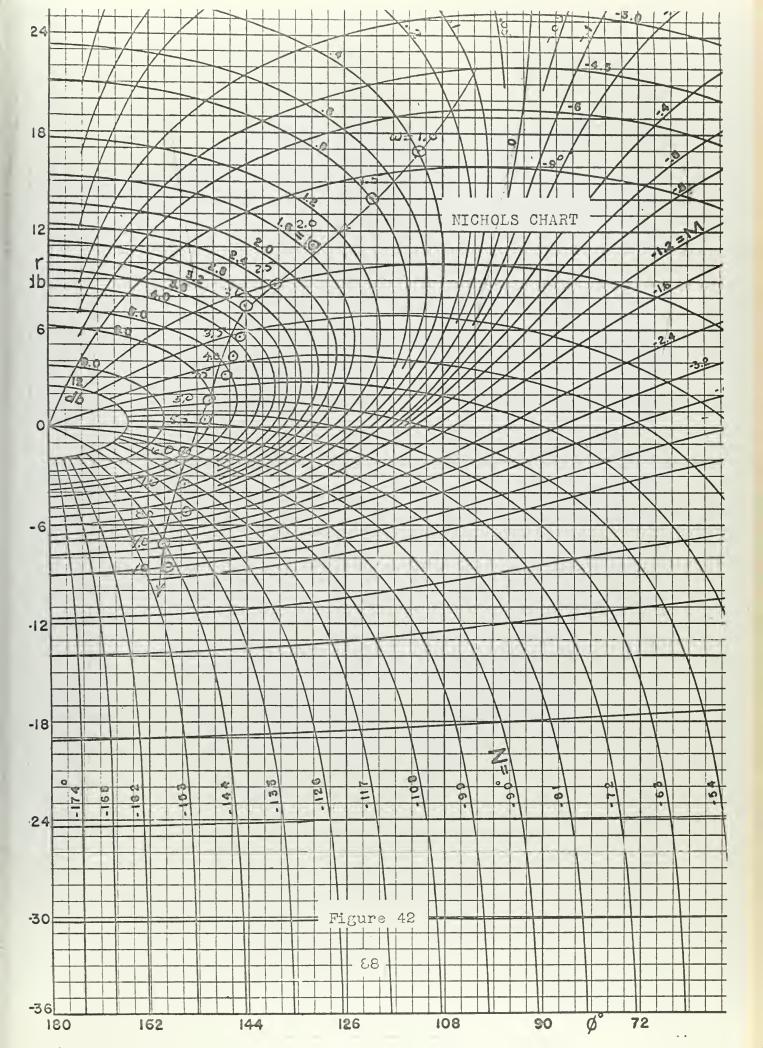

| 42.    | Nichols Chart                                        | 88   |

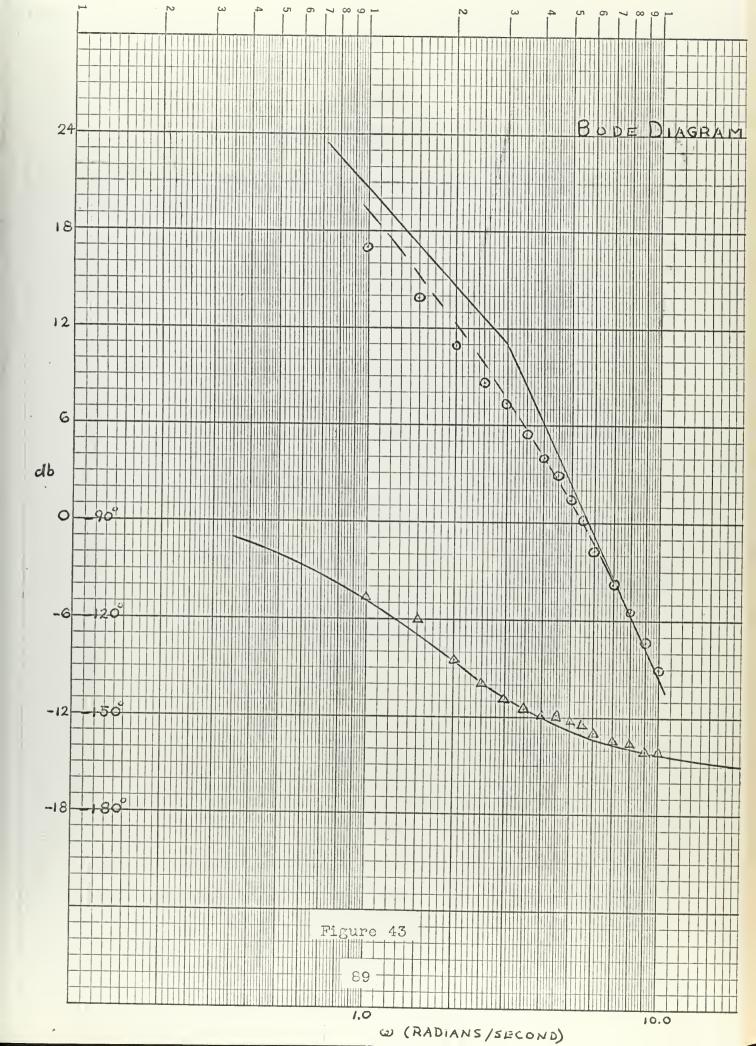

| 43.    | Bode Diagram of Open Loop Transfer Function          | 89   |

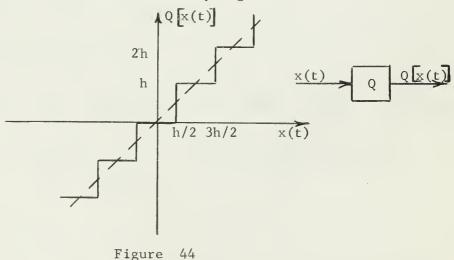

| 44.    | Quantization Operation                               | 90   |

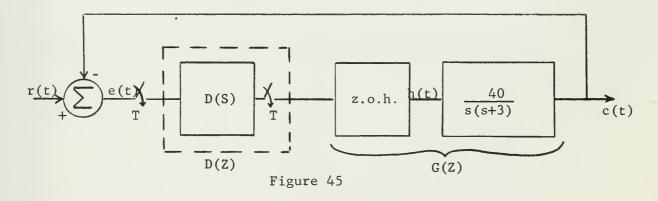

| 45.    | Block Diagram for Real System                        | 91   |

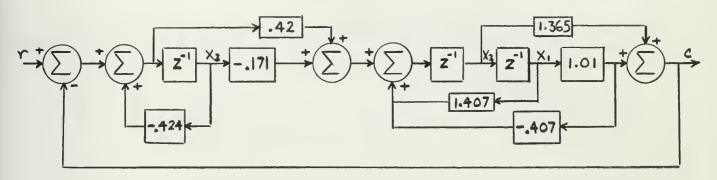

| 46.    | Canonical Form of Sampled-Data Control System        | 92   |

| 47.    | Function of Quantizers in Canonical Form             | 93   |

#### CHAPTER I

### 1.1 Introduction

During the past 15 years, advances in digital computer technology have developed the digital computer into an invaluable tool for all branches of the scientific world. In almost every scientific discipline, the capabilities of the digital computer for vast computational tasks, data processing, and simulation have been profitably employed. In addition to these uses, some engineers in the automatic control field have considered the digital computer, operating in a real time mode, as a tool for improving control techniques and capabilities. It is in this area of computer application that the authors are extremely interested.

There are many theoretical expositions on sampled data control techniques, and some include results from the digital control of simulated plants. However, with the exception of the technical reports of the Navy Electronics Laboratory [1, 2,] the authors were unable to find any information on sampled-data control of an actual plant. It is the opinion of the authors that unless the theory is tested in a hardware environment, the results are academic because of the difficulty in accurately simulating the inherent non-linearities in a real system. It was decided at the outset, therefore, that a prime goal of the thesis was to test the theories of sampled-data control on a real plant.

A second area in which data was lacking involved one of the primary advantages claimed for the sampled-data control techniques: the capability to control many systems simultaneously from the same computer.

Although implementing such a multi-control system is primarily a computer

programming task, certain basic techniques must be developed to insure flexibility and adequate performance. It was felt that the lack of documentation in this area was a serious shortcoming. Thus, a second goal of this thesis was to develop and implement techniques for multisystem sampled-data control.

Having established the basic goals of the thesis, the authors made a decision which essentially limited the scope of the thesis. Throughout the literature, there are many proposed theories for sampled-data control systems. It was decided to select only one of these theories as the basis for the laboratory experimentation. Rather than testing many theories in a less rigorous fashion, the authors preferred to make exhaustive hardware tests on the basis of one theoretical solution to the control problem. In general, the difficulties encountered in one theoretical approach would be comparable to those of another, and the techniques developed may be extended to other theories.

After examining many of the proposed theories, the authors, in conjunction with their advisor, Professor Robert Strum, selected the theory proposed by Benjamin C. Kuo. The basis of this theory is the concept of a variable gain amplifier in the control loop. The theory provides for minimum time, ripple free response to deterministic inputs. The prime reasons for selection of this theory as a basis for the laboratory experimentation are the theoretical advantages it offers, and the relatively simple tasks the digital computer is required to perform.

In considering the laboratory portion of the thesis, the authors

had one more basic decision to make. In selecting a digital computer for the experiments, the facilities at the Postgraduate School offered a choice between a general purpose computer, the Control Data Corporation 1604, and a small data processing computer with an auxiliary arithmetic capability, the CDC-160 in conjunction with the CDC-168 arithmetic unit. Due to the fact that any practical control method must not only perform well, but also must be economically feasible, the smaller, less expensive 160 computer was selected. It is conceded that the larger computer could more efficiently perform the required controlling tasks, but the authors preferred the more realistic practical approach. This led to a secondary goal of the thesis, to be able to comment on the general feasibility of sampled-data control systems on the basis of the results obtained.

# 1.2 Digital Controller Design

Before proceeding with work on the real plant, the authors decided to select a technique for the design of digital controllers for sampled-data control systems. A design theory that would give accurate results and would be readily adaptable to the existing hardware was desired. It was determined that the digital controller design described in Section 9-9 of Analysis and Synthesis of Sampled-Data Control Systems by Benjamin C. Kuo would be well suited to this problem. [3] Kuo's design theory makes use of state space and state transition techniques. It also enables derivation of a D(Z) that will yield a minimum time, ripple free response to the designated deterministic input (i.e., "deadbeat response"). This approach to digital controller design describes the digital controller as a variable gain amplifier which outputs certain values each sampling period in order to control the continuous system

in the desired manner. It is easily adaptable to implementation on a digital computer, and the use of state variables makes the manipulation of the mathematics involved relatively easy.

To explain this "variable gain amplifier" design theory it is best to look at a sample problem. Consider the sampled-data control system of Figure 1. The variables  $\mathbf{x}_1$  and  $\mathbf{x}_2$  are the state variables for the controlled process where  $\dot{\mathbf{x}}_1 = \mathbf{x}_2$ ;  $\mathbf{h}(\mathbf{t})$  is the output of the zero-order hold and  $\mathbf{e}(\mathbf{t})$  is the actuating signal. Note:  $\mathbf{e}(\mathbf{t}) = \mathbf{r}(\mathbf{t}) - \mathbf{c}(\mathbf{t})$ ;  $\mathbf{x}_1 = \mathbf{c}(\mathbf{t})$

Figure 1

To determine a D(Z) for "deadbeat response" to a given input:

- (1) Draw the state transition flow graph of the system with the digital controller represented by a variable gain amplifier K(kT). K(kT) = h(kT) / e(kT).

- (2) For a "deadbeat response" the system error must be zero for t>nT where n is the smallest possible integer.

i.e.,

$$x_1$$

(nT) = r(nT)

$$x_2$$

(nT) =  $x_3$  (nT) = ... =  $x_p$  (nT) = 0. unit step

$$x_2$$

(nT) = 1;  $x_3$  (nT)= $x_4$  (nT)=...= $x_p$  (nT) = 0. unit ramp

From this information the variable gains  $(K_{k} \mid s)$  and the minimum n can be determined.

- (3) Compute the  $h(0^{+})$ ,  $h(T^{+})$ , .... $h(nT^{+})$  using the  $K_{k}$  's determined and recalling that  $e(kT^{+})=r(kT)-x_{1}(kT)$ .

- (4) Calculate D(Z) using the relationship D(Z)=H(Z)/E(Z).

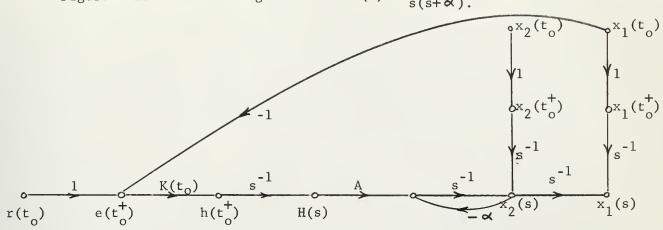

Returning to the example, let us draw the state transition flow graph of the system.

Figure 2

Using Figure 2 and applying flow graph techniques and the inverse Laplace transformation we arrive at the following:

Now let us assume a unit step input and a sampling period of one tenth of a second. (r(kT) = 1.0, T=0.1)

$$\begin{aligned} & \mathbf{x}_1 & \left[ (k+1)\mathbf{T} \right] &= (1 - 0.005K_k)\mathbf{x}_1(k\mathbf{T}) + 0.095 \ \mathbf{x}_2(k\mathbf{T}) + 0.005K_k \\ & \mathbf{x}_2 & \left[ (k+1)\mathbf{T} \right] &= -0.095K_k\mathbf{x}_1(k\mathbf{T}) + 0.905\mathbf{x}_2(k\mathbf{T}) + 0.095K_k \end{aligned}$$

For k=0 and  $x_1(0) = x_2(0) \stackrel{\triangle}{=} 0$ .

$$x_1(T) = 0.005K_0$$

$$x_2(T) = 0.095K_0$$

From the constraints placed on the problem (i.e.,  $x_1(nT) = r(nT)$  and  $x_2(nT)=0$ .) it may be seen that the solution can not be obtained from the above. In practice this means that the output of the controlled process cannot be made equal to a step input in one sampling period. We must therefore proceed to the second sampling period and let k=1. Doing this and setting  $x_1(2T) \triangleq 1.0$  and  $x_2(2T) \triangleq 0$ . yields:

$$x_1(2T) = 0.014K_0 - 0.000025K_0K_1 + 0.005K_1 \stackrel{\triangle}{=} 1.0$$

$$x_2(2T) = 0.086K_0 - 0.000475K_0K_1 + 0.095K_1 \triangleq 0.0$$

from which

$$K_0 = 105.6$$

;  $K_1 = -203.0$

therefore

$$e(0^+) = r(0)-x_1(0)=1$$

;  $e(T^+)=r(T)-x_1(T) = 0.472$

$$h(0^{+}) = 105.6$$

;  $h(T^{+}) = K_{1}e(T^{+}) = -95.8$

and

$$D(Z) = \frac{h(0^+) + h(T^+)Z^{-1}}{e(0^+) + e(T^+)Z^{-1}} = \frac{105.6 - 95.8 Z^{-1}}{1 + 0.472 Z^{-1}}$$

The above example demonstrated the technique of designing a digital controller for a sampled-data control system using the variable gain amplifier concept. It should be observed that in implementing this controller using a digital computer, the D(Z) does not have to be actually calculated. In fact, only the  $K_{\underline{k}}$ 's need be entered in the computer.

This proves to be quite advantageous since for a given sampling period the  $K_k$ 's are only a function of the continuous system gain and the G(S). Thus for a digital computer controlling a number of plants the  $K_k$ 's could be pre-computed and stored in the computer ready for use. These variable gains when multiplied by the sensed error and output at the sampling rate will provide the desired system response to the designated input. In fact, the digital controller designed above will yield the desired "deadbeat response" to any step input. It must also be pointed out that the design given is only for a step input and will not give optimum response for a ramp or parabolic input.

The design problem as stated and solved above was for the control of a type one system in response to a step input. In studying this design technique a digital controller was also designed for the same type one system  $(G(S) = \frac{1}{s(s+1)})$  for "deadbeat response" to a unit ramp input. With respect to a ramp input, optimum response was obtained in three sampling periods. It was also noted that once zero error had been achieved a constant output of 1.0 was needed from the controller. This was required because a type one system has an inherent steady state error in response to a ramp input. In this context it is important to realize that with the use of a digital controller a continuous system with an inherent steady state error can be made to respond with "deadbeat response" and no steady state error to any particular deterministic input. (See Appendix I for details.)

In Appendix I a digital controller is also designed for a type zero system (G(S) =  $\frac{1}{(s+1)(s+2)}$ ) which has an inherent steady state

error to both step and ramp inputs. With the designed controller, these errors were reduced to zero.

With regard to type two systems some difficulty was encountered. For a system of the type  $G(S) = \frac{1}{s^2}$  a digital controller was readily designed; however, for a system of the type  $G(S) = \frac{1}{s^2(s+1)}$  the mathematics involved in evaluating the  $K_k$ 's proved to be cumbersome. An iterative solution to the non-linear simultaneous equations was used in evaluating the  $K_k$ 's. This proved to be feasible. Further investigation into the problem was not carried out since the authors wished to direct their efforts to the control of the real system.

## 1.3 Simulation and Results

After completing the design of a digital controller for a "deadbeat response" to a unit step input, it was decided to simulate the system response. This was done to provide a check on the computations and to verify the design theory itself. The simulation programs used were written in Fortran 60 and employ a library routine known as INTEG 1. INTEG 1, written by Dr. J. R. Ward, provides a fourth order Runge-Kutta solution to ordinary differential equations and was well suited to the simulation problem encountered. (Appendix II contains a complete simulation program.)

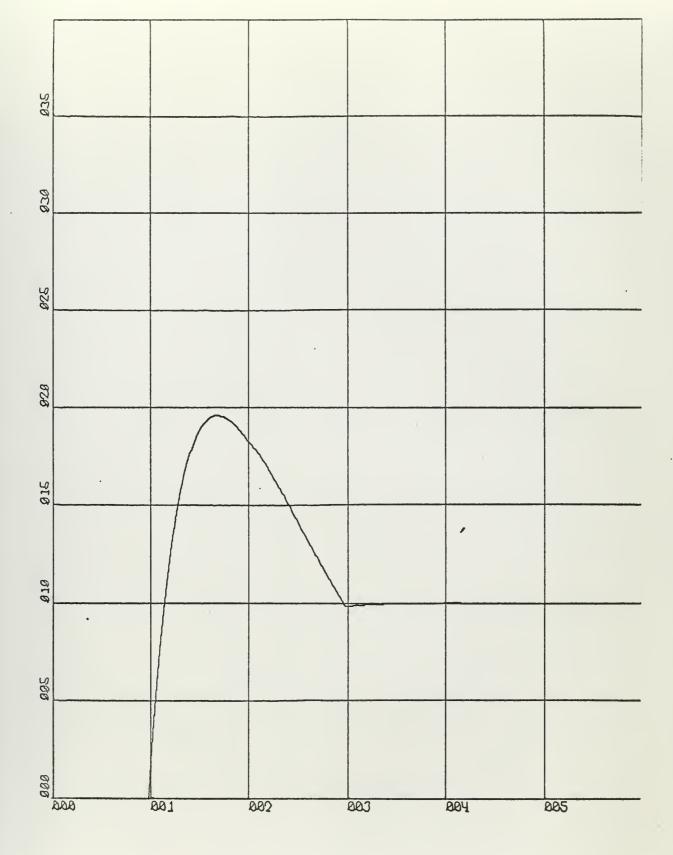

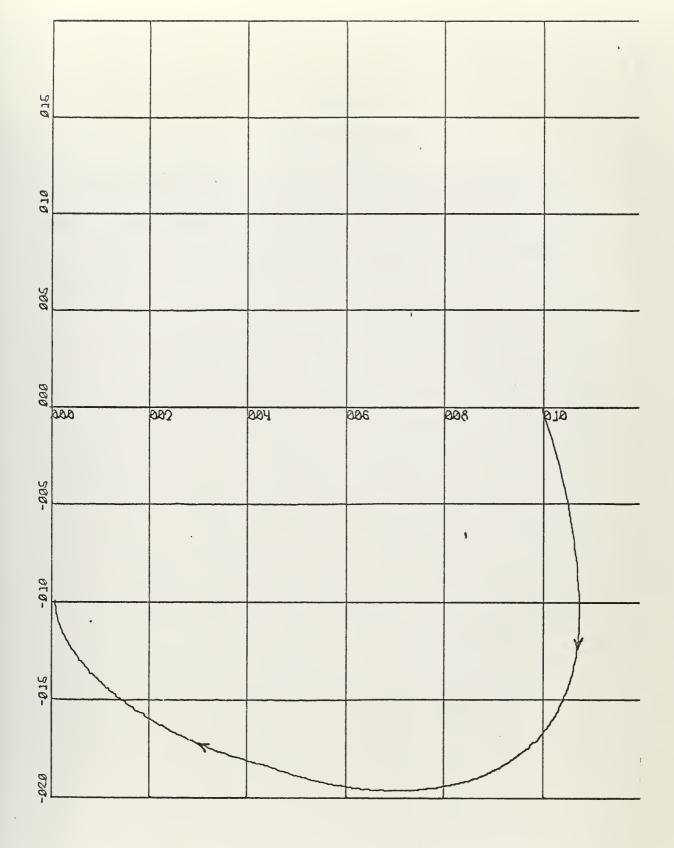

The graphical results to the simulation are on the following pages and do verify the design theory as well as the computations involved.

(Appendix I contains graphical results for a unit ramp input as well as results for a type zero system in response to both unit step and ramp inputs.)

It should be mentioned that a certain degree of accuracy is needed in the determination of the h's used. In some simulations, the rounding of the h value to two decimal places resulted in a response that was slightly less than optimum.

X-3 CALE = 1.00E-01 UNITS/INCH. Y-3 CALE = 2.00E-01 UNITS/INCH. BROWNE DIGIT 1

RUN 1

OUTPUT US. TIME

X-3CALE - 1.80E-81 UNITS/INCH. Y-3CALE - 2.80E+88 UNITS/INCH.

BROWNE DIGIT 1

RUN 1

VELOCITY US.TIME

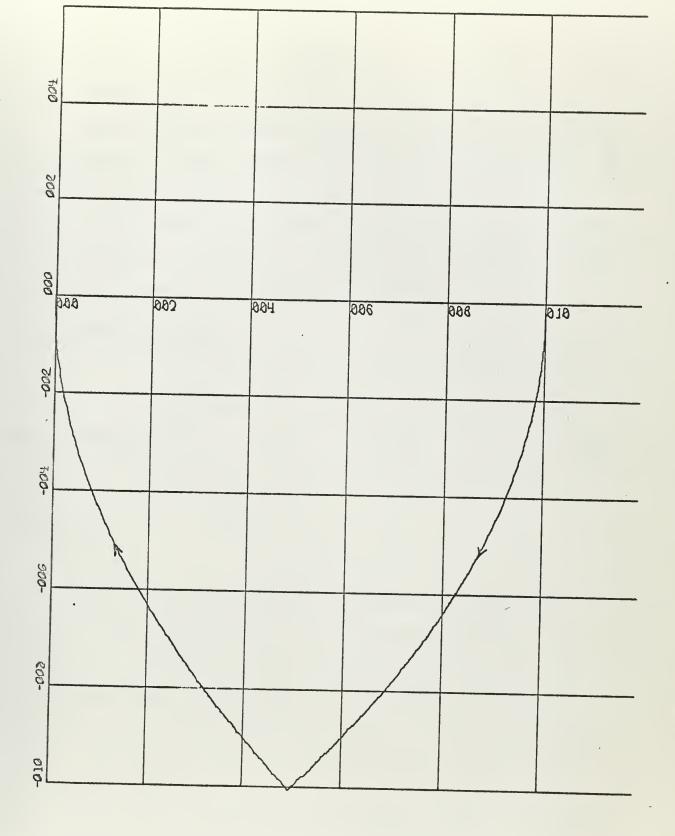

X-SCALE = 2.88E-81 UNITS/INCH.

Y-SCALE = 2.88E+88 UNITS/INCH.

BROWNE DIGIT 1

RUN 1

EDOT US ERROR

## 2.0 Investigation

The investigation conducted during the course of this thesis was developmental in nature. Using the variable gain amplifier control theory discussed in Section 1.2, techniques for accomplishing the sampled-data control of a real plant were developed. The investigation also included the development of a computer time sharing system through which many systems can be simultaneously controlled.

# 2.1 Theoretical Design

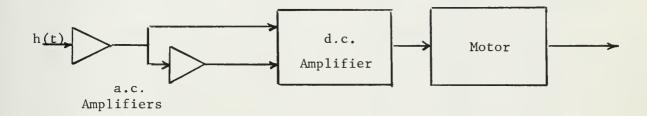

Figure 6

Figure 6 shows the general block diagram of the sampled-data control system that was used. The system breaks down into two main components which are the continuous plant and the D(Z), sampler, and zero-order hold. The continuous plant is described in Appendix III. The CDC-160, CDC-168, and A/D, D/A converters function as the sampler, D(Z), and zero-order hold. This operation will be treated in detail in Section 2.2.1.

The digital controller, D(Z), was designed to give a "deadbeat response" to a step input using the theory described in Section 1.2.

It was decided to solve for the  $K_k$ 's in general terms initially and then substitute the known G(S) determined in Appendix III.

Figure 7 is shown for a generalized  $G(S) = \frac{A}{s(s+\alpha)}$ .

Figure 7

From the flow graph we have

$$x_{1}(s) = \left[\frac{1}{s} - \frac{KA}{s^{2}(s+\alpha)}\right] x_{1}(t_{0}) + \frac{1}{s(s+\alpha)} x_{2}(t_{0}) + \frac{KA}{s^{2}(s+\alpha)} \qquad r(t_{0})$$

$$x_{2}(s) = \frac{-KA}{s(s+\alpha)} x_{1}(t_{0}) + \frac{1}{s+\alpha} x_{2}(t_{0}) + \frac{KA}{s(s+\alpha)} \qquad r(t_{0})$$

and after taking the inverse Laplace transformation we arrive at

$$x_{1} \left[ (k+1)T \right] = \left[ 1 - \frac{KA}{\alpha^{2}} \left( \alpha T - 1 + e^{-\alpha T} \right) \right] x_{1} (kT) + (1 - e^{-\alpha T}) x_{2} (kT) + \frac{KA}{\alpha^{2}} \left[ \alpha T - 1 + e^{-\alpha T} \right] r(kT)$$

$$x_{2} \left[ (k+1)T \right] = \frac{-KA}{\alpha} (1 - e^{-\alpha T}) x_{1} (kT) + e^{-\alpha T} x_{2} (kT) + \frac{KA}{\alpha} (1 - e^{-\alpha T}) r(kT)$$

For  $x_1(0) = x_2(0) \stackrel{\triangle}{=} 0.0$

and for a step input of  $r(0) = r(T) = (2T) \dots \triangleq r$

we have

$$K_{0} = \frac{\alpha}{AT(1-e^{-\alpha T})}$$

$$K_{1} = \frac{\alpha^{2}e^{-\alpha T}}{A\left[e^{-\alpha T}(1+\alpha T)-1\right]}$$

$$h_{0} = \frac{\alpha}{AT(1-e^{-\alpha T})} \Delta r$$

$$h_{1} = \frac{-\alpha e^{-\alpha T}}{AT(1-e^{-\alpha T})} \Delta r$$

where  $x_1$  (2T)  $\stackrel{\triangle}{=}$  r:  $x_2$ (2T)  $\stackrel{\triangle}{=}$  0.0

It is seen that a "delta" term is present in the solution for the  $K_k$ 's and the h's. This "delta" term arises from the fact that the error signal was attenuated by a 0.0121 factor before being sent to the A/D converter. This will be discussed in detail in Section 2.2.2. Now for the  $G(S) = \frac{40}{s(s+3)}$ ; T = 0.3; where  $r \triangleq 5.0$  we arrive at:

$$K_0 = 0.421$$

$K_1 = -0.398$   $h_0 = 0.0252$   $h_1 = -0.0102$

The h's computed were used in an earlier trial program. The computed  $K_k$ 's were used in the final control program and as such were entered directly in the computer. The CDC-160 together with the CDC-168 were programmed to serve as the digital controller using these  $K_k$ 's. The CDC-160 also operated as the sampler since the sampling period was also programmed into the computer.

The real system response was also simulated using the same simulation scheme as Section 1.3. The simulation results are in Section 2.3.

After controlling the real plant in a "deadbeat response" manner, it was decided to work on a time sharing routine for optimum control of two plants. The second plant was an analog simulation set up on the EAI TR-20 analog computer with a G(S) equal to  $\frac{1}{s(s+1)}$ . The CDC-160 was then used to provide optimum control to both systems. The design of the digital controller for the second plant followed the same theory used before.

#### 2.2 Development of Sampled-Data Control Technique

The step from the theoretical control solution to a working sampled-data controller involves the development of methods through which the requirements of the theoretical solution may be implemented in a real controller. This is a two-fold development involving the software of computer programming and the associated hardware requirements. Development in each area will be discussed in detail.

# 2.2.1 Hardware Development

Having developed, theoretically, the performance of the D(Z) portion of the control system block diagram, it was necessary to develop a hardware equivalent to the previously described mathematical model of D(Z). To accomplish this hardware development, the following equipment was used:

- (1) A two-channel digital to analog converter. (D/A)

- (2) A four-channel analog to digital converter. (A/D)

- (3) A Control Data Corporation 160 computer, in conjunction with a Control Data Corporation 168 arithmetic unit.

- (4) Operational amplifiers used for summing of signals coming in and out of the converter units.

The equipment used was chosen, not because it was thought to be most efficient for the desired tasks, but because it was readily available in the Digital Control Laboratory of the U. S. Naval Postgraduate School. Comments on the relative merits of the equipment in performing these tasks will be included where appropriate.

Development of the hardware equivalent of the mathematical model of D(Z) will now be discussed. It was decided immediately that the need

for analog hold circuits could be eliminated by replacing them with more accurate computer programmed holds. This is possible because of the operating characteristics of the converter units in conjunction with the 160 computer. First, the 160 computer can sample a converted digital input only when specifically commanded, and then it samples only one value. Similarly, the 160 computer can output a digital value for conversion only upon command, and furthermore, that value remains constant in the output register until it is changed by inserting a new value. Thus, by programming the computer to sample converted analog inputs and provide digital outputs for conversion at specified time intervals, hold circuits become unnecessary. In fact, the holds become an inherent part of the sampling rate of the computer and are varied automatically as the sampling rate changes.

Examining Figure 6, one sees that the input to D(Z) is the error signal, e(t), which is the sum of the reference signal, r(t), and the negative control signal, -c(t). There are two methods by which e(t) may be transmitted to the computer. The first method is to sample r(t) on one channel of the A/D and to sample -c(t) on another channel. The two inputs could then be summed in the computer to obtain the error signal. This method was discarded for two reasons. First, since it is impossible to sample r(t) and -c(t) simultaneously, the error signal computed would have some inherent error. Second, the A/D conversion time is of the order of 120 microseconds, and it was felt that this additional time delay might become prohibitive at sampling rates approaching 0.1 seconds.

The second method of supplying the error signal to the computer, and the one which was adopted, involved summing r(t) and -c(t) in an operational amplifier prior to transmission to the A/D. This method has the advantage of being fast, accurate, and readily adaptable to a restriction imposed by the physical characteristics of the converter unit. This restriction is that the converter units accept only negative voltages in the range of zero to minus ten volts. Thus, to handle both positive and negative values of e(t), the sum of r(t) and -c(t) is added by means of an operational amplifier to minus five volts. A zero error signal would then be sampled by the computer as an input of minus five volts, and an error signal of three volts would be sampled by the computer as an input of minus two volts. Similarly, the converted D/A value which is transmitted to the amplifiers of the system must be added to five volts prior to insertion in the system.

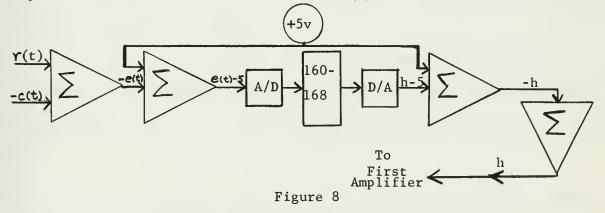

A block diagram of the hardware system used to provide the equivalent to the mathematical model of D(Z) is shown below:

With the above hardware system established, the rest of the development

of a unit equivalent to the mathematical model of D(Z) must be accomplished by programming the computer.

### 2.2.2 Software Development

Programming the computer to accomplish the aforementioned task was done in a progressive fashion, starting with programs to accomplish the simplest control functions and expanding the basic programs to provide for accomplishing more complex tasks. This was done for two reasons. The primary reason was that at the outset the authors wanted to isolate quickly any faults in the digital control system, and to analyze carefully system response at each stage of control function complexity. A secondary reason for adopting this progressive programming technique was the fact that the 160 computer is rather limited in its capability. Due to this limitation, the authors desired to bring the control capabilities of the equipment used to a maximum before computer saturation problems were encountered. Following is a discussion of these progressive programs.

The first program written was intended primarily to check the operation of the hardware equivalent of the D(Z) under minimum capability requirements, and also to check the plant response with the D(Z) in the

The 160 has limited storage capacity (4K), and a relatively slow memory cycle (6.4 microseconds). It can only multiply or divide in conjunction with the 168 and the 900 microsecond time for such operations is quite slow.

loop. The essence of Program 1 is to enable the plant to run as a continuous system with the D(Z) block in the loop. Mathematically, such a system may be described as D(Z) = 1, and the sampling period, T, approaching zero (approximately 200 microseconds).

The programming aspects of Program 1 were quite simple. The program was an iterative loop in which the current error signal was sampled from the A/D converter, read into the computer, stored temporarily, and output to the D/A converter for return to the system. A flow chart for Program 1 is shown below. A complete text of Program 1 is presented in Appendix VI.

The results of the test using Program 1 were quite satisfactory. System responses were obtained from step, ramp, and sinusoidal inputs, and these responses matched those obtained from the system when operated as a purely continuous system with unity feedback. This, of course, was predictable with D(Z) = 1., and T approaching zero. However, the results do validate the selection of hardware used to implement the realization of the mathematical D(Z).

The results of Program 1 opened another avenue of approach to the problem of implementing the variable gain samplifier method of digital control. It was noted, when working with the system in the Digital Control Laboratory, that the system was subject to many random inputs of small magnitude from various sources of noise. Program 1, when tested, maintained stability, and accurate and fast response in the presence of these noise sources. It was further noted that the advantages of the variable gain amplifier method in regard to minimum time response are lessened when the inputs are small and random.

In the light of the foregoing facts, a <u>temporary</u> control philosophy was developed. This philosophy states that for step inputs which exceed in magnitude a threshold, a standard variable gain amplifier control solution would be employed. For small inputs, such as noise, the system would be controlled as it was with Program 1. The threshold would be set at a level which would prevent the implementation of a solution of the type described in Section 1.2 for the random noise inputs, which were restricted to a relatively low magnitude. In other words, the

system would run in an essentially continuous mode D(Z)=1, until receipt of a valid step input, at which time it would be controlled by a variable gain amplifier digital solution.

To implement this type of control philosophy, an intermediate program, Program 2, was written to modify Program 1 to provide for detection of a definite step input and an exit to a solution. This detection is accomplished by comparing the new value of the sampled error signal with the immediately preceding value of the sampled error signal. If the difference between these values is greater than the established threshold, a step input is detected. To assist the reader in understanding the programming procedure for determining the sign of a detected step input, the following table of octal number values for analog voltages into the converter is presented:

| ANALOG         | OCTAL  |

|----------------|--------|

| VOLTAGE        | NUMBER |

|                |        |

| 0              | 4000   |

| -1             | 4632   |

| -2             | 5463   |

| -3             | 6314   |

| -4             | 7144   |

| <b>~</b> 5     | 0000   |

| -6             | 0631   |

| <del>-</del> 7 | 1463   |

| -8             | 2314   |

| -9             | 3144   |

| -10            | 3777   |

A flow chart for Program 2 is presented on the following page. A complete text of Program 2 is presented in Appendix VI.

The results of Program 2 were excellent. It proved to be a fast and accurate method of sensing step inputs having a magnitude greater

Figure 10

than the threshold level. In one sense Program 2 was too sensitive.

When certain knife switches were used to provide zero to five volt step inputs, negative transients appeared at the instant the switch was thrown. Program 2 was so sensitive that it sensed the transient as a negative step input. This imposed the requirement that step inputs be obtained from an electronic switching device or from a high quality knife switch which eliminates the aforementioned transient.

The next step in the development of the <u>temporary</u> control philosophy involved utilizing the computer in a real time mode to implement a variable gain amplifier solution. The iterative loop of Program 2, which maintains continuous control until a step input is sensed, employs the computer in a free-running mode. The variable gain amplifier solution, however, requires that the computer insert control voltages of definite real time length into the system. To do this, the computer must output a control voltage to the system, hold the voltage for a specified length of time, and then output another control voltage. Program 3 was written to develop techniques for accomplishing this task.

Program 3 was a simple program which called for the computer to output a given voltage, delay through a timing chain, and output another voltage. Theoretically, the length of the delay could be calculated from the execution time for the instructions which constitute the timing chain. However, exact timing data for D/A conversion were not available. Therefore, approximate timing chain delay was calculated and adjusted by experimental results for exactness. The timing chain was formed by constructing an iterative loop in which an index was increased by one on each pass and compared to a preset total. When the index equaled the

preset total, the time delay was complete. A flow chart for Program 3 is shown on the following page. A complete text of Program 3 is presented in Appendix VI.

In testing Program 3, it was decided to design a basic delay block of 0.1 second. With an accurate delay block established, delays which were integer multiples of 0.1 second could be achieved by iterating through the basic delay the required number of times. Delays of less than 0.1 second could be achieved by setting the preset total at a proper fraction of that required for a 0.1 second delay.

Satisfactory results were obtained from Program 3 in that a delay of exactly 0.1 second was produced between the output of the first and second voltages. For this delay, the preset total was set at 3403<sub>8</sub>. Results were checked on a high speed Mark II Brush Recorder and an oscilloscope.

Having developed Programs 2 and 3, the basic tools for implementing a solution within the constraints of the <u>temporary</u> control philosophy were ready. By using Program 2 to maintain continuous type control in the absence of an input signal and to sense a step input, and by employing the features of Program 3 to output the required controlling voltages, the desired solution to a step input may be attained. To test the basic validity of their approach, the authors wrote Program 4 as a first trial of the variable gain amplifier control method.

Program 4 was an unsophisticated approach which started with the system being controlled in the undisturbed state by Program 2 which will hereafter be referred to as the Sense Loop. When an input is sensed, h

Figure 11

is transmitted immediately to the system.  $h_{o}$  is held for one sampling period, and then  $h_{1}$  is transmitted and held for one sampling period. At the completion of the second sampling period, the system returns to

continuous operation as the computer returns to the Sense Loop. To insure a return to the continuous mode of operation at the completion of the second sampling period, it was necessary to "bootstrap" the Sense Loop by sensing the current error and inserting it in the Sense Loop as the "old value". Were this procedure not followed, an imperfect solution, one which did not have zero error at the end of two periods, would cause the Sense Loop to sense another step input and thus cause the system to go into unstable, erratic operation.

The unsophisticated aspect of Program 4 stems from the fact that the h's were not computed by multiplying e(t) by K during the solution, but were pre-calculated and inserted in memory as constants to be transmitted to the system at the proper time.  $K_0$  and  $K_1$  have been determined in Section 2.1.  $h_0$  was simply  $K_0$  times  $e_0(t)$ , and  $h_1$  was  $K_1$  times  $e_1(t)$  (predicted). Due to the fact that r(t) and -c(t) were transmitted to the summing operational amplifier after passing through dropping resistors in the front end of the system, the magnitude of the error signal was considerably decreased. For a five volt step input,  $e_0(t)$  sensed by the computer was 0.0600 volts and predicted  $e_1(t)$  was 0.0258 volts. On the basis of these values,  $h_0 = 0.0252$  volts and  $h_1 = -0.0102$  volts. A 0.3 second sampling interval was used.

A flow chart for Program 4 is shown on the following page. A complete text of Program 4 is presented in Appendix VI.

Complete results of the responses obtained when using Program 4 will not be presented because these tests were in the nature of feasibility checks. The results may be summarized by stating that they provided

## Program 4

Figure 12

definite proof of the validity of the variable gain amplifier approach, and led the authors to adopt certain techniques which were used in later programs to improve performance. Some of these lessons learned from these tests will now be discussed.

Accuracy problems were caused by the small magnitude of the error signal received at the D(Z) portion of the system for a five volt step input. Due to this fact, the magnitude of h's to be transmitted to the first amplifier was so small that the resolution of the D/A converter prevented sufficient accuracy for these h's. The resolution for the converter is 0.0024 volts per octal number. With h's of the magnitude of 0.02 volts, accuracy was limited to the first digit of the h. This condition was barely satisfactory due to the stringent demands of the variable gain amplifier method for accuracy in the h's. This demand was demonstrated when solutions were simulated on a general purpose digital computer. This demand was discussed more thoroughly in Section 1.3.

To correct the problems associated with converter resolution, the obvious solution was to increase the voltage levels in and out of the converter. The simplest method of accomplishing this would have been to eliminate the dropping resistors before the summing amplifiers. However, when this was tried, system noise increased to a level which was not tolerable. The method of achieving increased accuracy, which produced the best results, was to multiply the error signal by ten in the summing operational amplifiers prior to A/D

conversion, and to divide the D/A converted voltage by ten in the summing operational amplifiers before transmittal to the system. This enabled the use of h's of ten times computer value for conversion which alleviated the resolution problem. This scheme also maintains operation in the continuous mode of the Sense Loop to continue as before. For all further tests, the hardware shown in Figure 8 was modified to provide for the proper multiplication and division in the summing operational amplifiers.

A second lesson learned in this test program related to the "bootstrap" procedure discussed previously. This feature was originally inserted in the program to prevent system runaway for incorrect solutions resulting from tests using improper h's. It was found, however, that this "bootstrapping" return to continuous operation at the completion of the second period was an integral part of a satisfactory solution. This is due to the fact that a real system has inherent non-linearities such as coulomb friction and backlash. In view of these non-linearities, a perfect theoretical solution can not be obtained. (It is possible to approach more closely the perfect solution by slight modification of the size of the h's.) Thus, a rapid, smooth return to the continuous mode after the second sampling period is essential to a satisfactory solution. It is noted that by properly adjusting the size of the h's, the error at the end of the second sampling period is small (less than 10% of the step size), and the use of the continuous mode reduces error to zero rapidly. Specific examples of the foregoing may be noted in the presentation

of results in Section 2.3. At that time, the reader may note that the necessity to go to the continuous mode to bring error to zero does not significantly degrade system performance in comparison to a theoretical solution.

With the information derived from Programs 1 through 4, the authors developed Program 5 which was intended to culminate efforts in the development of the <u>temporary</u> control philosophy. Program 5 was a generalized version of Program 4, the primary difference being that in the newest program the h's were computed during the solution instead of using precomputed values. The solution technique may be summarized by stating that each h is computed by sampling current error and multiplying by the appropriate gain constant  $(K_k)$  by using the CDC-168 arithmetic unit in the multiply integer mode in conjunction with the CDC-160 computer.

Programming arithmetic operations for these two units is quite straightforward when Subroutine Arith, written by Professor M. L. Cotton, is used. However, the characteristics of the CDC-168 required manipulation of the sensed error signals. Specifically, for an arithmetic operation, the 168 requires two 22-bit operands, and supplies a 22-bit solution. Each operand is composed of two 12-bit 160 words, with the least significant half of the number in an even numbered cell and the most significant half of the number in its odd numbered mate. The first bit in each cell pair is a sign bit. It is this sign bit in the first bit of each of the two words composing the operands that require the manipulation. For the K multipliers which remain constant, proper values may be inserted into both storage cells

manually before the program runs. However, for the sensed error signal, negative numbers received from the converter create a problem. For the 168 to function properly, the sign bits for both portions of the operands must agree. To handle this problem, the following procedure was employed. To derive the proper h, the product of  $K_k$  and e(t)is required. After e(t) is sensed, it is placed in cell 0024 as the least significant half of an operand. The most significant half, cell 0025, is preset to zero. For negative step inputs, the error signals read in from the A/D converter are positive numbers, and the multiplication process may proceed immediately. For positive step inputs, however, the error signals sensed from the converter are all negative numbers. To maintain sign bit consistency with cell 0025, this negative number is complemented and placed in cell 0024. multiplication operation then proceeds. The product, of course, is of the wrong sign so it must be complemented prior to being transmitted to the system. This procedure will be defined completely in the flow chart for Program 5.

The other major innovations of Program 5 involved attempts to obtain greater accuracy in the solution and maintain high resolution in the converter. As previously discussed, the multiplication and division by ten in the operational amplifiers were included. To achieve greater accuracy in computing the h's, 100 times  $K_k$  was set in the computer as the multiplying constant. The products were then divided by 100 prior to being output to the D/A.

As before, a sampling interval of T = 0.3 seconds was used. The gain constants for this system were computed to be:  $K_0$ =0.421 and  $K_1$  = -0.398. A flow chart for Program 5 is shown below. A complete text of Program 5 is presented in Appendix VI.

Figure 13 (continued)

Figure 13 (continued)

As noted before, Program 5 marked the culmination of efforts in conjunction with the <u>temporary</u> control philosophy. Although the results of Program 5 were good, and gave valuable insight into digital control technique, Program 5 was merely a vehicle through which the validity of variable gain amplifier theory could be tested. The <u>temporary</u> control philosophy, although perfectly satisfactory for control of a single system, is unsatisfactory as a general philosophy for digital control because it excludes utilization of one of the primary advantages claimed for digital controllers: simultaneous control of many systems by the same computer. The authors believe that the realistic application of digital control methods is closely tied to the capability for simultaneous control of many systems.

Toward this end, a final control philosophy was developed.

The goal of this final control philosophy was to achieve this simultaneous control. This goal implies that the computer be "time-shared" among the systems to be controlled. Therefore, the significant difference between the <u>temporary</u> and <u>final</u> control philosophies is one which enables the computer to time-share its control function.

Before discussing the <u>final</u> control philosophy in detail, specific performance goals for this philosophy will be discussed. The authors wanted to develop techniques for controlling two or more systems simultaneously by employing one digital computer on a time-share basis. The control was to be achieved by the variable gain amplifier method. To achieve generality, it was desired to include

the capability for the systems to be controlled at different sampling rates. Furthermore, it was considered necessary to maintain the capability to handle simultaneous step inputs to each system without performance degradation.

It may be recalled that the <u>temporary</u> control philosophy called for a return to a free-running "continuous" mode at the completion of the solution. The major difference in the <u>final</u> control philosophy is that at the completion of the second sampling period, the computer returns to a mode in which D(Z) is still 1.0, but instead of a sampling interval approaching zero, a sampling period of definite finite length is employed. Although this innovation does not change the response characteristics of the control solution, it marks the change from a partially discrete, partially continuous system, to one which is completely discrete. It is this change which enables the development of the required time-sharing computer operation for multiple control.

Having discussed the major difference in the control philosophies, the <u>final</u> control philosophy will be covered in detail. As before, with no signal input to either system, the computer resides in a Sense Loop. In the Sense Loop each system under the control of the computer is sampled and tested for a step input. If a step input greater than a threshold is not detected, the exact signal sampled is returned to the system. (D(Z) = 1.0) Each of the systems under control is handled in this fashion. When all systems have been sampled, the computer goes through a basic delay. This basic delay

is so named because it is a building block for all delays required for implementing variable gain amplifier solutions of any length on any system controlled by the computer. All required solution delays are formed as integer multiples of the basic delay. It is noted that the basic delay is much longer than the time required to sample and test all systems being controlled.

When a step input is received by one of the systems, an error flag for the appropriate system is set and the computer exits from the Sense Loop to a Solution Routine. In the Solution Routine, the first control voltage for the flagged system is transmitted from the computer, and all other system flags are checked for possible simultaneous step inputs. If not, the computer goes through one basic delay and then senses all other systems for possible step inputs. no other systems have received signals, the computer returns to the start of the Solution Routine and begins to count the number of times the basic delay has been entered. After each pass through the basic delay, all other systems are checked for possible step inputs. When the pass count reaches a number which indicates that the first control voltage has been in the proper length of time, the computer computes and outputs the second control voltage, and a new pass count begins. If, at any time during the solution, another system receives a step input, it is flagged, and on the next pass through the Solution Routine, a solution similar to the one explained above is begun.

When a variable gain amplifier solution for one of the systems is completed, the computer jumps to a Return Routine. In this Return

Routine all counters for the appropriate system are zeroed and the error flag is set to zero. The system is then bootstrapped by the procedure previously explained, and returned either to the Sense Loop or the Solution Routine, if the error flag of another system is set. In any case, after being bootstrapped, the system returns to a mode in which the characteristics of the control function are D(Z) = 1.0, and T = the basic delay.

The characteristics of the  $\underline{\text{final}}$  control philosophy may be summarized by stating that any single system which is being controlled operates in a state in which D(Z)=1.0, and T= the basic delay when there is no step input above the threshold level. Thus, for small step inputs and noise inputs, the system would be controlled in the above mode. When a step input greater than the threshold level is received, a variable gain amplifier solution is executed and the control mode then returns to that specified above. In the time sharing mode, each system controlled is operated in this same manner, with the option of making the solution sampling period any integer multiple of the basic delay.

To test the <u>final</u> control philosophy, Program 6 was written. For purposes of this test, two systems were time-shared. One of the systems used was the real system used in previous tests. The second system was an analog simulation of a plant having the following characteristics:  $G(S) = \frac{1}{\hat{s}(s+1)}$ . The basic delay was established as 0.025 seconds. The solution sampling rate for the real system was 0.3 seconds; for the analog system, 1.0 seconds. The only

restriction for Program 6 was that it was written to control only two systems simultaneously. The basic delay time may be chosen arbitrarily, and the solution sampling rates may be any integer multiple of the basic delay. Computation of  $h_0$  and  $h_1$  was accomplished in the manner of Program 5. The hardware arrangement for the real system was the same as that employed in conjunction with Program 5, and the summing amplifier arrangement in and out of the converter for the analog system is identical to that of the real system.

A flow chart for Program 6 is shown on the following pages. It is broken down into three sections: Sense Loop, Solution Routine, and Return Routine. A complete text of Program 6 is presented in Appendix VI.

To simplify the flow chart for the Solution Routine, the negative step solution for System 1, and the positive step solution for System 2 have been omitted. The omitted processes are identical in form to those shown. Furthermore, the "D/A  $h_k$ " blocks, shown in the flow chart as predefined processes are handled exactly as in Program 5.

Before presenting the flow chart for the Solution Routine, the following indices are defined:

- I = the number of passes through the basic delay for the current h for System 1.

- J = the number of h's transmitted to System 1.

- P = the required number of passes through the basic delay to achieve the specified variable gain amplifier solution sampling rate for System 1.

- K = the number of passes through the basic delay for the current h for System 2.

- L = the number of h's transmitted to System 2.

- Q = the required number of passes through the basic delay to achieve the specified variable gain amplifier solution sampling rate for System 2.

The flow chart for the Solution Routine is shown on the following page.

Program 6

## SOLUTION ROUTINE

The Return Routine is shown on the following page. The Return Routine will be shown for System 1 only. That for System 2 is identical except for the fact that different indices are zeroed.

## Program 6

## RETURN ROUTINE

Figure 16

# 2.3 Results

The results of Program 6 were excellent. Both systems were controlled with predicted speed and accuracy. The real system response was equivalent to that obtained from utilization of Program 5. It is interesting to note that the system simulated on the analog computer exhibited exact theoretical response to the variable gain amplifier solution. This, of course, is due to the fact that there were no non-linearities in the simulated system. However, the exact theoretical solution obtained does validate the final control philosophy employed.

The time-share program was tested for all possible time combinations of step inputs to the two systems. In no case was system response degraded once the solution was started. In the worst case, there was a 25 millisecond delay between a step input and the start of a solution. This occurred when a step was entered just as the computer started a pass through the basic delay in the Sense Loop. The delay, in this worst case, which is a random occurrence, was not discernable on the Mark II Brush Recorder used to measure response.

On the following pages, the response curves for the two systems controlled in the time-share mode by Program 6 are shown. Also shown are the theoretical response curves for the real system.

## 2.4 Extension of Results

Due to the limitations imposed by the D/A, only two systems could be simultaneously controlled in the Digital Control Laboratory. To fully substantiate the validity of the <u>final</u> control philosophy, one must consider the feasibility of this philosophy in controlling more

R-SCALE = 2.00E-01 UNITS/INCH.

Y-SCALE = 1.00E+00 UNITS/INCH.

BROWNE E.R. REAL SIM

RUN 1 OUTPUT VS TIME

X-SCALE - 2.00E-01 UNITS/INCH. Y-SCALE - 5.00E+00 UNITS/INCH.

BROWNE E.R. REAL SIM RUN 1 VELO

VELOCITY US TIME

X-SCALE - 1.0 00 UNITS/INCH.

Y-SCALE - 5.00E+00 UNITS/INCH.

BROWNE E.R. REAL SIM

RUN 1 EDOT US ERROR

Figure 20 Real System

Upper Graph Velocity vs. Time; Lower Graph Position vs. Time

Figure 21 Analog Simulation

Upper Graph Velocity vs. Time; Lower Graph Position vs. Time

than two systems. Let us consider this feasibility with respect to the equipment used throughout the laboratory tests, assuming only that the number of channels in the converter may be arbitrarily expanded. (The authors feel that the problems associated with more difficult tasks in the computer field are too often dismissed with a bland inference that a bigger, faster computer can do any job. The dollar economics of the control problem preclude this approach.)

Using Program 6 as a basis for time-sharing control of many systems, the CDC-160 has sufficient memory capability to handle 12 systems simultaneously. By sub-routinizing wherever possible, this number could probably be increased to 15. For 15 systems, however, the sampling time, governed primarily by the analog to digital conversion time of 120 microseconds, becomes an appreciable proportion of the basic delay time. In the Sense Loop, for example, the time to sample A/D, check for step inputs, and return D/A would be approximately two milliseconds compared to the 25 milliseconds of the basic delay. This added delay in the Solution Routine would produce significant errors in the variable gain amplifier solution. If the basic delay could be satisfactorily increased to 50 or 100 milliseconds, the two milliseconds required to sample the 15 systems would become insignificant and not seriously degrade the solution. The authors feel that employment of a 50 or 100 millisecond basic delay, which limits the fastest solution to a step input to 100 or 200 milliseconds, is not unreasonable in most practical applications.

The foregoing discussion has made one tacit assumption. That assumption is that the number of simultaneous inputs is limited to three

of the 15 systems. This is due to the 900 microsecond multiply time required by the CDC-168. This, of course, excludes the desired generality for handling any step input at any time for any system. With the equipment used, the 160 in conjunction with the 168, there is no way to compensate for this problem.

At this point it is worthwhile to look at the advantages of using a different computer. Specifically, the CDC-160A would adequately solve the problem mentioned above. The 160A is a computer quite similar to the 160 in all respects with the additional capability for fast multiplication and division. Economically, the 160A is comparable in cost to a 160-168 tandem, and makes a much more compact unit.

On the basis of the foregoing tests and theoretical extension, the authors feel that with a small, relatively inexpensive computer, such as the CDC-160A, it is quite feasible to control up to 15 systems simultaneously. The control capability will vary with the capabilities of the brand and type computer selected. The main thesis, however, is that an excellent, multi-system, digital control scheme may be implemented without going to the larger general purpose computer.

#### CHAPTER III

# 3.1 Conclusion

It was noted in the Introduction that the basic goals of this thesis were the controlling of hardware by digital methods, and the developing of techniques for implementing time-sharing control of many systems from the same computer. The results obtained have been detailed. In this section the most important findings will be summarized and their relevance to the general feasibility of digital control systems will be noted.

The most significant aspect of controlling the hardware was the necessity for going to the "continuous" mode (D(Z) = 1). and a small T) to bring the error to zero at the conclusion of the solution to a step input. This characteristic, caused by the non-linearities of the system, would seem to be a significant disadvantage to this type control. However, this was not the case. In the worst case, the servo position was within ten percent of the desired final position at the moment of the switch to the "continuous" mode. Furthermore, at the switch time, the servo velocity was in the proper direction at a decreasing magnitude. This condition permitted the system to settle rapidly to the desired position.

Of course, to realistically evaluate this control method, one must establish a performance criterion as the basis for comparison with other control methods. The criterion selected was one which measured minimum time to reach a position within ten percent of final value and

to remain within this ten percent boundary while settling. On the basis of this criterion, the time for a unity feedback continuous system to meet the conditions was 1.2 seconds, and 800 milliseconds with the addition of optimum tachometer feedback. These figures were obtained with the amplifier gain potentiometers set at the same levels used for the digital operation. By increasing the amplifier gains, a time of 500 milliseconds was obtained with tachometer feedback. Using a variable gain amplifier solution sampling rate of 300 milliseconds, a time of 600 milliseconds was required to meet the criterion. relatively low saturation level of the amplifiers precluded the use of sampling rates of 100 or 200 milliseconds, but on the basis of responses obtained at rates of 300, 400, and 500 milliseconds, it follows that improved amplifiers would allow a solution time of 200 milliseconds. In general, the fastest speed of response obtainable by the variable gain amplifier method is limited by the saturation level of the amplifiers. Similarly, the response speed obtainable by a bang-bang technique is limited by this saturation level.

On the basis of these results, the performance characteristics of the digital control method indicate that this method is competitive with other control methods. With improved amplifiers, response speeds from the digital methods can be much faster than those obtainable from continuous methods. Optimum bang-bang techniques approach the response speeds obtainable with the variable gain amplifier method.

There are, of course, many criteria by which control systems

may be judged. The criterion above is one of speed of response.

Although other criteria were not evaluated, it is noted that the digital technique is, in general, quite adaptable. For example, the basic hardware and software employed by the authors is readily adaptable to a criterion which calls for minimum fuel expenditure.

The results of the time-sharing program have been fully discussed and the feasibility of extending the program to control many systems has been outlined. The basic approach of utilizing a small computer has precluded a discussion of a further extension of the technique. That is, using a large, general purpose computer as the digital controller, with other computing tasks being time-shared with the control function. This is feasible with no change in the basic program heretofore used in conjunction with the CDC-160. In examining this program, one can readily see that the vast majority of time is spent in the basic delay block. Time spent in the basic delay is ideal for carrying out other computing tasks. This could readily be implemented on a general purpose computer with a real time clock and interrupt capability, and an executive routine to direct the proper sequence of computing tasks not associated with the control task. The ramifications of this large computer capability are indicated by Slaughter and Lackowski in a paper presented to the 1963 National Convention on Military Electronics in which they state: "In those cases in which a digital computer is available, digital control requires less hardware than does conventional control." 4 The presumption accompanying this

statement was that the digital computer was required for other tasks, and the controlling tasks could be satisfactorily time shared.

In view of the performance characteristics of the variable gain amplifier method and the time-sharing capabilities developed, the authors have come to the conclusion that for many applications, digital control methods are presently feasible and superior to other control methods. Due to the present cost of computers, these applications are presently limited to large processes or areas where the advantages of digital control are overwhelming. A specific example of such an application is in large processes such as those in the chemical or petroleum industries in which multiple systems must be simultaneously controlled. Similarly, a single large process with multiple inputs may be controlled by digital methods. A military application would be the extension of the NTDS to include the servo control of gun mounts and missile launchers from the master computer. A final application might be in the aerospace field in which the new techniques for optimum control on the basis of minimizing a given cost function are quite adaptable to digital techniques.

Although immediate feasibility for digital control is limited to processes of the type mentioned above, the decreasing size and cost of digital computers increase their field of application.

The investigation for this thesis was limited in scope to permit the extensive study of a single method. The results from this study may, in general, be extended to other digital control techniques. The authors feel that the results of this study of digital control validate its basic feasibility, and indicate the value of further study in the field.

#### BIBLIOGRAPHY

- Dejka, W. J. and Kershaw, W. V. Digital Sampled-Data Feedback Systems for Shipboard Applications, Progress Report. Navy Electronics Laboratory Research and Development Report 1142, 29 October 1962.

- 2. Jensen, M. E. Optimum Control of a Nonlinear Second-Order Plant Using a General-Purpose Computer. Navy Electronics Laboratory Research and Development Report 1220, 24 April 1964.

- 3. Kuo, B. C. Analysis and Synthesis of Sampled-Data Control Systems. McGraw-Hill, 1963.

- 4. Slaughter, J. B. and Lackowski, D. Digital Control of a Tactical Weapon with a Shipboard General-Purpose Digital Computer.

Conference Proceedings of MIL-E-CON 7 National Convention on Military Electronics, 1963.

- 5. Pearson, M. and Tardif, D. W. Design Analysis and Test of a D. C. Servomechanism Utilizing Direct Drive. United States Naval Postgraduate School, 1959.

- 6. Slaughter, J. B. Quantization Errors in Digital Control Systems. Institute of Electrical and Electronics Engineers Transactions on Automatic Control, v. AC-9, January, 1964: 70-74.

### APPENDIX I

### DESIGN OF DIGITAL CONTROLLERS AND SIMULATION RESULTS

In addition to the design of a digital controller for a step input to a  $\frac{1}{s(s+1)}$  plant, a digital controller for a unit ramp input was also designed. Referring to Figure 1 and Figure 2 in Section 1.2 we arrive at the following equations.

$$T = 1.0$$

$$x_{1} \left[ (k+1)T \right] = \left[ 1 - 0.368K_{k} \right] x_{1}(kT) + 0.632x_{2}(kT) + (0.368K_{k})r(kT)$$

$$x_{2} \left[ (k+1)T \right] = (-0.632K_{k})x_{1}(kT) + 0.368x_{2}(kT) + (0.632K_{k})r(kT)$$

For a unit ramp input r(kT) = k.

$$k = 0; x_1(0) = x_2(0) = 0.0$$

$x_1(T) = 0; x_2(T) = 0$

$$k = 1$$

$$x_1(2T) = 0.368K_1$$

$$x_2(2T) = 0.632K_1$$

To obtain a solution we must set  $x_1(nT)=r(nT)$  and  $x_2(nT)=1$ . We therefore must proceed to the next period in order to solve for the given conditions.

Therefore k = 2

$$\mathbf{x}_{1}(3\mathbf{T}) = \begin{bmatrix} 1 - 0.368 \mathbf{K}_{2} \end{bmatrix} (0.368 \mathbf{K}_{1}) + (0.632)^{2} \mathbf{K}_{1} + 2(0.368 \mathbf{K}_{2}) \triangleq 3.0$$

$$\mathbf{x}_{2}(3\mathbf{T}) = \begin{bmatrix} -0.632 \mathbf{K}_{2} \end{bmatrix} (0.368 \mathbf{K}_{1}) + (0.368)(0.632 \mathbf{K}_{1}) + 2(0.632 \mathbf{K}_{2}) \triangleq 1.0$$

from which

$$K_1 = 3.82 ; K_2 = 0.31$$

and

$$h(T) = 3.82 ; h(2T) = 0.183$$

It should be noted that for this system to maintain a zero error after it has arrived "home" a constant output of h(nT)=1 must be fed into the continuous system. This will keep the system moving at a unit velocity and thus maintain a zero system error.

A digital controller using the same design theory was developed for a  $\frac{1}{(s+1)(s+2)}$  plant in response to both unit step and ramp inputs. The derivations and explanations follow. The procedure used is the same as that in Section 1.2.

Plant:

$$G(S) = \frac{1}{(s+1)(s+2)}$$

Sampling Period: T = 1.0

Block Diagram:

$$\begin{aligned} \mathbf{x}_1 & \left[ (\mathbf{k} + 1)\mathbf{T} \right] = \left[ 2\mathbf{e}^{-\mathbf{T}} - \mathbf{e}^{-2\mathbf{T}} - \mathbf{K}_{\mathbf{k}} \left( .5 - \mathbf{e}^{-\mathbf{T}} + .5\mathbf{e}^{-2\mathbf{T}} \right) \right] & \mathbf{x}_1 (\mathbf{k}\mathbf{T}) + (\mathbf{e}^{-\mathbf{T}} - \mathbf{e}^{-2\mathbf{T}}) \mathbf{x}_2 (\mathbf{k}\mathbf{T}) + \\ & \mathbf{K}_{\mathbf{k}} \left( .5 - \mathbf{e}^{-\mathbf{T}} + .5\mathbf{e}^{-2\mathbf{T}} \right) & \mathbf{r}(\mathbf{k}\mathbf{T}) \end{aligned} \\ \mathbf{x}_2 & \left[ (\mathbf{k} + 1)\mathbf{T} \right] = \left[ 2\mathbf{e}^{-2\mathbf{T}} - 2\mathbf{e}^{-\mathbf{T}} - \mathbf{K}_{\mathbf{k}} (\mathbf{e}^{-\mathbf{T}} - \mathbf{e}^{-2\mathbf{T}}) \right] \mathbf{x}_1 (\mathbf{k}\mathbf{T}) + (2\mathbf{e}^{-\mathbf{T}} - \mathbf{e}^{-\mathbf{T}}) \mathbf{x}_2 (\mathbf{k}\mathbf{T}) + \\ & \mathbf{K}_{\mathbf{k}} \left( \mathbf{e}^{-\mathbf{T}} - \mathbf{e}^{-2\mathbf{T}} \right) & \mathbf{r}(\mathbf{k}\mathbf{T}) \end{aligned}$$

For T = 1.0

$$x_{1} \left[ (k+1)T \right] = \left[ .601 - .1995K_{k} \right] x_{1}(kT) + .233x_{2}(kT) + .1995K_{k} r(kT)$$

$$x_{2} \left[ (k+1)T \right] = \left[ -.466 - .233K_{k} \right] x_{1}(kT) - .098x_{2}(kT) + .233K_{k} r(kT)$$

(I) Let

$$r(kT) = 1.0$$

$k=0$ ;  $x_1(0) = x_2(0) = 0$

$x_1(T) = .1995K_0$ ;  $x_2(T) = .233K_0$

These two equations clearly cannot be solved for the final conditions of:  $x_1(T) = 1.0$ ;  $x_2(T) = 0.0$

Therefore let k = 1

$$x_1(2T) = 0.1742K_0 - 0.0398K_0K_1 + 0.1995K_1 \stackrel{\triangle}{=} 1.0$$

$$x_2(2T) = -0.11575K_0 - 0.0465K_0K_1 + 0.233K_1 \stackrel{\triangle}{=} 0.0$$

from which:

$$K_0 = 3.65$$

;  $K_1 = 6.73$

and

$$h(0) = 3.65$$

;  $h(T) = 1.832$

Note: Since the plant involved is of type zero it will have an inherent steady-state error to a step input. To eliminate this error a "steady state h" will have to be put into the system after the error has been initially reduced to zero. To determine this "steady state h" the final value theorem was used as follows:

Assume:

$$h(t) = at + b$$

$$H(S) = \frac{a}{s^2} + \frac{b}{s}$$

$$x_1(s) = \left[\frac{bs+a}{s^2}\right] \left[\frac{1}{(s+1)(s+2)}\right]$$

$$x_1(\infty) = \frac{d}{ds} \left[\frac{(bs+a)e^{st}}{s^2+3s+2}\right] \qquad s = 0$$

$$x_1(\infty) = \frac{2b+2at-3a}{4} \qquad \triangleq 1.0$$

or

$$a = 0 \; ; \; b = 2$$

$$\therefore h(nT) = 2 \qquad n = 2,3...$$

(II) Now let r(kT)=k i.e. unit ramp

In this case the final values desired are:  $x_1(nT)=k$ ;  $x_2(nT)=1.0$ for n the smallest possible integer.

For:

$$k = 0$$

;  $x_1(0) = x_2(0) = 0$

$x_1(T) = 0$  ;  $x_2(T) = 0$

Therefore let k=1

$$x_1(2T) = 0.1995K_1$$

$$x_2(2T) = 0.233K_1$$

These two equations cannot be solved so we must proceed to k=2.

$$x_1(3T) = 0.17425K_1 - 0.0398K_1K_2 + 0.399K_2 = 3.0$$

$$x_2(3T) = -0.11575K_1 - 0.0465K_1K_2 + 0.466K_2 \stackrel{\triangle}{=} 1.0$$

From which

$$K_1 = 7.85 ; K_2 = 18.71$$

and

$$h(T) = 7.85$$

;  $h(2T) = 8.14$

Again to keep the output equal to the input for this type zero system we must output a "steady state h". From the final value theorem this is:

$$h(nT) = 2n+3 n 3,4,5,...$$

The following pages contain the graphical simulation results for the type one system (G(S) =  $\frac{1}{s(s+1)}$ ) to a unit ramp input and the responses of a type zero system (G(S) =  $\frac{1}{(s+1)(s+2)}$ ) to both unit step and unit ramp inputs.

-ROCALE = 1.00E+A0 UNITS/INCH. Y-SCALE = 1.00E+A0 UNITS/INCH. BROWNE DIGIT 1R  $G(S) = \frac{1}{S(S+1)}$  r (kT) = k RUN 1 OUTPUT VS. TIME

X-SCALE = 1.ADE+AD UNITS/INCM. Y-SCALE = 5.ADE-AD UNITS/INCM.

BROWNE DIGIT 1R

RUN 1

VELOCITY US, TIME

X-SCALE = 2.20E-21 UNITS/INCH.

Y-SCALE = 5.20E-21 UNITS/INCH.

BROWNE DIGIT 1R

RUN 1

EDOT US. ERROR

Figure 29

X-SCALE - 1.00E+00 UNITS/INCH. Y-SCALE - 2.00E-01 UNITS/INCH. BROWNE DIGIT 2

DUNIN 1

VELOCITY US.TIME

X-SCALE = 2.80E-81 UNITS/INCH. Y-SCALE = 2.80E-81 UNITS/INCH. BROWNE DIGIT 2

RUN 1

EDOT US. ERROR

X-SCALE = 1.00E+00 UNITS/INCH. Y-SCALE = 1.00E+00 UNITS/INCH. BROWNE DIGIT 2R  $G(s) = \frac{1}{(s+1)(s+2)}$  r(kT) = k RUN 1 OUTPUT VS. TIME Figure 32

X-SCALE = 1.00E+00 UNITS/INCM

Y-SCALE = 5.00E-01 UNITS/INCM.

BROWNE DIGIT 2R

RUN 1 VELOCITY VS.TIME

X-SCALE = 2.00E-01 UNITS/INCM. Y-SCALE = 5.00E-01 UNITS/INCM.

BROWNE DIGIT 2R RUN 1

EDOT US, ERROR

### APPENDIX II

## SIMULATION PROGRAM

The following pages contain the simulation program used in verifying the digital controller design for a "deadbeat response" to a unit step input. The programs for simulating a unit ramp response are similar.

```

.. JOB127F, BROWNE, E.R.

PROGRAM DIGIT 1

DIMENSION X(30), XDOT(30), C(15)

C(10)=1.0

1 CALL INTEG1 (T, X, XDOT, C)

INPUT=1.0

IF (T-1.*C(1)) 10,11,12

10 HOLD= C(2)

GO TO 14

11 \text{ HOLD} = C(3)

GO TO 14

12 IF (T-2.*C(1)) 11,13,13

13 \text{ HOLD} = C(4)

14 \times DOT(2) = HOLD-X(2)

XDOT(1)=X(2)

ERROR=1.0-X(1)

EDOT=-X(2)

X(3) = ERROR

X(4) = EDOT

C(11) = 50.0

GO TO 1

END

END

```

# BROWNE DIGIT 1 ONE RUN IS CALLED FOR

INPUT DATA RECORD

CRDER OF EQUATIONS = INITIAL TIME = FINAL TIME = STEP SIZE = .0000E+C0 .5000E+C0 .2000E-C3

THE NCN-ZERO CONSTANTS, C(I), ARE C( 1) = .1000E+C0 C( 2) = .1056E+C3 C( 3) = -.9580E+C2

ALL THE INITIAL CONDITIONS ARE ZERO

THE COLUMN HEADINGS AND THE CORRESPONDING VARIABLES ARE

TIME OUTPUT VELOCITY ERROR X( 0) X( 1) X( 2) X( 3)

THE INDIVIDUAL GRAPH TITLES AND THE CORRESPONDING VARIABLES ARE

OUTPUT VS. TIME VELOCITY VS.TIME EDOT VS. ERROR X( 1) VS. X( 0) X( 2) VS. X( C) X( 4) VS. X( 3)

# BROWNE DIGIT 1

| TIME                                                                                                                                | OUTPUT                                                                                                                                   | VELOCITY                                                                                                                                           | ERROR                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| .00000E+00<br>.10000E-01<br>.20000E-01<br>.30000E-01<br>.40000E-01<br>.50000E-01<br>.70000E-01<br>.80000E-01                        | .00000E+00<br>.52624E-02<br>.26980E-01<br>.47048E-01<br>.83365E-01<br>.12983E+00<br>.18633E+00<br>.25279E+00<br>.32909E+00<br>.41513E+00 | .00000 E+00<br>.10507 E+01<br>.20910 E+01<br>.312406 E+01<br>.51502 E+01<br>.61497 E+01<br>.71392 E+01<br>.81189 E+01                              | .10000E+01<br>.99474E+00<br>.9792E+00<br>.95295E+00<br>.91664E+00<br>.87017E+00<br>.81367E+00<br>.74721E+00<br>.67091E+00                 |

| .10000 E+00<br>.11000 E+00<br>.12000 E+00<br>.13000 E+00<br>.14000 E+00<br>.15000 E+00<br>.16000 E+00<br>.17000 E+00<br>.1800 CE+00 | .51083E+00<br>.60598E+00<br>.69565E+00<br>.76495E+00<br>.82897E+00<br>.88283E+00<br>.92662E+00<br>.96044E+00<br>.98439E+00               | .10042E+02<br>.89893E+01<br>.79466E+01<br>.69143E+01<br>.58923E+01<br>.48805E+01<br>.38787E+01<br>.28869E+01<br>.19049E+01<br>.93272E+00           | . 48917E+00<br>.39402E+00<br>.39935E+00<br>.23505E+00<br>.17103E+00<br>.11717E+00<br>.73384E-01<br>.39565E-01<br>.15614E-01<br>.14340E-02 |