**Calhoun: The NPS Institutional Archive**

**DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

1984-06

Using the Control System Design Environment in the design of a data link receiver unit for the Coast Guard HH-65A helicopter.

Fox, F. Sutter

Monterey, California. Naval Postgraduate School

https://hdl.handle.net/10945/19606

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

43.943

# NAVAL POSTGRADUATE SCHOOL

Monterey, California

## THESIS

USING THE CONTROL SYSTEM DESIGN ENVIRONMENT IN THE DESIGN OF A RECEIVER UNIT FOR THE COAST GUARD HH-65A HELICOPTER

by

F. Sutter Fox

June 1984

Thesis Advisor:

Alan A. Ross

Approved for public release; distribution unlimited T217403

SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

| REPORT DOCUMENTATION PAGE                                                                                                                  |                            | READ INSTRUCTIONS BEFORE COMPLETING FORM                       |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------|

| 1. REPORT NUMBER                                                                                                                           | 2. GOVT ACCESSION NO.      | 3. RECIPIENT'S CATALOG NUMBER                                  |

| 4. TITLE (and Substite) Using the Control System Design Environment in the Design of a Receiver Unit for the Coast Guard HH-65A Helicopter |                            | s. TYPE OF REPORT & PERIOD COVERED Master's Thesis June 1984   |

|                                                                                                                                            |                            |                                                                |

| F. Sutter Fox                                                                                                                              |                            | 8. CONTRACT OR GRANT NUMBER(*)                                 |

| Naval Postgraduate School Monterey, California 93943                                                                                       |                            | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |

| Naval Postgraduate School                                                                                                                  |                            | June 1984                                                      |

| Monterey, California 93943                                                                                                                 |                            | 13. NUMBER OF PAGES 165                                        |

| 14. MONITORING AGENCY NAME & ADDRESS(If different                                                                                          | t from Controlling Office) | Unclassified                                                   |

|                                                                                                                                            |                            | 15. DECLASSIFICATION/DOWNGRADING SCHEDULE                      |

16. DISTRIBUTION STATEMENT (of this Report)

Approved for public release; distribution unlimited

17. DISTRIBUTION STATEMENT (of the abetract entered in Block 20, if different from Report)

18. SUPPLEMENTARY NOTES

19. KEY WORDS (Continue on reverse elde if necessary and identify by block number)

Computer-aided design, Data Link Receiver, Control System Design Environment, Microprocessor Controller Device

20. ABSTRACT (Continue on reverse elde if necessary and identify by block number)

This thesis is an attempt to prove the value of the Control System Design Environment by designing a shipboard or ground-based data link receiver to communicate with the data link installed in the Coast Guard HH-65A helicopter. The Control System Design Environment was intended to allow a designer to use a high-level language to describe the required inputs and outputs of a system. This high-level language, the Control System Design Language (CSDL) is translated into a list of primitives by a Pascal (Continued)

## ABSTRACT (Continued)

program, CSDL.PAS. The primitive list is then compiled into assembly language by a FORTRAN program, NEWCSDL.FOR. The final output includes the hardware and software lists to build a controller that meets the designer's specifications. This particular project includes a project design much more ambitious than any previously attempted in the Control System Design Environment.

Using the Control System Design Environment in the Design of a Data Link Receiver Unit for the Coast Guard HH-65A Helicopter

by

F. Sutter Fox

Lieutenant Commander, United States Coast Guard

B.S., United States Coast Guard Academy, 1971

M.B.A., Roosevelt University, 1977

Submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN COMPUTER SCIENCE

from the

NAVAL POSTGRADUATE SCHOOL June 1984 The 13

#### **ABSTRACT**

This thesis is an attempt to prove the value of the Control System Design Environment by designing a shipboardor ground-based data link receiver to communicate with the data link installed in the Coast Guard HH-65A helicopter. The Control System Design Environment was intended to allow a designer to use a highlevel language to describe the required inputs and outputs of a system. This high-level language, the Control System Design Language (CSDL) is translated into a list of primitives by a Pascal program, CSDL.PAS. The primitive list is then compiled into assembly language by a FORTRAN program, NEWCSDL.FOR. The final output includes the hardware and software lists to build a controller that meets the designer's specifications. particular project includes a project design much ambitious than any previously attempted in the Control System Design Environment.

## TABLE OF CONTENTS

| I. INTRODUCTION                                  | 7   |

|--------------------------------------------------|-----|

| II. DATA LINK RECEIVER SPECIFICATIONS            | 11  |

| III. CSDL DESIGN                                 | 30  |

| IV. IMPLEMENTATION                               | 42  |

| V. CONCLUSIONS AND RECOMMENDATIONS               | 51  |

| LIST OF REFERENCES                               | 54  |

| APPENDIX A-CSDL PROGRAM                          | 56  |

| APPENDIX B-CSDL PROGRAM (REVISED)                | 63  |

| APPENDIX C-CSDL.PAS OUTPUT (PRIMITIVE LISTING)   | 70  |

| APPENDIX D-NEWCSDL.FOR OUTPUT LISTING (SOFTWARE) | 82  |

| APPENDIX E-NEWCSDL.FOR OUTPUT LISTING (HARDWARE) | 131 |

| INITIAL DISTRIBUTION LIST                        | 165 |

#### ACKNOWLEDGEMENTS

I wish to acknowledge the help and advice of my thesis advisor, Lieutenant Colonel Alan A. Ross, U.S. Air Force, and my second reader, Captain Bradford D. Mercer, U.S. Air Force. My special thanks and appreciation go to my wife, Bonnie, my son, Darryl, and my daughter, Laurel. Their concern, patience, and support were invaluable to me in my time at the Naval Postgraduate School.

#### I. INTRODUCTION

design of electonic equipment, including microprocessor-controlled equipment, has traditionally been a and money consuming proposition. The design must be worked out manually and paper-tested, changes improvements made, and more paper-testing performed. it appears that the design is feasible, one or prototypes are built and tested. Building prototypes is expensive because they are labor-intensive and fail benefit from economies of scale. The use of computer aided design (CAD) has become more prevalent in many design applications in recent years because of these reasons. One such design and is the Control System Design Environment proposed by Matelan [Ref. 1] and implemented by Ross [Ref. 21.

The Control System Design Environment makes use of the Control System Design Language (CSDL). This high-level language provides the user with a method to describe the inputs and outputs of a controller and specify time constraints for completion of the required tasks. A translator program takes the CSDL problem statement written by the user, tests the syntax, and then generates symbol and variable tables. It also translates the CSDL statements

into a format called the primitives list with the associated parameters and selection criteria. The primitives are used as macro calls to the realization libraries. These libraries are based on families of microprocessors. The original library built by Ross consisted solely of the Intel 8080 family. Recent additions to the realization libraries include the Zilog Z80 by Smith [Ref. 3] and the Intel 8086 by Cetel [Ref. 4].

family of microprocessors is chosen for implementation by the designer and noted in the description. A solution is attempted and if it fails, another family is chosen and another solution is tried. If all families fail, the failure is reported to the user. When there is a success, software is generated to support the hardware, and monitor code is output for the overall control of the system. The automation of these functions makes it possible to rapidly and inexpensively design, build, and test prototypes. The ability to describe the functional specifications of a control process high-level language and let the CSDE provide output in form of hardware and software design can greatly simplify the work involved and thus lower the cost of producing working prototypes.

The application of the Control System Design Environment (CSDE) to the design of hardware and software for controller applications has been explored by a number of

researchers since Ross first designed CSDL. Some of those who have contributed to CSDE include Carson, Cetel, Heilstedt, Pollock, Riley, Sherlock, Smith, Walden, and Woffinden. Their accomplishments and contributions are all recorded in their respective theses. [Refs. 5-13]

The goal of this thesis is to attempt a validation of the Control System Design Environment. This will be accomplished by using CSDE to design a microprocessor-based data link receiver for the data link to be installed in the Coast Guard HH-65A helicopter. Since CSDE was designed to produce process controllers, the production of a data link receiver will demonstrate the flexibility of the Control System Design Environment to handle additional and more complex types of problem descriptions beyond those considered in the original design of CSDE.

This project is a departure both in size and scope from any previous attempt at using the CSDE system. Several researchers have used CSDE to design controllers. Pollock used CSDE to design a fuel injection system for an automobile in 1981 [Ref. 14]. Heilstedt designed digital filters using CSDE in 1983 [Ref 15]. The latest CSDE design is an automatic start sequencer for a jet engine performed by Riley in 1984 [Ref. 16]. The design of a microprocessor-based data link receiver is a much more ambitious application than any of these previous works. It requires the movement of strings of data throughout the system while

watching for keyboard input from an operator. The goal of the project is concerned with the use and abilities of the CSDE and not with producing a working prototype of a unit that will function according to Coast Guard requirements. The data link receiver will be a subset of and not a complete implementation of the Coast Guard requirements and specifications as outlined in the next chapter.

### II. DATA LINK RECEIVER SPECIFICATIONS

Development of systems, including computer systems, can be costly due to the time and effort required to design, build, and test prototypes. The use of the Control System Design Environment can dramatically reduce the time and effort involved in designing a microprocessor system and in producing the associated software. The cost of a system is spread over the number of items produced, and in general, prototypes are produced in small, and thus expensive, quantities. The automation of the design of hardware and software promises to greatly reduce the cost of the design and prototyping portions of new systems development, especially those systems that will be produced in small

An example of a system currently under development was chosen for an implementation under CSDE for this thesis. The U.S. Coast Guard is presently acquiring a new helicopter, the HH-65A. One of the features of the aircraft avionics suite is a data link transceiver which will automatically send and receive flight information data. Unfortunately, there is no compatable transceiver available for use aboard Coast Guard cutters or at air stations. The potential contributions to a wide range of Coast Guard

missions, not to mention the safety of flight ramifications,

make automated communications between Coast Guard

operational units via data link extremely desirable.

It is virtually impossible today for the U.S. Guard to conduct truly covert law enforcement operations with helicopters deployed aboard cutters or based Safety procedures call for a number of emitters to be employed for the duration of the flight. A properly smuggling operation can gain considerable equipped intelligence against the Coast Guard, particularly from voice communications. Voice communications are notoriously susceptible to monitoring with any of a number of relatively inexpensive scanners available in the electronics market. Making such communications protected or secure can deny the smuggler the information contained in the transmissions, but it cannot conceal Coast Guard presence during the critical preliminary search. A system is needed that will allow the passing of safety and other important data between a helicopter and its cutter or air station and, at the same time, lend a higher degree of covertness to the operation. Since the new HH-65A helicopter is being built with a data link capability installed as part of its avionics package. an opportunity to conduct covert law enforcement operations with cutters or air stations. Since the data link can send position and operations information automatically using preselected time periods, the pilots are

relieved of one more duty that distracts from the mission accomplishment.

From the pilots' point of view, a data link capability means that their attention need not be diverted from the normal scan of aircraft instruments, the airspace around the helicopter, and the water or ground over which they are searching. The onboard computer system does many of the navigation functions automatically and, with the installation of data link capability, can make the required operations reports to the controlling Coast Guard unit. a typical mission the aircrew must monitor the UHF and/or HF radios for communications with their controlling unit, the VHF-AM radio for normal communications with FAA facilities and other aircraft, and the VHF-FM radio for communications with vessels. Thus, the pilots must monitor up to four different radios simultaneously while communicating with other members of the aircrew over the internal (ICS). These communications communications system requirements tax the concentration of the aircrew and contributes to their fatigue. The data link can relieve the crew of one duty while enhancing the security of the flight operation.

The Coast Guard Office of Operations sent a memorandum to the Office of Research and Development in June 1983 requesting development of a shipboard version of the data link. The performance standards and specifications listed in

that request have been used as a basis for the functional specifications for the CSDE implementation of this thesis project.

The performance standards and criteria outlined in the request for support specified a "shipboard version of the data link built into the HH-65A helicopter". This language does not reflect the possible use of the data link at a Coast Guard Air Station. This thesis will assume that the design of shipboard equipment will be more than capable of working ashore as well as at sea.

It would be possible to use a commercially available microcomputer for this project. Writing the assembly language software to drive that system would not be too difficult. This approach, however, would provide a software engineering problem without adding anything new to the knowledge base of computer—aided design. It is far more enlightening to attempt the project through the use of CSDE in order to reduce design costs for new systems.

The goal of this project is concerned with the use and abilities of the CSDE and not with producing a working prototype of a data link receiver unit that will function according to Coast Guard requirements. The data link receiver designed using CSDE will be a subset of and not a complete implementation of the specifications listed by the Office of Operations. Because of this, there will be no

effort to fully meet the performance requirements specified in the request for support.

The following is a listing of the requirements and performance standards as stated in the request and describes how each will be addressed in this project.

The data link receiver system:

1. Must operate on all frequencies (selectable)

from HF to UHF (30.000-3**9**9.975 MHz).

Comment: This is outside the scope of the thesis work and will be assumed to have been met.

The point of this thesis is not the solution of interfacing problems with the radio transmitters.

2. Must be compatible with the AN/ARC-182 transceiver on the HH-65A helicopter.

Comment: This is outside the scope of the thesis work for the same reasons as cited in the paragraph above and will be assumed to have been met.

3. Must be compatible with data link system presently installed in the HH-65A. This system, manufactured by Collins, operates at a 300 baud rate with data burst.

Comment: This is central to the design but little information was available for use in this thesis. The details will be addressed later in this section.

4. Must be of the smallest size and weight practicable for installation in CIC/CSC on all flight-deck equipped cutters, up to 200 feet from transceiver and antenna. A remote readout for the pilothouse is extremely desirable.

Comment: The small size and weight should follow from an efficient design. The installation aboard cutters will be assumed as will the solution regarding the distance between transceiver and antenna. The remote readout requirement will not be addressed. It is expected that the addition of a remote readout will be relatively simple when the system design is complete.

5. Must be capable of automatically tracking and polling at least three aircraft in sequence at selective time intervals from 5-30 minutes, and must be capable of manually polling an aircraft data link.

Comment: These requirements will be met in full.

6. Must be capable of providing an automatic response to an aircraft interrogation. This response would give the cutter's position by the best electronic navigational aids available and would provide for data verification, as in the HH-65A system.

Comment: The acknowledgement of a message receipt and the reply with a position will be met. Provisions for manual input of navigation information for use with a stationary receiving unit (an air station) will be included. This will also mean that manual input will be possible aboard a cutter if the electronic navigational aids become unusable. The data verification will not be included for reasons stated later.

Attempts to acquire the actual protocols for the communications and the technical specifications for the data link equipment installed in the HH-65A helicopters failed. Coast Guard sources could not provide the necessary information. The Collins Government Avionics Division of Rockwell International Corporation, makers of the HH-65A data link, did not respond to requests for the information. The protocols, message formats, and other specifications used in this thesis are estimates of what and how the data

link system should work and not the result of any propproprietary information.

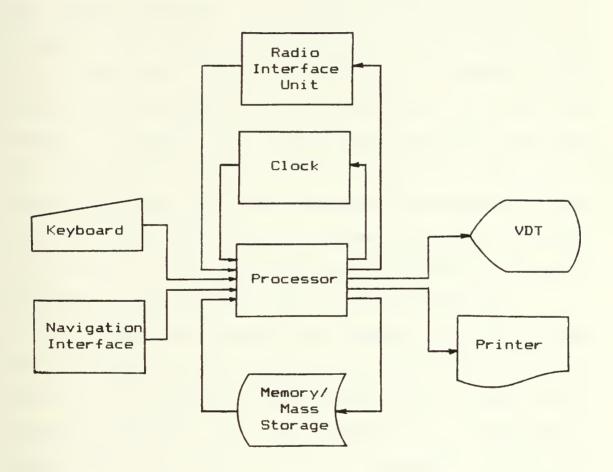

The data link receiver is configured as shown in Figure 1. There are four inputs: from the radio interface unit, the electronic navigation devices interface unit, the clock, and the keyboard. There are four outputs: to the radio interface unit, the video display unit, the printer, and the clock. All inputs to and outputs from the system are digital signals using ASCII code.

There is a pattern of levels of abstraction in this view of the project. At the center is the data link receiver processor designed for this thesis. This processor is responsible for the proper routing of messages to and from memory, calling menus from ROM and sending them to the video display terminal, updating positions, and performing tasks in response to input from the keyboard. It is assumed that there is a radio interface unit that receives and processes all signals. If a message is addressed for this particular Coast Guard unit, then the radio interface unit receives the message, checks the correctness of the message, and sets a flag to tell the data link receiver controller that a message awaits.

The electronic navigation devices are an abstraction for the actual machines that compute the receiver unit's position. These devices may include LORAN-C, OMEGA, navigation satellites, or any other navigation instruments

## DATA LINK RECEIVER

Figure 1

that may be polled by the navigation interface unit. These devices pass their position information to the navigation interface which sets a flag to let the main processor know that a new position has been computed. The system operator may override the automatic polling of the interface unit by the system processor in the event of a malfunction in the navigation instruments. In the case of a shore unit, there is no need for a navigation interface. The operator would manually enter the position of the air station and set the system to prevent the interface being polled in the case where the receiving unit is a shore unit and thus in a constant position. The same method could be used for a ship at anchor when most navigation devices are normally secured. It is essential that the ship's position be sent as often as necessary to keep the helicopter's computer updated.

The third input comes from a clock. The clock is used for time-stamping the positions computed by the navigation devices. This information is passed as part of the acknowledgement messages sent in response to a helicopter's message and also when polling helicopters. The radio interface unit is assumed to have direct access to the clock to obtain the time. The output to the clock from the processor is for setting the date and time and is entered by the operator through the keyboard.

All commands to the system are entered using a keyboard. Menus are provided on the video display unit for

the operator's assistance. Most inputs through the keyboard consist of single keystrokes for the selection of operations as listed in the menu currently displayed. There are several cases where more than one keystroke is required. When an aircraft is logged into or out of the system, the clock is set, or the position of the receiving unit is manually inserted, the operator must enter the appropriate number of characters.

The video display unit may consist of some sort of smart terminal or it may be an interface unit between the main data link processor and the VDT. In either case, the data link receiver's processor need only send certain codes to the video display port. These codes trigger the appropriate actions by which a driver in the video display interface causes the menus to be displayed on the screen. Messages from the helicopters are displayed in a similar manner. This is another advantage of the levels of abstraction. The technology, architecture, and implementation of the device is invisible to the data link receiver processor.

The printer receives its commands and data in a manner similar to that of the video display terminal. It does not receive as much text as the VDT because the menus are not printed. It exists in the system mainly to provide hard copy output of the message traffic during a mission. Should the hard copy not be required or desired, the operator has

only to secure the power switch of the printer. This makes the overall system simpler because there is no need to include an on/off function for the printer in the system.

This approach of levels of abstractions is a reasonable one for several reasons. It would be difficult for CSDE to design a controller that would perform all the requirements of this controller and still be able to meet the required time constraints for each task. The overall system must monitor the airwaves, receive a message, check it for validity, and store it properly not to mention all the other functions required to drive the video display unit, monitor the keyboard for input, and other such tasks.

One criticism of CSDE has been that there is no way to force a design with two CPUs [Ref.17]. CSDE will design a system with two processors when one cannot perform all the functions set forth by the designer within the required time constraints. Nor does CSDE presently allow for more than two CPUs. There are, however, ways around these limitations. The central part of the receiver is designed with the assumption of several "smart" interfaces. These other interface units may also be designed using CSDE as long as the user is careful to specify compatible links between the units. The result is a number of processors integrated into one system much as an operating system or a communications network may be viewed as consisting of layers.

The radio interface will receive messages sent to the particular receiving unit. The message will be tested for completeness and correctness. If the message passes this test, it is held in a buffer and a status flag set. The processor checks the status bit when it polls the radio receiver and if it is set, it reads the message into memory in a serial fashion and passes it to the video display unit and the printer.

The radios, navigation devices, and the keyboard are polled according to the time constraints in the CSDL contingency list. The number of polls of a device per time period vary with the immediacy of the input. For instance, the keyboard will be polled more often than the navigation device. The system must respond to keyboard inputs fast or the operator may become frustrated or think the system is locked up. The position of the unit doesn't change at a fast rate so the position need only be updated every minute or so.

The system will handle at least three helicopters simultaneously. A maximum of ten aircraft may be logged in at any given time. The tail numbers of the helicopters must be logged into the system memory manually by the system operator. The system will receive and process messages from an aircraft not logged in as long as the receiving unit is specifically addressed in the message. It will not,

however, poll any helicopter that is not logged into the system .

The polling of aircraft is done either automatically or manually as selected by the operator. If the polling is on automatic, the operator must select a polling time period from 1 to 30 minutes in duration. The normal reporting period for a Coast Guard helicopter is every 15 minutes. The performance standards and criteria for the system specified periods between five and thiry minutes. A one minute interval was added for closer monitoring of a helicopter during an in-flight emergency or a critical period during a search and rescue case or law enforcement action.

Messages from the helicopters are fixed in format. The messages are received and held in a buffer by the radio interface. While the message is read into memory, it is printed on the video display terminal and on the printer. Messages are acknowledged by the radio interface by sending the position of the receiving unit and the time the position was calculated back to the helicopter. The position is read from the navigation interface by the processor and stored in memory. It is called from memory when needed and passed serially to the radio interface.

A garbled message from an aircraft is not acknowledged. When a message is not acknowledged, the helicopter's data link processor will resend the message

after waiting a random period of time. The message will be sent again and again with random wait times between transmissions until acknowledged. After being sent a certain number of times without acknowledgement, the pilots are notified by a message printed on their VDTs.

If two or more helicopters send messages simultaneously, none will be acknowledged. This contention is not serious since the helicopters will resend their messages after waiting a random period. The messages are short (less than 64 bytes sent at 300 baud) and most cutters operate with only one helicopter at a time. An exception are the five polar icebreakers that normally carry two helicopters. Operations from air stations present the highest probability of contention since they might have two or more helicopters airborne on missions at the same time. The short duration of the messages coupled with the few aircraft generally under the control of one unit plus the random timing for resending a message creates a situation where the contention is self-correcting.

The messages are stored in the same packed form as they are received. When the messages are processed for display, they are filled out with the necessary descriptive enhancements. The overlays or templates for this purpose reside in ROM and are inserted by the video display unit as the messages are displayed on the VDT. The system has the ability to store the last ten messages received in memory.

The protocol of the data link transmissions include the preamble, control data, and information. The preamble and control data sections are used by the radio interface. The information section alone is passed to the processor by the radio interface. The information section of the message follows the format below. The number of characters in each field are shown in parentheses.

- Helicopter number. (From)

4 digits (1409)

- 2. Ship/ground station identifier. (To)

4 digits (7184)

- 3. Date and time. (DTG for message numbering)

12 characters (311545ZMAY84)

- 4. Position time. (This is the time the position was calculated. The time may be local or Zulu, depending on local doctrine).

4 digits (1543)

5. Message type. (Message types include normal position reports, poll response, etc., or mission type such as fisheries patrol, drug interdiction,

search and rescue, etc., and can declare an aircraft

emergency)

1 character (3)

6. Position. (Latitude/Longitude. Format is degrees, minutes, and tenths of minutes followed by N or S for latitude, E or W for longitude; i.e., Lat = ddmmtN, Long = dddmmtW)

13 characters (36429N088321W)

7. Ground speed (in knots).

3 digits (105)

8. Track (in degrees true).

3 digits (220)

9. Fuel (in pounds, less reserve).

4 digits (1200)

10. Wind direction (in degrees true).

3 digits (345)

11. Wind velocity (in knots).

3 digits (022)

- 12. Altitude (in hundreds of feet).

2 digits (12)

- 13. CRC (cyclic redundancy check. This is used in the radio interface unit but is not read into the processor's memory).

Each field of the message will be complete, that is, each field will use its full number of characters. If the information for a particular field is unavailable for some reason (the failure of an instrument such as the omnidirectional airspeed indicator or lack of an updated position because of loss of LORAN lock on) the field will be filled with blanks (20H). Fields that are short will use blanks (20H) or zeroes (00H) as appropriate to pad the data field.

The format for the examples given above looks like this:

- 31 34 30 39 37 31 38 34 33 31 31 35 34 35 **5**A 4D 41 **5**9 38

- 34 31 35 34 33 33 33 36 34 32 39 4E 30 38 38 33 32 31 57

- 31 30 35 32 32 30 31 32 30 30 33 34 35 30 32 32 31 32

These numbers are hexidecimal representations of the ASCII characters for the numbers and letters used in the examples.

Keyboard inputs provide the operator's control over the system. The input system is simplified to the point where single keystrokes are all that are necessary to invoke different functions. When a keyboard input is detected, the appropriate menu is placed on the video display unit. The operator uses single keystrokes to select and invoke the different system functions. The menus are contained in ROM and are written to the VDT by the video display unit interface. The data link receiver processor sends the appropriate code to the video display unit interface to call the menus to the screen.

## III. CSDL DESIGN

The Control System Design Environment was first proposed by Matelan [Ref. 18] as a method of simplifying the design of process controllers. Ross implemented the Control System Design Language (CSDL) as part of this environment [Ref. 19]. The designer of a controller system describes the inputs and outputs needed and the required response times for different functions. Using this high-level language makes the design of the controller much simpler than it would be without the use of computer-aided design tools.

Some of the syntax rules of CSDL should be mentioned. CSDL programs must be in upper case characters only. Most statements end in a semicolon. The names of functions end with a colon while task names end with a semicolon. The final end statement has no punctuation. Variable names cannot exceed ten characters. Because they are later truncated to six characters, the user should insure that the first six characters in a name are unique. A complete listing of the formal syntax of CSDL is available in Carson's thesis [Ref. 20].

There are five sections to CSDL programs. The sections are Identification, Environment, Contingency List,

and Procedures. The Identification section is simply the name of the designer, the date, and the project name. It is intended to identify the program and does not have any effect when the program is run. It appears in this format:

## IDENTIFICATION

DESIGNER: "SUTTER FOX"

DATE: "05-31-84"

PROJECT: "COAST GUARD DATA LINK RECEIVER"

The second section is the design criteria. This is the portion of the program where the designer can choose the primitive list and processor family for CSDL to use. At present there are three realization libraries. They are based on the 8080, Z80, and 8086 microprocessor families. The format for the design criteria section is:

DESIGN CRITERIA

METRIC FIRST;

VOLUMES 1;

MONITORS 1;

METRIC FIRST refers to the first realization that meets the the timing requirements of the system. Alternatively, the designer may prescribe cost or power as the minimum requirements for the system. VOLUMES refers to the realization libraries in the order they are numbered. Since only one volume was resident when this project was translated, the first (and only) volume was designated. As with the realization volume, there is only one monitor volume for the realization volume, and thus the first (and only) monitor is selected.

design variables are declared in the environment section. The system for the data link receiver produced under CSDL requires a greater number of variables than any earlier attempt at a CSDE controller generation . This will be discussed in more detail later in this chapter. There are three types of variables in a CSDL program. variables are values that are sensed by the controller from outside of the controller processor. The output variables send values outside the controller. The declaration of these variables includes the number of lines necessary between the controller and the outside world the type of technology desired for their design. The third type of variable is the arithmetic variable. Arithmetic variables used in computations within the controller itself. The declarations made in the environment section are analogous to declarations made in a block structured language such as Pascal, Ada, or PL/I. The format of environment section is:

## ENVIRONMENT

INPUT : KEYFLG,1,TTL; KEYCHAR,8,TTL;

MANPOS,8,TTL; END INPUT;

OUTPUT: MENU, 8, TTL; POLL, 8, TTL; MSGVDT, 8, TTL; MSGRCVD, 1, TTL; END OUTPUT;

ARITHMETIC: KEYINMAIN,8; MINTAC,8; NEXTMSG,8; NEXTAC,8; COUNT,8; END ARITHMETIC;

The procedures section is much the same as found in block structured languages. This section contains the high-level descriptions of the arithmetic and data manipulations required to make the system work. There are two types of blocks within the procedures section: functions and tasks. The functions and tasks are always coupled in what are referred to as contingency/task pairs. Each function is evaluated in its turn as set forth in the contingency list. If it is true, its associated task is performed. The requirement that each function have one and only one task creates some problems with programming with CSDL that will be discussed later. An example of a function and a task follows.

```

BINARY, 1;

SENSE (KEYFLAG);

IF KEYFLAG = 1 THEN KEYINMAIN := 1; END IF;

END KEYINMAIN;

TASK KBINPMAIN;

MENU:=0; ISSUE (MENU);

SENSE (KEYCHAR);

IF KEYCHAR = 1 THEN MINTAC := 1; END IF;

IF KEYCHAR = 2 THEN MMSGDSPLY := 1; END IF;

IF KEYCHAR = 3 THEN MLOCATION := 1; END IF;

IF KEYCHAR = 4 THEN MCLOCKSET := 1; END IF;

IF KEYCHAR = 5 THEN MLOGINOUT := 1; END IF;

KEYINMAIN := 0;

```

FUNCTION KEYINMAIN:

FUNCTION KEYINMAIN is called according to the time constraints set forth in the contingency list as described in the next paragraph. The keyboard active status flag is checked by SENSE (KEYFLG). If the flag is set, then the

variable KEYINMAIN is set. Thus, the function is true the associated task KBINPMAIN is performed. This task calls for the video display interface to put the appropriate menu VDT with the statements MENU:=0 and ISSUE (MENU). The menu presents the five selections available to waits for input. Upon pressing a number key and five, the appropriate variable is set to one. from one to Note that the variable is the same name as a function in the CSDL program. When that particular function is tested found to be true, its associated task will be performed. The final line sets the function associated with the task to zero so that it will not be performed again until set. Ιt important in this data link receiver project to insure that no more than one function be set at any given time order to preserve the flow of program control.

The fifth section is the contingency list. In this section the designer lists the contingencies (functions) that occur and the time constraints for performing the associated tasks. This is where CSDL differs greatly from languages that execute in a linear manner such as FORTRAN, BASIC, or Pascal. The timing requirements may be such that some functions are tested several times before another certain function is tested at all. Some procedures (tasks) may be performed every designated time period. The execution of functions and procedures are dependent upon the timing requirements the designer delineates in this section

of a CSDL program. An example for the contigency section is:

## CONTINGENCY LIST

WHEN KEYINMAIN : 100 MS DO KBINPMAIN; WHEN MINTAC : 100 MS DO INTAC; WHEN SMMANUAL : 100 MS DO MANUAL; WHEN SMAUTO :100 MS DO AUTO; WHEN TPOLL :100 MS DO POLLAUTO; WHEN MLOCATION : 100 MS DO LOCATION; WHEN TMLOCATION: 100 MS DO MANLOC; WHEN POSCH :100 MS DO POSUPDATE; WHEN MMSGDSPLY : 100 MS DO MSGDSPLY: WHEN MCLOCKSET: 100 MS DO CLOCKSET: WHEN MLOGINOUT : 100 MS DO LOGINOUT; WHEN TLOGIN : 100 MS DO LOGIN; WHEN TLOGOUT : 100 MS DO LOGOUT; WHEN MSGIN : 100 MS DO MSGSTORE;

Writing code in CSDL is not as easy or convenient as in many high-level languages. There are several factors that can make it a frustrating experience for those who are used to the constructs available in languages such as Pascal, PL/I, and even BASIC. The reader should not judge CSDL too harshly. It should be remembered that the CSDL language was designed for simpler controllers than the one attempted in this thesis.

There are no comments in CSDL other than those enclosed in quotes in the Identification Section. It is widely accepted that commenting within programs makes it easier to maintain those programs. Since most candidates for a CSDE implementation are relatively simple, and since most CSDL programs will be written and implemented in a fairly short time, this may not be a very big problem.

The data link receiver project would normally be a candidate for an interrupt-driven system. As it is presently implemented, CSDL has no ability to design systems that use interrupts.

Since all contingencies and tasks in CSDL must be in a one to one ratio, all the functions and tasks have been placed together in the listing for this data link receiver CSDL program. This makes it clearer for the reader (not to mention the programmer) when perusing the code. There are many menus in this system and the functions and tasks have been named to reflect the fact that some menus are called from other menus. The main menu presents five choices. If, for instance, the operator selects "Interrogate Aircraft", FUNCTION MINTAC is set to 1 (true). FUNCTION MINTAC is paired with TASK INTAC. Functions generally have more letters in their names than their tasks since functions generally have a prefix added to the name of the associated task. TASK INTAC calls up a menu wherein the operator may select a return to the main menu without any function being carried out, or the operator may elect to interrogate the aircraft manually or automatically. If the selection is to interrogate automatically, FUNCTION SMAUTO is set true. TASK AUTO is paired with FUNCTION SMAUTO, and by now the pattern may be clear to the reader. The name of function that is set to true by a selection made under the main menu is prefixed with an M. A menu called from a task that is

associated with "M" function has a function prefixed with "SM" for secondary menu. When there is another submenu, the function name will be prefixed with "TM" for tertiary menu. Tasks have names similar to their associated functions but without the prefixs.

One construct that would be most welcome in CSDL the CASE statement. This would allow ease of programming when one out of several possible paths would be chosen. lack of a CASE construct requires one to write multiple IF statements which does not make for the most elegant programming. Several of the procedures in this data receiver project have ten IF statements where some other languages would be able to express the same function in one two lines. This does take up some space in memory but when compiled it requires less space and may be insignificant in terms of overhead. The real problem that is evident is that there are many more variables necessary in most other high-level languages. CSDL does not allow for subscripting variables which leads the designer of system to writing many more lines of code and having to name each variable instead of using subscripts. example, ten messages are required to be in memory at any given time. This requires ten different variable names for these ten messages. A pointer must keep track of the next message block available for use and it would be quite simple to use subscripted variables for this purpose. Since this

is not possible, a series of nearly identical IF statements must be traversed when locating the next block. The same problem occurs when printing the messages. The code must explicitly name each of the ten variables. It would require less memory for the program to be able to refer to these variables with subscripts and would also make for clearer code. The complexity could be simplified by adding new primitives that would allow for the constructs using subscripted variables. Examples of tasks with multiple statements that could be handled with a CASE statement include KBINPMAIN, INTAC, and AUTO. Nearly every task in this program could benefit from the use of subscripted variables.

The original design approach was to divide the memory for the ten messages according to the number of aircraft logged into the system. Two message memories were to be reserved for messages from helicopters not logged in. Thus, there would have been a maximum of eight aircraft tracked where each would have one message available for immediate recall. This would be the worst case scenario and also highly unlikely. If only one helicopter was logged in, the system could maintain the last eight messages for that one helicopter. Since CSDL does not provide a capablity for indexing variables, it would be difficult to provide such dynamic allocation of the ten message memory areas.

It is highly likely that there will be three or less helicopters logged into one system at any given time. It is less likely that there would be four or more aircraft logged in simultaneously. Standard safety procedures call for a helicopter to maintain a radio quard at all times and send "operations normal" and position report every fifteen minutes. If there were three helicopters logged into one system that would mean 12 reports in an hour. This means that the two earliest reports would be overwritten by newer messages at the end of an hour but there would be at least three messages remaining for each aircraft. Even if there were ten aircraft using the system, there would be at least one message in memory for each aircraft. This would be the last position sent and would be used as a datum for search and rescue procedures should communications be lost with the aircraft. Position reports include heading, track, ground speed, and other environmental data that would provide excellent search planning information. Since manual polling of the helicopters is provided, it would be possible to manually poll one or more helicopters enough times so that there would not be any messages in the memory from a particular helicopter. There are two backups in this case. First, the printer should be enabled so that there would hard copy of all the messages. The second is the multi-track audio tapes that monitor telephone and radio traffic at air stations and aboard the flight-deck equipped

cutters. Should it be required in an emergency, the tapes could be run back as far as necessary and then replayed to feed the raw radio signals to the radio interface device.

Reading messages in from the electronic navigation device interface created a problem when coding the program. Each message is 56 bytes long and the input to the processor is 8 bits wide. In order to read in the message, the bytes must be read into the processor and sent to memory, the video display unit, and the printer in a serial fashion. There was no construct in CSDL that would read in a string of characters of this length. This function is one that is basic to the operation of this system. String handling can be added by writing a new primitive that would read in the 56 bytes or any other number by overloading the SENSE (input) statement in CSDL. Without this addition to the language, there could be no CSDL implementation that would satisfy the requirements of the data link receiver project. A similar primitive can be specified to write a message out to the VDT and printer when the operator selects that function. These primitives can be general enough that they may be used for different sizes of strings.

When the CSDL program is completed, it is translated by Carson's CSDL.PAS program. This program, written in Pascal, takes the high-level CSDL program and translates it into a primitive list for the controller. The primitive

list is used in the next step in the control system design environment process.

list is used in the next step in the control system design

ANALOGO POSTORIONIA

## IV. IMPLEMENTATION

The next step in the process from the high-level description to the hardware and software listings is to take the output of the CSDL translator and feed it through Ross' FORTRAN program, NEWCSDL.FOR.

main task performed by NEWCSDL.FOR is to map the primitive list compiled by CSDL.PAS to the selected realization library. The output includes a listing of the hardware to implement the controller and the assembly language software to run it. Two files, the primitive list and another containing information about the contingency list, are used by the Optimizer Module in NEWCSDL.FOR to set up a formatted application table and an index to the selected realization volume. The Functional constructs the Realization Timing Table and determines if the realization is feasible. A monitor sequence is added and actual values are substituted for dummy parameters and an output listing is generated. If the Timing Analyzer fails to find a feasible single processor realization, the contingency/task list is partitioned and a dual processor generated under realization i 5 the control of the Optimizer. For greater detail, see doctoral Ross' dissertation [Ref. 21].

The project at this point had progressed from the CSDL description through translation by Carson's CSDL.PAS program. This was the second attempt to use CSDL.PAS on a project. The first use was for a test of CSDL.PAS conducted by Carson by running Riley's jet engine start sequencer controller through the translator.

There were some problems getting the CSDL description for the data link receiver project through the translator. The data link receiver required so many variable names that it exceeded the size limits set in CSDL.PAS. One problem concerned a CASE statement in the CSDL.PAS program where 20 possible cases existed. This problem was resolved by increasing the allowed number of cases to 95. There were other errors generated in translation that were quite frustrating. One problem was overcome when it was discovered that CSDL.PAS would generate errors whenever a tabkey had been used to produce spacing within the CSDL description. All tabkey spacing was removed and replaced with spaces generated using the spacebar. CSDL.PAS should be modified to allow for spaces generated by either the space bar or the tabkey.

More problems were discovered when trying to run the primitive list generated by CSDL.PAS through NEWCSDL.FOR. FORTRAN is notorious for the inflexibility of program inputs, which is a carryover from the days of card input.

NEWCSDL.FOR is no exception. Title lines for functions and procedures in the primitive files have the format:

1 6 23 p xxx t.generated for: procedure name

where xxx represents the line number of the primitive and t stands for title line. The t.generated for primitive marks the beginning of a new procedure. The procedure names in the title lines of the primitive list as generated by CSDL.PAS were in column 22. When NEWCSDL.FOR is run with the procedure name in the wrong column, everything between the title lines is ignored and error messages are generated for each title line in the file. Each title line in the primitive list had to be reformatted to meet the requirements of NEWCSDL.FOR.

Another problem encountered in the translation was that the s.ni primitive should have appeared as:

p xxx g.ni (::)

The s stands for a software primitive. An h stands for a hardware primitive. The colons inside the parentheses are required because they are used to separate variables, parameters, and attributes. They were not in the primitive list generated by CSDL.PAS. The colons were added using the text editor. A similar error was discovered in the s.main primitive.

The entire primitive list must be in lower case letters except for the function and task names. They may be

in upper or lower case as long as they are consistent with the case used in the contingency list file. Although CSDL.PAS allows variable names of up to ten characters in length, NEWCSDL.FOR has a maximum of six characters. The designer must insure that no two variables have the same six first characters.

While the formatting errors and the lack of colons in the proper places created some unnecessary work, the biggest problem at this point was the incompatibility of the primitive list and the Z80 realization library. For instance, the function of one basic primitive is to sense a value on a particular input line to the processor. This primitive has the form:

p xxx s.sensecond (keychar:8)

where sensecond stands for sense condition, keychar is the name of some variable, and eight refers to the arithmetic precision of the variable. It was discovered that the Z80 realization library did not contain any realization of this primitive.

The Z80 library was designed by Smith at the same time Riley was working on the jet engine start controller. This was before Carson's CSDL.PAS program was available. Riley had to translate the CSDL listing into a primitive list by hand. Since he chose to implement his project using the Z80 library, he and Smith worked closely together. Prolog equipment was used for the project implementation and so

Smith geared the Z80 library toward that end. Thus, the Z80 library was not as general as needed to produce contollers using other hardware. In particular, the I/O primitives were designed specifically to match the Prolog hardware. The s.sense and s.issue primitives were not needed for the Prolog implementation and thus were not included in the Z80 realization library.

At this point it was decided to shift the emphasis from using the Z80 realization library to the 8080 and 8086 realization libraries. There were two reasons for this. First, the designer of the 8086 library, Cetel, was still available to make adjustments to the library. Second, the 8086 library closely followed the example of the original 8080 library built by Ross. If the primitive list could be adjusted to run under NEWCSDL.FOR, then two realizations of the data link receiver could be produced. This would help standardize the realization libraries to where any library could be used with the primitive list output by CSDL.PAS and further processed by NEWCSDL.FOR.

Other problems remained stemming from the incompatibility of the primitive list produced by CSDL.PAS and the realization libraries. CSDL.PAS produced other primitives that did not exist in the realization libraries. These primitives included s.inputport and s.outputport. Inputport and outputport are both primitives that remain to be added to the realization libraries.

The s.forcons and s.forend primitives in the 8080 and 8086 libraries are not in the same format. These primitives mark the beginning and end of for-next loops. There are two variables for the upper and lower values of the loop.

NEWCSDL.FOR expects actual numbers but CSDL.PAS produces variable names instead.

The s.exitproc primitive marks the end of a procedure in the primitive list. NEWCSDL.FOR was designed to use the contingency name in the parameter list to reset the value of the contingency to zero after the task was executed. The CSDL program written for this project included a statement at the end of each task explicitly resetting the contigency. Ross decided that the realization libraries and NEWCSDL.FOR would be changed to adopt this latter method of resetting the contingency.

There are several different primitives with the same names in a realization library. This is to allow for different precisions of arithmetic manipulations. NEWCSDL.FOR performs a binary search to find a primitive name. When it finds the primitive, it searches up the realization library index to find the first instance of the primitive name. NEWCSDL.FOR then works down through the index to find the first instance of the primitive that will satisfy the precision required. For instance, s.var and

s.cons primitives in the 8086 realization library had the format:

```

s.var (nam, val: 0,8 :...etc)

s.var (nam, val: 0,16 :...etc)

s.var (nam, val: 0,24 :...etc)

```

where the O,n referred to variables with zero to n bits of precision. It was discovered that NEWCSDL.FOR was choosing the greatest precision available every time. This was corrected by changing 8086 realization library to the format:

```

s.var (nam, val: 0,8 :...etc)

s.var (nam, val: 9,16 :...etc)

s.var (nam, val: 17,24 :...etc)

```

The correct precision is now selected for these particular primitives but the entire 8086 library must be examined for other instances of this precision error.

NEWCSDL.FOR requires a listing of the contingency/task pairs in a file named IADEFL.DAT as one of its inputs. CSDL.PAS creates such a file but it is not in the required format. A new line for the system must be added as the first line in the file. The other columns must be corrected to the format as set forth in Ross' doctoral dissertation.

The multiplication primitive, s.mult, was present in the 8086 library as s.mul. The two precisions of multiply were renamed s.mult to conform with the standard. The s.mult primitive in the 8080 library had been changed by Polluck from a strictly software implementation to one that called an arithmetic chip to do a hardware multiply. The

chip had been removed from the library at some point before this project was started. Either the chip or the software multiplication routine must be restored for the 8080 library to correctly handle multiplication.

The size of the program also created problems in NEWCSDL.FOR. One of the stacks in the Formatter Module proved to be too small for the data link receiver project. The stack overflowed before the completion of the realization. The program was adjusted by Ross to allow for a greater stack size. The output of NEWCSDL.FOR for the 8086 library is in Appendices D and E.

At the time of writing this thesis, the following corrections and alterations to the primitive file must be made for NEWCSDL.FOR to properly process it. The two lines with

t.generated for: SYSTEM \*\*\*\*\*\*\*\*\*

must be corrected to start the word system in column 23.

The second line,

s.MAIN (::)

must be changed so that the word main is in lower case letters. All lines with s.inputport or s.outputport must be removed from the program altogether until those primitives are added to the realization libraries.

Even with these changes, some errors were still produced. To avoid problems with the s.in, s.ni, s.forcons, s.forend, and s.exitproc primitives, the original CSDL

program was rewritten to remove for-next loops and timed blocks. These primitives must be standardized before they may be used without concern for any errors they may produce. The revised CSDL program is in Appendix B.

The two realization libraries now produce the software and hardware listings to implement the data link receiver project but not without errors. One prominent mistake is that each time an input is sensed, another chip is added to the hardware listing. There should only be one I/O chip produced for a particular input or output. At the time of this writing, CSDL.PAS and NEWCSDL.FOR are being patched to correct some of the problems discovered while designing the data link receiver.

## V. CONCLUSIONS AND RECOMMENDATIONS

The Control System Design Environment holds great promise as a tool for simplifying the work of designers and reducing the expense of producing controllers. This ambitious data link receiver project has shown that the CSDE has greater application than may have been realized by those who did the early work on it. This project has shown that it may be possible to design a system in modules and use CSDE to design each each of the modules independently of the others as long as the interfaces are compatible.

This project has also demonstrated the necessity for compatibility among the different programs within the Control System Design Environment. Since the output of one program is the input of another, there must be a conscious effort to standardize the interfaces.

Heilstedt has recommended that NEWCSDL.FOR be rewritten in a newer language than FORTRAN [Ref. 22]. While it is true that other languages may be easier to maintain than FORTRAN, there are other items in the Control System Design Environment that should be addressed first for a better return on the investment of the time and effort that would be required. Since VMS on the VAX computer allows a file produced under one language to be used as input to

another language, there is no need to rush a reprogramming of NEWCSDL.FOR. A rewrite of NEWCSDL.FOR would make input less column-dependent. A more critical problem is the incompatibilty among the different realization libraries. There should be a standardization of primitive names and their associated functions. Without this standardization. mapping from primitive lists to the realization libraries will continue to be a hit or miss proposition. One of the major objectives of the Control System Design Environment is that much of the work can be automated to make designing, prototyping, testing, and implementation controllers faster and less expensive. The lack standardization requires the intervention of the designer to make the transitions between the various elements of the system.

Along with the standardization of the realization libraries, CSDL.PAS should be updated to incorporate the standards. This program is a real boon to the designer since it removes the tedious work of translating the CSDL program into the primitive list. As previously discussed, implementing some other high level constructs in CSDL.PAS would be an enhancement of the value of the program for the system user. These constructs should include CASE statements and the use of subscripted variables.

The Control System Design Environment has great promise and could be a lucrative product when it is improved

to provide an automatic transition from CSDL description to the hardware and software listings. As presently implemented, it requires too much effort while moving through the different segments of the system. A great deal of work remains to be done, especially the testing of the interfaces between the different sections and of the realization libraries. It seems that the work will be well worth it.

## LIST OF REFERENCES

- 1. Matelan, M.N., <u>The Automated Design of Real Time</u>

<u>Control Systems</u>, Lawrence Livermore Laboratory, 10

December 1976.

- 2. Ross, A.A., <u>Computer Aided Design of Microprocessor</u>

<u>Based Controllers</u>, Ph.D. Thesis, University of California, Davis, June 1978.

- Smith, T.J., <u>Implementation of a Zilog Z-80 Based</u>

Realization <u>Library for the Control System Design</u>

Environment, M.S. Thesis, Naval Postgraduate School,

March 1984.

- 4. Cetel, A.J., Implementation of an Intel 8086-Based Realization Library for the Control System Design Environment, M.S. Thesis, Naval Postgraduate School, June 1984.

- Carson, T.H., <u>A Translator for a Computer-Aided Design</u>

<u>System</u>, M.S. Thesis, Naval Postgraduate School,

June 1984.

- 6. Cetel, A.J., Implementation of an Intel 8086-Based Realization Library for the Control System Design Environment, M.S. Thesis, Naval Postgraduate School, June 1984.

- 7. Heilstedt, M.R., <u>Automated Design of Microprocessor</u>

<u>Based Digital Filters</u>, M.S. Thesis, Naval Postgraduate School, June 1983.

- 8. Polluck, G.G., <u>Further Development and Investigation of Computer-Aided Design of Microprocessor Systems</u>, M.S. Thesis, University of California, Davis, December 1981.

- 7. Riley, R.P., <u>Control System Design Language</u>

<u>Implementation of a Gas Turbine Starting Controller</u>,

M.S. Thesis, Naval Postgraduate School, March 1984.

- 10. Sherlock, B.J., <u>User-Friendly, Syntax Directed Input</u>

to a <u>Computer-Aided Design System</u>, M.S. Thesis, Naval

Postgraduate School, June 1983.

- 11. Smith, T.J., Implementation of a Ziloq Z-80 Based Realization Library for the Control System Design Environment, M.S. Thesis, Naval Postgraduate School, March 1984.

- 12. Walden, H.J., <u>Application of a General Purose DBMS to Design Automation</u>, M.S. Thesis, Naval Postgraduate School, December 1983.

- Woffinden, D.S., <u>Interactive Design Environment for a Computer-Aided Design Environment</u>, M.S. Thesis, Naval Postgraduate School, June 1984.

- Polluck, G.G., <u>Further Development and Investigation of Computer-Aided Design of Microprocessor Systems</u>, M.S. Thesis, University of California, Davis, December 1981.

- 15. Heilstedt, M.R., <u>Automated Design of Microprocessor</u>

<u>Based Digital Filters</u>, M.S. Thesis, Naval Postgraduate School, June 1983.

- 16. Riley, R.P., <u>Control System Design Language</u>

<u>Implementation of a Gas Turbine Starting Controller</u>,

M.S. Thesis, Naval Postgraduate School, March 1984.

- 17. Heilstedt, M.R., <u>Automated Design of Microprocessor</u>

<u>Based Digital Filters</u>, M.S. Thesis, Naval Postgraduate School, June 1983.

- 18. Matelan, M.N., <u>The Automated Design of Real Time</u>

<u>Control Systems</u>, Lawrence Livermore Laboratory, 10

December 1976.

- 19. Ross, A.A., <u>Computer Aided Design of Microprocessor-Based Controllers</u>, Ph.D. Thesis, University of California, Davis, June 1978.

- 20. Carson, T.H., <u>A Translator for a Computer-Aided Design System</u>, M.S. Thesis, Naval Postgraduate School, June 1984.

- 21. Ross, A.A., <u>Computer Aided Design of Microprocessor-Based Controllers</u>, Ph.D. Thesis, University of California, Davis, June 1978.

- 22. Heilstedt, M.R., <u>Automated Design of Microprocessor</u>

<u>Based Digital Filters</u>, M.S. Thesis, Naval Postgraduate School, June 1983.

#### APPENDIX A

# CSDL PROGRAM

IDENTIFICATION DESIGNER: "SUTTER FOX" DATE : "05-31-84" PROJECT : "COAST GUARD DATA LINK RECEIVER" DESIGN CRITERIA METRIC FIRST; VOLUMES 1: MONITORS 1; ENVIRONMENT INPUT: KEYFLG, 1, TTL; KEYCHAR, 8, TTL; MANPOS, 8, TTL; NEWPOS, 1, TTL; POSITION, 8, TTL; MSGREADY, 1, TTL; MESSAGE, 8, TTL; ACNUM, 8, TTL; END INPUT; OJIPUT: MENU, 8, TTL; POLL, 8, TTL; MSGVDT, 8, TTL; MSGRCVD, 1, TTL; END OUTPUT; ARITHMETIC: KEYINMAIN.8; MINTAC.8; MMSGDSPLY.8; MLOCATION, 8; MCLOCKSET, 8; MLOGINOUT, 8; SMMANUAL, 8; SMAUTO,8; ACO,8; AC1,8; AC2,8; AC3,8; AC4,8; AC5,8; AC6,8; AC7,8; AC8,8; AC9,8; INTPERIOD,8; MSG0,8; MSG1,8; MSG2,8; MSG3,8; MSG4,8; MSG5,8; MSG6,8; MSG7,8; MSG8,8; MSG9,8; TMLOCATION,8; TLOGIN,1; TLOGOUT, 1; NEXTMSG, 8; NEXTAC, 8; TPOLL, 1; COUNT, 8; END ARITHMETIC: PROCEDURES FUNCTION KEYINMAIN: BINARY, 1; SENSE (KEYFLG); IF KEYFLG=1 THEN KEYINMAIN:=1; END IF; END KEYINMAIN;

TASK KBINPMAIN;

```

MENU:=0: ISSUE (MENU);

SENSE (KEYCHAR);

IF KEYCHAR=1 THEN MINTAC :=1; END IF;

IF KEYCHAR=2 THEN MMSGDSPLY:=1; END IF;

IF KEYCHAR=3 THEN MLOCATION:=1; END IF;

IF KEYCHAR=4 THEN MCLOCKSET:=1; END IF;

IF KEYCHAR=5 THEN MLOGINOUT:=1; END IF;

KEYINMAIN:=0;

FVD KBINPMAIN;

FINCTION MINTAC:

BINARY, 1;

SENSE (KEYCHAR);

END MINTAC;

TASK INTAC:

MENU:=1; ISSUE (MENU);

SENSE (KEYCHAR);

IF KEYCHAR=0 THEN KEYINMAIN:=1; END IF;

IF KEYCHAR=1 THEN SYMANUAL :=1; END IF;

IF KEYCHAR=2 THEN SMAUTO :=1; END IF;

MINTAC: = 0;

END INTAC:

FUNCTION SMMANUAL:

BINARY, 1;

SENSE (KEYCHAR);

END SMMANUAL;

TASK MANUAL;

IF ACO/=0 THEN POLL:=0; ISSJE (POLL); END IF;

IF AC1/=0 THEN POLL:=1; ISSJE (POLL); END IF;

IF AC2/=0 THEN POLL:=2; ISSUE (POLL); END IF;

IF AC3/=0 THEN POLL:=3; ISSUE (POLL); END IF;

IF AC4/=0 THEN POLL:=4: ISSUE (POLL); END IF;

IF AC5/=0 THEN POLL:=5; ISSJE (POLL); END IF;

IF AC6/=0 THEN POLL:=6; ISSUE (POLL); END IF;

IF AC7/=0 THEN POLL:=7; ISSJE (POLL); END IF;

IF AC8/=0 THEN POLL:=8; ISSUE (POLL); END IF;

IF AC9/=0 THEN POLL:=9; ISSUE (POLL); END IF;

SMMANUAL:=0;

END MANUAL;

FUNCTION SMAUTO:

BINARY, 1;

SENSE (KEYCHAR);

END SMAUTO;

```

```

TASK AUTO;

MENU:=2; ISSUE(MENU);

SENSE (KEYCHAR);

IF KEYCHAR=0 THEN KEYINMAIN := 1; END IF;

IF KEYCHAR=1 THEN INTPERIOD := 30; END IF;

IF KEYCHAR=2 THEN INTPERIOD := 20; END IF;

TE KEYCHAR=3 THEN INTPERIOD := 15 : END TE:

IF KEYCHAR=4 THEN INTPERIOD := 10 ; END IF;

IF KEYCHAR=5 THEN INTPERIOD := 5; END IF;

IF KEYCHAR=5 THEN INTPERIOD := 1; END IF;

SMAUTO:=0;

TPOLL:=1;

END AUTO;

FUNCTION TPOLL:

BINARY, 1;

IF INTPERIOD=30 THEN IN 30 M DO TPOLL:=1;

END IN; END IF;

IF INTPERIOD=20 THEN IN 20 M DO TPOLL:=1;

END IN; END IF;

IF INTPERIOD=15 THEN IN 15 M DO TPOLL:=1;

END IN; END IF;

IF INTPERIOD=10 THEN IN 10 M DO TPOLL:=1;

END IN; END IF;

IF INTPERIOD = 5 THEN IN 5 M DO TPOLL:=1;

END IN; END IF;

IF INTPERIOD= 1 THEN IN 1 M DO TPOLL:=1;

END IN; END IF;

END TPOLL;

TASK POLLAUTO:

IF ACO/=0 THEN POLL:=0; ISSUE (POLL); END IF;

IF AC1/=0 THEN POLL:=1; ISSUE (POLL); END IF;

IF AC2/=0 THEN POLL:=2; ISSUE (POLL); END IF;

IF AC3/=0 THEN POLL:=3; ISSUE (POLL); END IF;

IF AC4/=0 THEN POLL:=4; ISSUE (POLL); END IF;

IF AC5/=0 THEN POLL:=5; ISSUE (POLL); END IF;

IF AC6/=0 THEN POLL:=6; ISSUE (POLL); END IF;

IF AC7/=0 THEN POLL:=7; ISSUE (POLL); END IF;

IF AC8/=0 THEN POLL:=8; ISSUE (POLL); END IF;

IF AC9/=0 THEN POLL:=9; ISSUE (POLL); END IF;

TPOLL:=0;

END POLLAUTO;

FUNCTION MMSGDSPLY:

BINARY, 1;

SENSE (KEYCHAR);

```

```

END MMSGDSPLY;

TASK MSGDSPLY;

MSGVDT:=MSGO; ISSUE(MSGVDT);

MSGVDT:=MSG1; ISSUE(MSGVDT);

MSGVDT:=MSG2; ISSUE(MSGVDI);

MSGVDT:=MSG3; ISSUE(MSGVDT);

MSGVDT:=MSG4; ISSUE(MSGVDT);

MSGVDT:=MSG5; ISSUE(MSGVDT);

MSGVDT:=MSG5; ISSUE(MSGVDT);

MSGVDT:=MSG7; ISSUE(MSGVDT);

MSGVDT:=MSG8; ISSUE(MSGVDT);

MSGVDT:=MSG9; ISSUE(MSGVDT);

MMSGDSPLY:=0;

END MSGDSPLY;

FUNCTION MLOCATION:

BINARY, 1;

SENSE (KEYCHAR);

END MLOCATION;

TASK LOCATION;

MENU:=3; ISSUE (MENU);

SENSE (KEYCHAR);

IF KEYCHAR=0 THEN KEYINMAIN:=1; END IF;

IF KEYCHAR=1 THEN NEWPOS:=1; END IF;

IF KEYCHAR=2 THEN NEWPOS:=0; TMLOCATION:=1; END IF;

MLOCATION: = 0;

END LOCATION;

FUNCTION IMLOCATION:

BINARY, 1;

SENSE (KEYCHAR);

END IMLOCATION;

TASK MANLOC;

SENSE (MANPOS);

POSITION: = MANPOS;

TMLOCATION: =0;

END MANLOC;

FUNCTION MCLOCKSET:

BINARY, 1;

SENSE (KEYCHAR);

END MCLOCKSET;

TASK CLOCKSET;

MENU:=4; ISSUE (MENU);

```

```

SENSE (KEYCHAR);

MCLOCKSET:=0;

FND CLOCKSET;

FINCTION MLOGINOUT:

BINARY, 1;

SENSE (KEYCHAR);

END MLOGINOUT;

TASK LOGINOUT;

MENU:=5; ISSUE (MENU);

SENSE (KEYCHAR);

IF KEYCHAR=0 THEN KEYINMAIN:=1; END IF;

IF KEYCHAR=1 THEN TLOGIN:=1; END IF;

IF KEYCHAR=2 THEN TLOGOUT:=1; END IF;

MLOGINOUT:=0;

END LOGINOUT:

FUNCTION TLOGIN:

BINARY.1:

SENSE (KEYCHAR);

END TLOGIN;

TASK LOGIN;

ACNUM: = 0;

FOR COUNT FROM 1 TO 4:4 DO

SENSE (KEYCHAR);

ACNJM:=(ACNUM*10)+KEYCHAR;

END FOR;

IF NEXTAC=0 AND ACO=0 THEN ACO:=ACNUM; END IF;

IF NEXTAC=1 AND AC1=0 THEN AC1: = ACNUM; END IF;

IF NEXTAC=2 AND AC2=0 THEN AC2:=ACNUM; END IF;

IF NEXTAC=3 AND AC3=0 THEN AC3:=ACNUM; END IF;

IF NEXTAC=4 AND AC4=0 THEN AC4:=ACNUM; END IF;

IF NEXTAC=5 AND AC5=0 THEN AC5:=ACNUM; END IF;

IF NEXTAC=6 AND AC6=0 THEN AC6:=ACNUM; END IF;

IF NEXTAC=7 AND AC7=0 THEN AC7:=ACNUM; END IF;

IF NEXTAC=8 AND AC8=0 THEN AC8:=ACNUM; END IF;

IF NEXTAC=9 AND AC9=0 THEN AC9:=ACNUM; END IF;

NEXTAC:=NEXTAC+1;

IF NEXTAC=10 THEN NEXTAC:=0; END IF;

TLOGIN: =0:

END LOGIN;

FUNCTION TLOGOUT:

BINARY.1;

SENSE (KEYCHAR);

END TLOGOUT;

```

```

TASK LOGOUT;

ACNUM: = 0;

FOR COUNT FROM 1 TO 4:4 DO

SENSE (KEYCHAR);

ACNUM: = (ACNUM * 10) + KEYCHAR;

END FOR;

IF ACO=ACNUM THEN ACO:=0; END IF;

IF AC1=ACNUM THEN AC0:=1; END IF;

IF AC2=ACNUM THEN AC0:=2; END IF;

IF AC3=ACNUM THEN AC0:=3; END IF;

IF AC4=ACNUM THEN AC0:=4; END IF;

IF AC5=ACNUM THEN ACO:=5; END IF;

IF AC6=ACNUM THEN AC0:=6; END IF;

IF AC7=ACNUM THEN AC0:=7; END IF;

IF AC8=ACNUM THEN ACO:=8; END IF;

IF AC9=ACNUM THEN ACO:=9; END IF;

TLOGOUT:=0;

END LOGOUT;

FUNCTION POSCH:

BINARY, 1;

SENSE (NEMPOS);

IF NEWPOS=1 THEN POSCH:=1; END IF;

END POSCH;

TASK POSUPDATE;

SENSE (POSITION);

POSCH:=0;

END POSUPDATE;

FUNCTION MSGIN:

BINARY, 1;

SENSE (MSGREADY);

IF MSGREADY=1 THEN MSGIN:=1; END IF;

END MSGIN;

TASK MSGSTORE;

SENSE (MESSAGE);

ISSUE (MSGRCVD);

IF NEXTMSG=0 THEN ACO:=MESSAGE; END IF;

IF NEXTMSG=1 THEN AC1:=MESSAGE; END IF;

IF NEXTMSG=2 THEN AC2:=MESSAGE; END IF;

IF NEXTMSG=3 THEN AC3:=MESSAGE; END IF;

IF NEXTMSG=4 THEN AC4:=MESSAGE; END IF;

IF NEXTMSG=5 THEN AC5:=MESSAGE; END IF;

IF NEXTMSG=6 THEN AC6:=MESSAGE; END IF;

IF NEXTMSG=7 THEN AC7:=MESSAGE; END IF;

IF NEXTMSG=8 THEN AC8:=MESSAGE; END IF;

IF NEXTMSG=9 THEN AC9:=MESSAGE; END IF;

```

```

NEXIMSG:=NEXIMSG+1;

IF NEXIMSG=10 THEN NEXIMSG:=0; END IF;

END MSGSTORE;

```

```

CONTINGENCY LIST

WHEN KEYINMAIN : 100 MS DO KBINPMAIN;

WHEN MINTAC : 100 MS DO INTAC;

WHEN SMMANUAL : 100 MS DO MANUAL;

WHEN SMAUTO

: 100 MS DO AUTO;

: 100 MS DO POLLAUTO;

WHEN TPOLL

WHEN MLOCATION: 100 MS DO LOCATION;

WHEN IMLOCATION: 100 MS DO MANLOC;

WHEN POSCH

:1000 MS DO POSUPDATE;

WHEN MMSGDSPLY: 100 MS DO MSGDSPLY;

WHEN MCLOCKSET : 100 MS DO CLOCKSET;

WHEN MLOGINOUT: 100 MS DO LOGINOUT;

: 100 MS DO LOGIN;

WHEN TLOGIN

WHEN TLOGOUT

: 100 MS DO LOGOUT;

WHEN MSGIN

: 100 MS DO MSGSTORE;

FVD

```

62

## APPENDIX B

# (REVISED)

IDENTIFICATION

DESIGNER : "SUTTER FOX"

DATE: "05-31-84"

PROJECT : "COAST GUARD DATA LINK RECEIVER"

DESIGN CRITERIA

METRIC FIRST;

VOLUMES 1;

MONITORS 1;

ENVIRONMENT

INPUT: KEYFLG, 1, ITL; KEYCHAR, 8, ITL; MANPOS, 8, TTL;

NEWPOS, 1, TTL; POSITION, 8, TTL; MSGREADY, 1, TTL;

MESSAGE, 8, ITL; ACNUM, 8, ITL;

END INPUT;

OJTPUT: MENU, 8, TTL; POLL, 8, TTL; MSGVDT, 8, TTL; MSGRCVD, 1, TTL;

END OUTPUT;

ARITHMETIC: KEYINMAIN,8; MINTAC,8; MMSGDSPLY,8;

MLOCATION,8; MCLOCKSET,8; MLOGINOUT,8; SMMANUAL,8;

SMAUTO,8; ACO,8; AC1,8; AC2,8; AC3,8; AC4,8;AC5,8;

AC6,8; AC7,8; AC8,8; AC9,8; INTPERIOD,8; MSG0,8;

MSG1,8; MSG2,8; MSG3,8; MSG4,9; MSG5,8; MSG6,8;

MSG7,8; MSG8,8; MSG9,8;TMLOCATION,8; TLOGIN,1;

TLOGOUT,1; NEXTMSG,8; NEXTAC,8; TPOLL,1; COUNT,8;

CLOCK,8;

END ARITHMETIC:

PROCEDURES

FUNCTION KEYINMAIN:

BINARY,1;

SENSE (KEYFLG);

```

IF KEYFLG=1 THEN KEYINMAIN:=1; END IF;

END KEYINMAIN;

TASK KBINPMAIN:

MENU:=0; ISSUE (MENU);

SENSE (KEYCHAR);

IF KEYCHAR=1 THEN MINTAC :=1; END IF;

IF KEYCHAR=2 THEN MMSGDSPLY:=1; END IF;

IF KFYCHAR=3 THEN MLOCATION:=1; END IF;

IF KEYCHAR=4 THEN MCLOCKSET:=1; END IF;

IF KEYCHAR=5 THEN MLOGINOUT:=1; END IF;

KEYINMAIN: = 0;

END KBINPMAIN;

FINCTION MINTAC:

BINARY.1:

SENSE (KEYCHAR);

END MINTAC;

TASK INTAC:

MENU:=1; ISSUE (MENJ);

SENSE (KEYCHAR);

IF KEYCHAR=0 THEN KEYINMAIN:=1; END IF;

IF KEYCHAR=1 THEN SYMANUAL :=1; END IF;

IF KEYCHAR=2 THEN SMAUTO

:=1; END IF;

MINIAC:=0:

END INTAC;

FUNCTION SMMANUAL:

BINARY, 1;

SENSE (KEYCHAR);

END SMMANUAL;

TASK MANUAL;

IF ACO/=0 THEN POLL:=0; ISSUE (POLL); END IF;

IF AC1/=0 THEN POLL:=1; ISSUE (POLL); END IF;

IF AC2/=0 THEN POLL:=2; ISSUE (POLL); END IF;

IF AC3/=0 THEN POLL:=3; ISSUE (POLL); END IF;

IF AC4/=0 THEN POLL:=4; ISSUE (POLL); END IF;

IF AC5/=0 THEN POLL:=5; ISSUE (POLL); END IF;

IF AC6/=0 THEN POLL:=6; ISSUE (POLL); END IF;

IF AC7/=0 THEN POLL:=7; ISSUE (POLL); END IF;

IF AC8/=0 THEN POLL:=8: ISSUE (POLL); END IF;

IF AC9/=0 THEN POLL:=9; ISSUE (POLL); END IF;

SMMANUAL: = 0;

```

END MANUAL;

```

FUNCTION SMAUTO:

BINARY, 1;

SENSE (KEYCHAR);

END SMAUTO;

TASK AUTO;

MENU:=2; ISSUE (MENU);

SENSE (KEYCHAR);

IF KEYCHAR=0 THEN KEYINMAIN := 1; END IF;

IF KEYCHAR=1 THEN INTPERIOD := 30 ; END IF;

IF KEYCHAR=2 THEN INTPERIOD := 20; END IF;

IF KEYCHAR=3 THEN INTPERIOD := 15; END IF;

IF KEYCHAR=4 THEN INTPERIOD := 10; END IF;

IF KEYCHAR=5 THEN INTPERIOD := 5; END IF;

IF KEYCHAR=6 THEN INTPERIOD := 1; END IF;

SENSE (CLOCK);

INTTIME := CLOCK;

SMAUTO: = 0;

TPOLL:=1;

END AUTO;

FUNCTION TPOLL:

BINARY, 1;

SENSE (CLOCK);