# **Calhoun: The NPS Institutional Archive**

# **DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2022-03

# ASIC BENCHMARKING FOR PROPOSED LIGHTWEIGHT CRYPTOGRAPHY STANDARD XOODYAK

Wakeland, Michael C.

Monterey, CA; Naval Postgraduate School

https://hdl.handle.net/10945/69718

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

# THESIS

# ASIC BENCHMARKING FOR PROPOSED LIGHTWEIGHT CRYPTOGRAPHY STANDARD XOODYAK

by

Michael C. Wakeland

March 2022

Thesis Advisor: Co-Advisor: Gaylord Henry Chad A. Bollmann

Approved for public release. Distribution is unlimited.

| <b>REPORT DOCUMENTATION PAGE</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                 |              | Form Approved OMB<br>No. 0704-0188                     |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------|--------------------------------------------------------|--|

| Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington, DC 20503.                                                                                                                                                                                                                                                                                                               |                                                                                 |              |                                                        |  |

| 1. AGENCY USE ONLY<br>(Leave blank)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2. REPORT DATE<br>March 2022                                                    | 3. REPORT TY | <b>PE AND DATES COVERED</b><br>Master's thesis         |  |

| <ul> <li>4. TITLE AND SUBTITLE<br/>ASIC BENCHMARKING FO<br/>CRYPTOGRAPHY STANDA</li> <li>6. AUTHOR(S) Michael C. W</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                 |              | 5. FUNDING NUMBERS                                     |  |

| 7. PERFORMING ORGAN<br>Naval Postgraduate School<br>Monterey, CA 93943-5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ZATION NAME(S) AND ADDF                                                         | RESS(ES)     | 8. PERFORMING<br>ORGANIZATION REPORT<br>NUMBER         |  |

| ADDRESS(ES)<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ORING AGENCY NAME(S) AN                                                         |              | 10. SPONSORING /<br>MONITORING AGENCY<br>REPORT NUMBER |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>TES</b> The views expressed in this t<br>and Department of Defense or the U. |              | he author and do not reflect the                       |  |

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT12b. DISTRIBUTIONApproved for public release. Distribution is unlimited.12b. DISTRIBUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                 |              | 12b. DISTRIBUTION CODE<br>A                            |  |

| Approved for public release. Distribution is unlimited. A<br><b>13. ABSTRACT (maximum 200 words)</b><br>The U.S. National Institute of Standards and Technology (NIST) has initiated a process to standardize a<br>"lightweight" cryptographic algorithm. Lightweight algorithms are designed for use in gate and<br>performance-limited devices. This report compares an Application Specific Integrated Circuit (ASIC)<br>implementation of the NIST Advanced Encryption Standard-128 (AES-128) and a competition finalist,<br>Xoodyak. Implementations were written in SystemVerilog. Testing was performed using Vivado field<br>programmable gate array simulations. Twenty six instances of AES and Xoodyak were built. These builds<br>were optimized for throughput, clock frequency, and cell area, respectively. Size and performance<br>benchmarks were obtained from builds using an 5nm and 16nm ASIC technology. Results indicate Xoodyak<br>is capable of higher throughput than AES-128 while using a lower cell area. |                                                                                 |              |                                                        |  |

| 14. SUBJECT TERMS<br>lightweight, encryption, lightweight encryption, benchmarking, NIST, security, throughput,<br>cell area, AES, Xoodyak, hardware, ASIC, SystemVerilog, hardware description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                 |              | 83                                                     |  |

| 17. SECURITY18. SECURITY19. SECURITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |              | 16. PRICE CODE<br>20. LIMITATION OF                    |  |

| CLASSIFICATION OF<br>REPORT<br>UnclassifiedCLASSIFICATION OF THIS<br>PAGE<br>UnclassifiedCLASSIFICATION OF<br>ABSTRACT<br>Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                 |              | ION OF ABSTRACT<br>UU                                  |  |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

## Approved for public release. Distribution is unlimited.

# ASIC BENCHMARKING FOR PROPOSED LIGHTWEIGHT CRYPTOGRAPHY STANDARD XOODYAK

Michael C. Wakeland Lieutenant, United States Navy BS, University of Illinois at Urbana-Champaign, 2015

Submitted in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

# NAVAL POSTGRADUATE SCHOOL March 2022

Approved by: Gaylord Henry Advisor

> Chad A. Bollmann Co-Advisor

Douglas J. Fouts Chair, Department of Electrical and Computer Engineering

# ABSTRACT

The U.S. National Institute of Standards and Technology (NIST) has initiated a process to standardize a "lightweight" cryptographic algorithm. Lightweight algorithms are designed for use in gate and performance-limited devices. This report compares an Application Specific Integrated Circuit (ASIC) implementation of the NIST Advanced Encryption Standard-128 (AES-128) and a competition finalist, Xoodyak. Implementations were written in SystemVerilog. Testing was performed using Vivado field programmable gate array simulations. Twenty six instances of AES and Xoodyak were built. These builds were optimized for throughput, clock frequency, and cell area, respectively. Size and performance benchmarks were obtained from builds using an 5nm and 16nm ASIC technology. Results indicate Xoodyak is capable of higher throughput than AES-128 while using a lower cell area.

# **TABLE OF CONTENTS**

| I.   | INT | RODUCTION1                       |

|------|-----|----------------------------------|

|      | А.  | OVERVIEW1                        |

|      | B.  | MOTIVATION2                      |

|      | C.  | SCOPE                            |

|      | D.  | THESIS ORGANIZATION              |

| II.  | BAC | CKGROUND                         |

|      | A.  | OVERVIEW5                        |

|      | B.  | AES IMPLEMENTATION5              |

|      |     | 1. Round Based6                  |

|      |     | 2. Functionality                 |

|      | C.  | HARDWARE DESIGN DECISIONS7       |

|      |     | 1. S-box Instance7               |

|      |     | 2. Default Cipher Configuration7 |

|      |     | 3. Vector Key Generation8        |

|      | D.  | AES BEHAVIORAL VERIFICATION9     |

|      | E.  | SUMMARY10                        |

| III. | ME  | <b>FHODS</b> 11                  |

|      | A.  | OVERVIEW11                       |

|      | B.  | THE XOODYAK ALGORITHM11          |

|      | C.  | PRIMITIVES14                     |

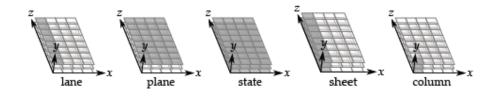

|      |     | 1. <i>State</i> (as a concept)14 |

|      |     | 2. Color Bytes15                 |

|      |     | 3. Core f15                      |

|      | D.  | DESCRIBING A FUNCTION CALL15     |

|      |     | 1. Level 3 Function Calls15      |

|      |     | 2. Level 2 Function Calls17      |

|      |     | 3. Level 1 Function Calls19      |

|      |     | 4. Top Level Instance            |

|      | E.  | IMPLEMENTATION                   |

|      |     | 1. Instance Parameters23         |

|      |     | 2. <i>State</i> Machines24       |

|      |     | 3. User Operation of Xoodyak25   |

|      |     | 4. Structural Datapath26         |

|      |     | 5. Verification                  |

|      | F.  | SUMMARY                          |

| IV.  | RES    | ULTS    |                                                                 | 33 |

|------|--------|---------|-----------------------------------------------------------------|----|

|      | А.     | CON     | MPARATIVE FUNCTIONALITY ANALYSIS                                | 33 |

|      | В.     | SUB     | JECTIVE STRUCTURAL ANALYSIS                                     | 34 |

|      | C.     | IMP     | ORTANT CONSIDERATIONS FOR BENCHMARKING                          | 35 |

|      |        | 1.      | Build Qualification for Benchmarking                            | 35 |

|      |        | 2.      | Precision Limitations on Results                                | 36 |

|      |        | 3.      | Startup Delays, Streaming Mode, and Performance                 | 36 |

|      |        | 4.      | Adjustments for AES KeyExpansion                                | 36 |

|      | D.     | PAR     | RAMETER ANALYSIS                                                | 37 |

|      |        | 1.      | Throughput Analysis                                             | 39 |

|      |        | 2.      | Cell Area Analysis                                              | 39 |

|      | Е.     | ALT     | <b>TERNATIVE COMPARISONS</b>                                    | 40 |

|      |        | 1.      | Alternative: Xoodyak and AES-Galois Counter Mode<br>(AES-GCM)   | 40 |

|      |        | 2.      | Alternative: Enc/Dec Xoodyak only and AES Core                  |    |

|      | F.     |         | IMARY                                                           |    |

|      |        |         |                                                                 |    |

| V.   | CON    | ICLUS   | ION                                                             | 43 |

|      | А.     | ASS     | ESSMENT OF GOALS                                                | 43 |

|      | В.     | FUT     | URE WORK                                                        |    |

|      |        | 1.      | Remove Fixed Length String Requirement                          |    |

|      |        | 2.      | Perform a More Extensive Verification                           | 44 |

|      |        | 3.      | Reduce the Xoodyak Startup Clocks from Two to One               | 44 |

|      |        | 4.      | Perform an ASIC Benchmarking of AES with Galois<br>Counter Mode | 44 |

| APP  | ENDIX  | X A. CC | DDE REPOSITORY                                                  | 45 |

| APP  | ENDIX  | K B, DE | FINITION OF XOODOO                                              | 47 |

| APP  | ENDIX  | K C VE  | CTOR EXAMPLE                                                    | 49 |

| APP  | ENDIX  | K D. AF | S AND XOODYAK BUILD METHODOLOGY                                 | 53 |

| APP  | ENDIX  | K E. BU | ILD RESULTS                                                     | 55 |

| APP  | ENDIX  | K F. SA | MPLE BUILD IMAGES                                               | 57 |

| LIST | r of r | EFERI   | ENCES                                                           | 61 |

| INIT | TAL D  | ISTRI   | BUTION LIST                                                     | 63 |

# LIST OF FIGURES

| Figure 1.  | Top Level AES-128 Process Diagram                             | 8  |

|------------|---------------------------------------------------------------|----|

| Figure 2.  | Function Verification Process Flow Diagram                    | 9  |

| Figure 3.  | Definition of Xoodyak as Cyclist with Parameters. Source: [5] | 12 |

| Figure 4.  | Use of Xoodyak Functions for Hashing. Source: [5]             | 13 |

| Figure 5.  | Use of Xoodyak Functions for AEAD. Adapted from [5]           | 14 |

| Figure 6.  | <i>Up</i> Function Definition. Source: [5]                    | 16 |

| Figure 7.  | Down Function Definition. Source: [5].                        | 17 |

| Figure 8.  | AbsorbAny Function Definition. Source: [5]                    | 18 |

| Figure 9.  | Crypt Function Definition. Source: [5]                        | 18 |

| Figure 10. | SqueezeAny Function Definition. Source: [5]                   | 19 |

| Figure 11. | AbsorbKey Function Definition. Source: [5]                    | 20 |

| Figure 12. | Absorb Function Definition. Source: [5].                      | 20 |

| Figure 13. | Encrypt Function Definition. Source: [5]                      | 21 |

| Figure 14. | Decrypt Function Definition. Source: [5]                      | 21 |

| Figure 15. | Squeeze Function Definition. Source: [5]                      | 21 |

| Figure 16. | SqueezeKey Function Definition. Source: [5]                   | 22 |

| Figure 17. | Ratchet Function Definition. Source: [5]                      | 22 |

| Figure 18. | Cyclist Function Instantiation. Source: [5].                  | 22 |

| Figure 19. | Pre-Permute Process Diagram                                   | 27 |

| Figure 20. | Permute Process Diagram                                       | 29 |

| Figure 21. | Reconcatenation Logic                                         | 30 |

| Figure 22. | Post-Permute Process Diagram                                  | 31 |

| Figure 23. | Xoodyak Data Verification Process                             | 32 |

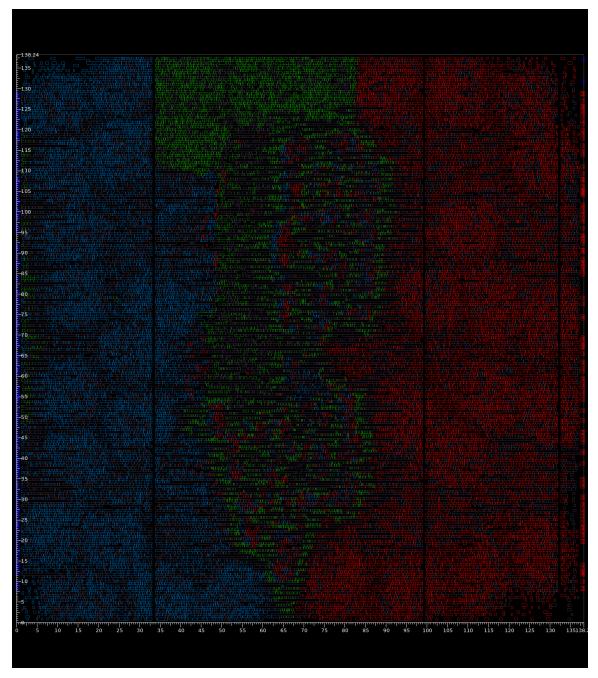

| Figure 24. | A-03c Die Space. Source: [9]. | 57 |

|------------|-------------------------------|----|

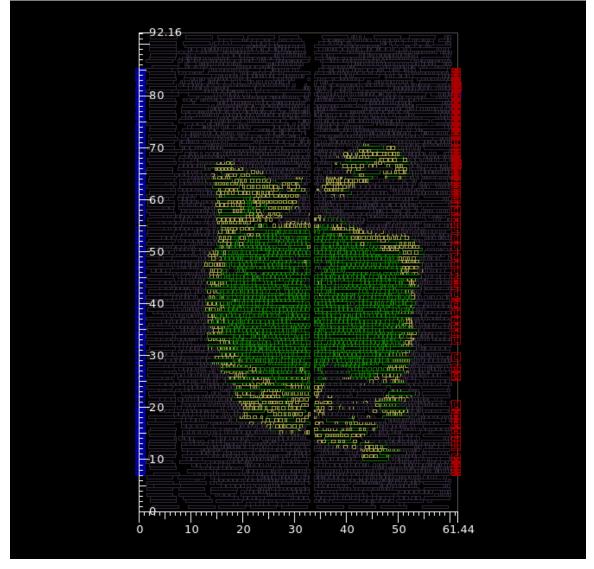

| Figure 25. | X-07b Die Space. Source: [9]  | 58 |

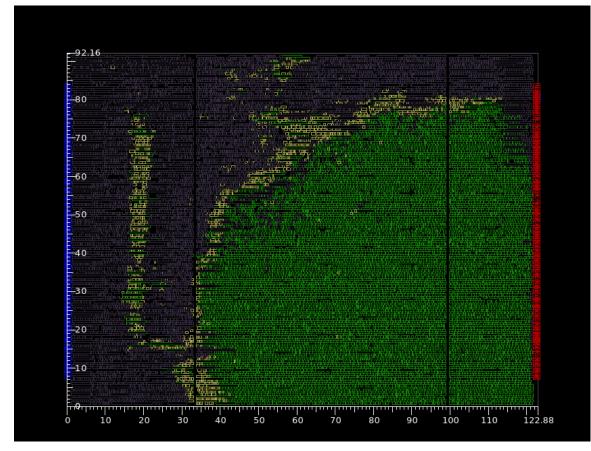

| Figure 26. | X-08a Die Space. Source: [9]  | 59 |

# LIST OF TABLES

| Table 1.  | AES-128 Function Call Decodes                                                       | 6  |

|-----------|-------------------------------------------------------------------------------------|----|

| Table 2.  | AES-128 Function Return Decodes                                                     | 7  |

| Table 3.  | AES Datapath Flow Order                                                             | 8  |

| Table 4.  | Validated Function Transitions1                                                     | 0  |

| Table 5.  | Organization of Xoodyak Function Calls. Adapted from [5]1                           | 3  |

| Table 6.  | Xoodyak Parameter Length Summary. Adapted from [5]2                                 | .4 |

| Table 7.  | Xoodyak Opcode Decode and Mode Restriction2                                         | 4  |

| Table 8.  | Functions with 1-Clock Stream Delays                                                | .6 |

| Table 9.  | Functions That Make the Next Non-Identical Function Have a 1-<br>Clock Stream Delay | 6  |

| Table 10. | Functions with a 4-Clock or 12-clock Stream Delay by Default2                       | .6 |

| Table 11. | Function Comparison - Xoodyak and AES-1283                                          | 4  |

| Table 12. | Streaming Results—5nm Technology. Adapted from [9]3                                 | 7  |

| Table 13. | Streaming Results—16nm Technology. Adapted from [9]3                                | 7  |

| Table 14. | Non-Streaming Results—5nm Technology. Adapted from [9]3                             | 8  |

| Table 15. | Cell Area Results—16nm Technology. Adapted from [9]3                                | 8  |

| Table 16. | Cell Area Results - 5nm Technology. Adapted from [9]3                               | 8  |

| Table 17. | Cell Area Results - 16nm Technology. Adapted from [9]3                              | 8  |

# LIST OF ACRONYMS AND ABBREVIATIONS

| AEAD    | authenticated encryption with associated data          |

|---------|--------------------------------------------------------|

| AES     | Advanced Encryption Standard                           |

| AES-128 | Advanced Encryption Standard, 128-bit security variant |

| ASIC    | application specific integrated circuit                |

| FSM     | finite state machine                                   |

| LWC     | Lightweight Cryptography Competition                   |

| NIST    | National Institute of Standards and Technology         |

| RTL     | register transfer level                                |

| S-box   | substitution box                                       |

# **EXECUTIVE SUMMARY**

The National Institute of Standards and Technology is holding a competition to create a lightweight cryptography standard. The scope of the competition contains both authenticated encryption with associated data, and hashing. Xoodyak is a cryptographic algorithm and finalist in the competition.

In this work, we wrote register transfer level code to reflect behavior for Xoodyak at a synthesizable hardware level. The complete module is operable by a user and capable of processing arbitrary length and numbered strings. We also wrote register transfer level code for the Advanced Encryption Standard, which is similarly operable. Centaur Technologies of Austin, Texas created 26 application specific integrated circuit builds based on this code, which were then compared on a throughput, cell area, and leakage power basis. The results show that Xoodyak builds can be optimized for size or throughput, and these tailored builds are either significantly smaller or faster than Advanced Encryption Standard across both 5nm and 16nm technology. Algorithm security was not evaluated within the scope of this research.

# ACKNOWLEDGMENTS

I wish to thank my advisors, G. Glenn Henry and Commander Chad Bollmann, for their mentorship over the last eighteen months. They showed great interest and vigor which inspired superior results. However, I think the most important thing is that I both learned something and thoroughly enjoyed the process. They greatly facilitated both goals. The experience was similarly valuable; not many had the chance to get a build of their graduate school projects.

I also wish to specifically recognize the efforts and resources of Jim Donahue and Centaur Technologies in making the builds. His builds furthered the success of this project and gave us the hard data we needed.

Lastly, I offer thanks for the fellowship of the following friends and colleagues who materially impacted my journey, both directly and indirectly.

LT Brandy Allain, USN Ms. Marcea Ascencio, USAF CAPT William Clive Blodgett, Jr., USN CAPT Garrett Farman, USN CAPT Dave Huljack, USN Capitão-tenente Madjer & Juliana Martins, MDB LT Karina Monroe, USN Professor John Roth CAPT Zoah Scheneman, USN ENS Wyatt Smith, USN LT Tim Stevenson, USN

# I. INTRODUCTION

#### A. OVERVIEW

Encryption has been used to ensure the secrecy of information since antiquity. Two thousand years after the Caesar Cipher, the National Institute of Standards and Technology (NIST) adopted a subset of the Rijndael cipher as Advanced Encryption Standard (AES) [1]. AES is the most common and thoroughly vetted block cipher available today. Block ciphers ensure data confidentiality, but not integrity or authenticity.

TLS 1.3 and other modern security systems require Authenticated Encryption with Associated Data (AEAD), which provides integrity and authenticity in addition to confidentiality [2]. The use of AES with AEAD requires more than the AES block cipher alone<sup>1</sup> [3]. These additional requirements can limit throughput and add computational burden to resource-constrained devices. The NIST Lightweight Cryptography Competition (LWC) seeks to alleviate these concerns by creating a standard for both AEAD and hashing [4].

Daemen et al. created Rijndael as well as Xoodyak, which is one finalist in the NIST competition [5]. Xoodyak is a family of mathematical functions that are synthesizable in hardware. Xoodyak can be used for both AEAD and hashing. The principal characteristic in Xoodyak is a 384-bit *State*. The *State* undergoes minor modification at the start of every function call and is then distributed by a permute function which performs various Boolean XORs and round key additions in 12 iterations. The output is then combined with an input text to "absorb" a string or generate an output text. This process repeats, perhaps multiple times, depending on the length of the input string, until all text is processed. ASIC benchmarking can determine the performance relationship between Xoodyak and AES, which is the primary goal of this work.

<sup>&</sup>lt;sup>1</sup> NIST recommends the use of Galois Counter Mode to mode to perform AEAD with an AES core, as described in ref. [3], NIST Special Publication 800–38D Ch 7: GCM Specification

#### **B.** MOTIVATION

The Fleet has a need for lightweight, scalable encryption to support time-critical and Internet of Things applications. Higher throughput is one of the goals of the LWC, which translates to smaller encryption delays in operational use. If selected as the lightweight cryptographic standard, Xoodyak will be positioned to provide AEAD with low latency to fill these requirements. Quantifying the relative gain over the existing standard, AES, is a critical benchmark for assessing algorithm performance.

The hardware builds which we created will also provide the NIST Lightweight Cryptography Competition with ASIC benchmarking data. This data will better inform NIST decision makers about real performance marks for Xoodyak in an isolated standardto-proposed-standard comparison in relation to AES-128.

# C. SCOPE

This research evaluated the performance and size of the AES-128<sup>2</sup> standard in comparison to the Xoodyak cryptography suite.<sup>3</sup>

This comparison was selected because AES is the established technical standard, and Xoodyak is a proposed technical standard for lightweight cryptography. Consequently, the direct comparison is between an established and proposed standard.

ASIC benchmarks were performed by Centaur Technologies of Austin, Texas. Our research was concerned with implementing cores and measuring parameters to assess performance. These parameters were cell area, cell count, and clock frequency. The research did not evaluate any dynamic power consumption or security claims.

<sup>&</sup>lt;sup>2</sup> In the context of this document, "AES," "AES core," or "AES standard" refers to statements about the entire Advanced Encryption Standard regardless of key size (128, 192, or 256 bits). Every use of AES refers to the block cipher only, not AES as a part of a larger AEAD scheme such as that described in the NIST Recommendation [3]. "AES-128" specifically refers to an AES standard algorithm using a 128-bit key size, or a build that only supports 128-bit true keys.

<sup>&</sup>lt;sup>3</sup> As described in "Xoodyak, a Lightweight Encryption Scheme." - Algorithm 2, page 9 [5]. The suite includes every possible combination of functions with arbitrary input lengths and arbitrary order, so long as the order is algorithmically feasible.

# D. THESIS ORGANIZATION

Chapter II describes the control implementation of the AES core, which includes the *KeyExpansion, Encrypt*, and *Decrypt* modules. Chapter III describes the Xoodyak algorithm in theory and hardware architecture. Chapter IV describes full benchmarking results and comparisons. Chapter V is the conclusion. Appendix A contains a link to the author's GitHub repository containing the full register transfer level (RTL) description for both AES and Xoodyak. Appendix B is a reproduction of the Xoodoo *Permute* function as described in [3]. Appendix C is an example series of function calls, evaluated using the Xoodyak hardware instance. Appendix D provides the technical build methodology employed by Centaur Technologies in creating the hardware instances. Appendix E contains the full list of AES-128 and Xoodyak builds and benchmarking data. Appendix F provides selected die plot images of various hardware builds.

# II. BACKGROUND

#### A. OVERVIEW

The purpose of this research was to evaluate Xoodyak performance in relation to AES. A direct evaluation required RTL instantiations of both algorithms and subsequent builds for benchmarking. A "build" is the collection of transistors and wires which perform the described function, demonstrating the size and performance on any resulting silicon chip. Only minor steps remain before a build can be released into manufacturing. This chapter concerns the AES instance, from both a structural overview and user operation perspective.

The AES algorithm supports 128, 192, and 256-bit key lengths, but the 196 and 256-bit key lengths require more hardware to implement. They also require more rounds, or iterations of the algorithm, to complete an encryption cycle, which increases cell area and decreases throughput. Xoodyak only claims 128 bits of security. Our AES implementation therefore only supports 128-bit key lengths to obtain a more equivalent perspective.

The AES structure is designed to accomplish one AES round every clock, as described in the AES Standard. We also made several design decisions, particularly regarding substitution-boxes (S-boxes) which are discussed in more detail in Section II.C.

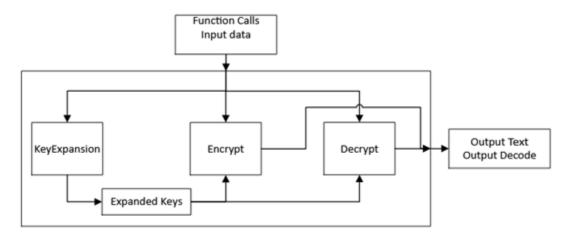

The separate *KeyExpansion, Encrypt*, and *Decrypt* modules are wired together in a manner that supports continuous operation. The full AES module is fully operational; users can expand keys, then encrypt or decrypt an arbitrary length string.

Lastly, the completed AES instance was verified using a combination of the sample test vectors in the AES Standard and hand verification using MATLAB.

# **B. AES IMPLEMENTATION**

NIST FIPS - 197 forms the basis of AES [1]. AES, including AES-128, is publicly understood. Our discussion regarding AES is therefore limited to general approach, functionality, and notable design decisions.

#### 1. Round Based

Our implementation of AES sought to match the technical requirements of [1] in a functional, ASIC-instantiated RTL model. The implemented datapath closely resembles the steps in [1] for all modules. Each module uses a round-based approach, where one clock completes one round. For example, one clock in the *Encrypt* module accomplishes one *SubBytes*, *ShiftRows*, *MixColumns*, and *AddRoundKey* transformation. Ten clocks are required to accomplish the entire *Cipher* (*Encrypt*) operation. *Inverse Cipher* (*Decrypt*) and *KeyExpansion* require ten and 11 clocks respectively under the same paradigm.

#### 2. Functionality

Our AES-128 implementation includes hardware to implement the *KeyExpansion*, *Encrypt*, and *Decrypt* functions. The modules are interlinked for operational use. Users can call various functions based on a 2-bit opcode. The appropriate data must be provided synchronously with the function call. The opcodes are listed in Table 1.

| Functions [1:0] |         |  |  |

|-----------------|---------|--|--|

| Opcode          | AES     |  |  |

| 0               | Idle    |  |  |

| 1               | Encrypt |  |  |

| 2               | Decrypt |  |  |

| 3               | Keys    |  |  |

Table 1.AES-128 Function Call Decodes

Ingesting a valid opcode creates a text output for *Encrypt* or *Decrypt* calls. Function durations are counter-based and determinate. Opcode 3 calls for *KeyExpansion* create no output text because the expanded keys are held in the module for future use. However, an output text decoder informs the user when *KeyExpansion* is complete. The return decode is provided synchronously with the output text for *Encrypt* and *Decrypt* calls. Table 2 is a full readout of output function decodes. Throughput and cell area results are detailed in Chapter IV.

| Returns [1:0] |            |  |

|---------------|------------|--|

| Decode        | AES        |  |

| 0             | Invalid    |  |

| 1             | Ciphertext |  |

| 2             | Plaintext  |  |

| 3             | Keys       |  |

Table 2.

AES-128 Function Return Decodes

# C. HARDWARE DESIGN DECISIONS

Several design decisions had to be made when designing the AES hardware instance. For example, accomplishing one AES round per clock was a conscious choice. Two deliberate choices involved how to handle the forward and inverse S-box, and whether to reverse certain commutable steps in the *Decrypt* module. The most significant design choice was to hold expanded keys in a register, rather than generate keys "on the fly."

#### 1. S-box Instance

The *Encrypt* module contains a forward Rijndael S-box instance. The S-box is shared with the *KeyExpansion* module for use in key generation. The Inverse S-box is separately instanced in the *Decrypt* module, rather than being computed as a derivative of the forward S-box.

# 2. Default Cipher Configuration

Certain AES steps are commutable [1]. This implementation performed the standard function flows with no use of "equivalencies." The *Encrypt/Decrypt* datapath flows are summarized in Table 3.

|      | AES Flow        |               |  |

|------|-----------------|---------------|--|

| Step | Encrypt Decrypt |               |  |

| 1    | SubBytes        | InvShiftRows  |  |

| 2    | ShiftRows       | InvSubBytes   |  |

| 3    | MixColumns      | AddRoundKey   |  |

| 4    | RoundKey        | InvMixColumns |  |

Table 3.AES Datapath Flow Order

#### **3.** Vector Key Generation

Keys are provided in a complete set to the *Encrypt* and *Decrypt* modules. Calls to *Encrypt* or *Decrypt* use the stored keys for computation. One key is generated on every clock. The expansion is complete when all 11 keys are generated. The keys are held in registers, comprising 11 128-bit registers in total. These stored keys comprise a large part of the *KeyExpansion* hardware. The keys are not "flushed" after an encryption cycle. This allows multiple cipher operations to use the same key vector. Figure 1 visualizes both how key vectors are shared with both *Encrypt* and *Decrypt*, and shows the high-level structure of the AES-128 module.

Figure 1. Top Level AES-128 Process Diagram

Table reflects both the default datapath per the AES Standard, and the implementation in the *Encrypt* and *Decrypt* Modules. Adapted from [1].

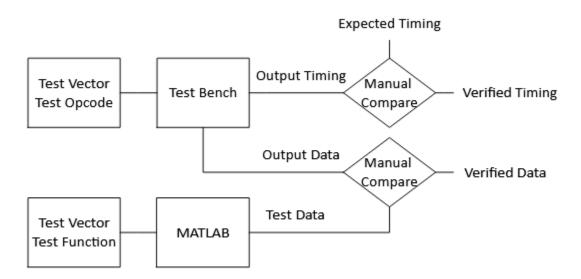

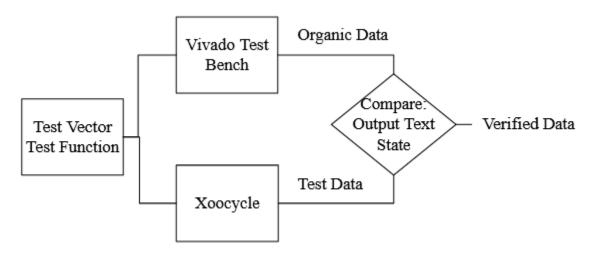

# D. AES BEHAVIORAL VERIFICATION

Our AES-128 instance supports three function calls and idle. Vivado is an RTL design suite by Xilinx for analysis and synthesis of RTL logic [6]. Each function was individually verified through Vivado using MATLAB, [1], and [7]. The MATLAB script in [7] was assumed to be correct after our detailed visual inspection and verification of intermediate and final outputs from the sample test vectors in [1]. Our individual vector results were verified by hand using a combination of the MATLAB code in [7] and Vivado waveform simulation. The waveform window was examined for correct output text, opcode/decode/operation congruence, and timing. Figure 2 visualizes this process.

Figure 2. Function Verification Process Flow Diagram

After individual functions were validated, all possible sequences of function calls were performed in Vivado with MATLAB verification. The data used was the default test vector in the AES Standard [1]. The nine distinct function transitions were performed to directly test for errors in control logic. Table 4 describes every possible function transition. Idle transitions are not included because they are no-ops. The output pins were then examined for correctness across the entire function sequence.

| Function transitions |              |  |

|----------------------|--------------|--|

| Call N               | Call N+1     |  |

| KeyExpansion         | KeyExpansion |  |

| KeyExpansion         | Encrypt      |  |

| KeyExpansion         | Decrypt      |  |

| Encrypt              | KeyExpansion |  |

| Encrypt              | Encrypt      |  |

| Encrypt              | Decrypt      |  |

| Decrypt              | KeyExpansion |  |

| Decrypt              | Encrypt      |  |

| Decrypt              | Decrypt      |  |

Table 4.Validated Function Transitions

# E. SUMMARY

This chapter discussed a stable control to compare with Xoodyak, the proposed lightweight cryptography standard. Our hardware instance of AES-128 serves as that control basis. This operational AES-128 module forms a basis on which to compare to an operational Xoodyak module. The algorithmic definition and hardware construction of Xoodyak is the topic of the next chapter.

# III. METHODS

#### A. OVERVIEW

The purpose of this research was to benchmark the Xoodyak suite against the AES-128 block cipher. The principal component of this work was the development of a Xoodyak hardware instance. Creating the Xoodyak instance required two main efforts. The first part was understanding the Xoodyak algorithm and making design decisions on supportability. This required a thorough investigation of the formal algorithm definitions which make up Xoodyak which are described in Section B.

The second part was writing the RTL code that supported those requirements. Section E describes the implementation from a structural and operational perspective using RTL logic in synthesizable SystemVerilog. Appendix A contains links to the full RTL description. These new implementations were built using the same tools and circuit modules as our AES-128 instance.

The Xoodyak module is fully operational, just like our AES-128 instance. This includes the capability to handle arbitrary length strings across all AEAD and hashing functions using two inputs, text, and opcode. Verification was conducted by hand examination and C code. An example series of function calls with associated data is available in Appendix C.

#### **B.** THE XOODYAK ALGORITHM

The Xoodyak algorithm is an instance of the *Cyclist* algorithm with specific parameters [5]. *Cyclist* is made up of a series of mathematical function calls. The algorithmic instantiation of Xoodyak is given in Figure 3.

**Definition 2.** XOODYAK is CYCLIST  $[f, R_{hash}, R_{kin}, R_{kout}, \ell_{ratchet}]$  with

- f = XOODOO[12] of width 48 bytes (or b = 384 bits)

- R<sub>hash</sub> = 16 bytes

- R<sub>kin</sub> = 44 bytes

- R<sub>kout</sub> = 24 bytes

- *l*<sub>ratchet</sub> = 16 bytes

Figure 3. Definition of Xoodyak as Cyclist with Parameters. Source: [5].

Xoodyak, being a derivative of the *Cyclist* algorithm, operates through what we termed "level 1" function calls.<sup>4</sup> We have parsed these functions according to levels for clarity, but this is not a distinction that exists in the NIST submission. All functions, and their precise relationships, are given in Algorithm 2 of [5]. Level 1 function calls are similar to *KeyExpansion, Encrypt*, or *Decrypt* function calls in AES. Level 1 functions take user inputs and create outputs. Lower-level functions are described in Algorithm 3 of [5] as "internal interfaces."

The higher-level function calls heavily overlap with lower-level calls. Two examples of level 1 functions include *Encrypt* and *Decrypt*, which both call the *Crypt* function on level 2. Every level 1 function call calls *Xoodoo*, the *Permute* core of Xoodyak, if the phase is "DOWN" at the start of the call.<sup>5</sup> This also sets the Xoodyak phase to "UP." Table 5 shows the relative relationship between all the various nested functions.

$<sup>^4</sup>$  Function calls in this section specifically refer to *algorithm* function calls, not hardware functions called by an opcode and supplied by a user.

<sup>&</sup>lt;sup>5</sup> *Xoodoo* and *Permute* are used interchangeably in this document. Likewise, permutation refers to the results of *Xoodoo*, and the verb "to permute" a string means to provide a *State* input to *Xoodoo* and collect the result.

| Top Level Instantiation |         |                |         |  |

|-------------------------|---------|----------------|---------|--|

| Cyclist (               | (keyed) | Cyclist (Hash) |         |  |

|                         | Le      | vel 1          |         |  |

| AbsorbKey               | Decrypt | Squeeze        | Ratchet |  |

| Absorb                  | Encrypt | SqueezeKey     | -       |  |

|                         | Level 2 |                |         |  |

| AbsorbAny               | Crypt   | SqueezeAny     | -       |  |

|                         | Level 3 |                |         |  |

| Split                   | Down    | Up             | -       |  |

|                         | Core    |                |         |  |

| f (Xoodoo)              | -       | -              | -       |  |

Table 5. Organization of Xoodyak Function Calls. Adapted from [5].

The Daemen et al. formal Xoodyak submission is described by a specific series of function calls. However, users can call functions in arbitrary order. For example, while {*Cyclist*, *Crypt*, *Crypt*, *Absorb*, *Squeeze*, *Absorb*} is not a series of function calls in the AEAD or hash submission, it is still algorithmically possible. The formal AEAD and hash function calls for the submission are described, along with their parameters, in Figures 4 and 5.

When used in hash mode as described in Figure 3, the Xoodyak algorithm can produce any *n*-byte hash value, based on the absorption of any arbitrary length associated data input x [5]. The *Cyclist* function generates a string of all zeros as the arguments are null. The *Absorb* function call described absorbs an arbitrary length string x into the *State*. The *Squeeze* function call generates an *n*-byte length hash, depending on the *State*.

```

Cyclist(\epsilon, \epsilon, \epsilon)

Absorb(x)

Squeeze(n)

```

Figure 4. Use of Xoodyak Functions for Hashing. Source: [5].

Figure 4 describes the use of Xoodyak in AEAD. The fundamentals of the process are the same, supplying arguments represented by a variable name. AEAD requires a key

*K*, which is null in hash mode. Several inputs are parameterized. The parameters are discussed in greater detail in the implementation, Section E.1.

| CYCLIST( $K$ , id, $\epsilon$ )<br>ABSORB(nonce)<br>ABSORB( $A$ )<br>$C \leftarrow \text{ENCRYPT}(P)$<br>$T \leftarrow \text{SQUEEZE}(t)$<br>return $(C,T)$ | CYCLIST(K, id, $\epsilon$ )<br>ABSORB(nonce)<br>ABSORB(A)<br>$P \leftarrow \text{DECRYPT}(C)$<br>$T' \leftarrow \text{SQUEEZE}(t)$<br>if $T = T'$ then<br>return $P$<br>else<br>return $\perp$ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 5. Use of Xoodyak Functions for AEAD. Adapted from [5].

# C. PRIMITIVES

A common thread unites Xoodyak operations: the relationship between two objects and a permutation. The first object is the *State*, which is a vector that changes value depending on every function call since instantiation. The second are color bytes, which provide domain separation at the start of each function call. In any function, the *State* undergoes a color byte modification, is permuted, and then has another color byte modification.<sup>6</sup>

## 1. *State* (as a concept)

The *State* is the fundamental object described in Xoodyak. The *State* has three properties: value, length, and phase. In Xoodyak, the *State* is always 384 bits long and the value is determined by process history. The process history is the sequence of function calls, in order, with arguments, up to the present call. The phase of *State* is either "UP" or "DOWN." The phase can be flipped from "UP" to "DOWN" by the *Down* internal function, or from "DOWN" to "UP" by the *Up* internal function. Applying the *Up* function

<sup>&</sup>lt;sup>6</sup> The color bytes are only active the first "pass" through a function. For strings of greater length than the maximum operation length (given by parameters in Figure 3, Table 6) multiple passes are required.

to *State* whose phase is "UP" creates a no-op. Applying the *Down* function to *State* whose phase is "DOWN" is not algorithmically possible.

#### 2. Color Bytes

An Up color byte,  $C_U$ , is applied via bitwise XOR to the least significant byte of the *State* depending on the function called. For operations with multiple calls to Up and Down, the  $C_U$  is only applied before the first call to Up.

#### 3. Core f

The *f* function is an instance of the *Xoodoo/Permute* function summarized by Algorithm 1 [5]. It manipulates the *State* based on a set operation and pre-defined round constants. The *State* manipulation performed by *Xoodoo* forms the core of the Xoodyak algorithm. For Xoodyak, 12 rounds are required to complete the *f* function. Algorithm 1 is reproduced fully in Appendix B.

# D. DESCRIBING A FUNCTION CALL

Level 1 function calls perform a modification of the *State*, then permute the *State* through *Up* and then Down. Function calls with large-sized arguments endure this process multiple times. The precise nature of whether an *Up* function is used on a call, or what modifications are performed before or after it, are specific to the function, the length of the function call, and the phase of the *State* when the call is processed. Each level of function call must be described in detail. The discussion must begin at the lowest level with *Permute*, and end at the highest level with *Cyclist*, because each function call all lower-level functions.

### 1. Level 3 Function Calls

#### *a. UP*

Up calls permute, change the phase to "UP," and updates the value of the *State* with the post-permute value. Setting the phase to "UP" prevents a subsequent Up call until a *Down* function processes. Up accepts |Yi| and the Up color byte  $C_U$  as inputs, where |Yi| is

the size of the desired return value in bytes. In practice this is a parameter based on the function call.

$C_U$  is not applied to the *State* in hash mode, but it is applied to the least significant byte of the *State* in keyed mode. The returned value from Up is the most significant |Yi| bytes of the state, after the permute. Figure 6 gives the formal definition for Up.

Internal interface:  $Y_i \leftarrow \text{UP}(|Y_i|, c_U)$ (PHASE, s)  $\leftarrow$  (up,  $f(s \text{ if MODE} = \text{hash else } s \oplus (`00`* || c_U)))$ return  $s[0] || s[1] || \dots || s[|Y_i| - 1]$

## b. DOWN

The *Down* function performs post-permute processing. At a high level, the *Down* function creates a vector, then XORs that vector with the *State*. The output of this XOR is the new *State*.

The entire post-permute processing has four parts concatenated together in a specific order. In Xoodyak, this concatenated vector is 384 bits long and articulates which bits to flip in the *State*. The first is the input data,  $X_i$ , is of variable length and can be zero. The second is 0x01. The third is an extended 0x00 which spans the distance from the end of the second part to the final byte. The last part is a *Down* color byte (*C*<sub>D</sub>), which also contains a logical AND with 0x01 in hash mode.<sup>7</sup> *C*<sub>D</sub> varies depending on the function call. Figure 7 describes this process in formal terms, where both the phase and state (s) are assigned.

Figure 6. Up Function Definition. Source: [5].

<sup>&</sup>lt;sup>7</sup> Contextually, the impact of the logical AND 0x01 in <u>hash mode only</u> means that  $C_D$  is zero for all hash mode functions, except for the first pass through a call to *Absorb*. Recall that the only valid functions in hash mode are *Cyclist*, *Absorb*, and *Squeeze*.

Internal interface: DOWN $(X_i, c_D)$ (PHASE, s)  $\leftarrow$  (down,  $s \oplus (X_i \parallel `01' \parallel `00'^* \parallel c_D \& `01' \text{ if } \text{MODE} = \text{hash else } c_D)$ )

Figure 7. Down Function Definition. Source: [5].

## c. SPLIT

The *Split* function breaks the input string X into n sized pieces. Argument n is the maximum length that can be operated on at a single time and is variable depending on the function called. An n-sized piece of the string is processed for every sequential alteration through *Down* and *Up* until the entire input string X is exhausted.

## 2. Level 2 Function Calls

The level 2 functions are called by the level 1 functions. Level 2 function calls perform a modification of the *State*, then permute the *State* through *Up*, then perform another modification of the state through *Down*. The process is repeated depending on the input strings. The difference between the level 2 functions is the nature of the arguments supplied to the modifications in pre- or post-permute processing, and the length of the parameters supplied to those modifications.

## a. AbsorbAny

AbsorbAny adds an input string to the state. Like every level 2 function, arguments are supplied by the level 1 functions. Until the input string is exhausted, AbsorbAny will break the first input into |X/r| sized chunks through the Split function, then apply the Up (which includes the permute) and Down functions to the state for every chunk. If the phase is "UP" at the start of the function call, the Up function is not called and the function proceeds directly to Down.

The  $C_D$  is zero for every run through the Up and Down function beyond the first one. Regardless of input string size, *AbsorbAny* always terminates with the state in the "DOWN" phase. Figure 8 gives the formal definition for *AbsorbAny*. Internal interface: ABSORBANY $(X, r, c_D)$ for all blocks  $X_i$  in SPLIT(X, r) do if PHASE  $\neq$  up then UP(0, '00')DOWN $(X_i, c_D$  if first block else '00')

Figure 8. AbsorbAny Function Definition. Source: [5].

## b. Crypt

*Crypt* performs either the encrypt or decrypt operation. The calling level 1 function supplies text *I* and a Boolean value indicating whether the text is to be enciphered into the *State* (0 for encrypt), or whether the text is ciphertext to replace in the *State* (1 for decrypt).

The text is broken into  $(I/|R_{kout}|)$  chunks, rounded up, through *Split* as described before. Then for each chunk, *Up* is performed on the state.

For *Encrypt* operations, the argument supplied to the *Down* function is the input text, parted into chunks. For *Decrypt* operations, the input to the *Down* function is input text XORed with the most significant  $|R_{kout}|$  bytes of the *State*. Behaviorally, this means that the first  $|R_{kout}|$  bytes of the state are replaced with the input chunk in *Decrypt* operations. Figure 9 gives the formal definition for *Crypt*.

```

Internal interface: O \leftarrow \text{CRYPT}(I, \text{DECRYPT})

for all blocks I_i in \text{SPLIT}(I, R_{\text{kout}}) do

O_i \leftarrow I_i \oplus \text{UP}(|I_i|, `80` (\text{crypt}) \text{ if first block else `00`})

P_i \leftarrow O_i if \text{DECRYPT} else I_i

\text{DOWN}(P_i, `00`)

return ||_i O_i

```

Figure 9. Crypt Function Definition. Source: [5].

## c. Squeeze

Squeeze produces an *l*-byte hash of the state. Like all level 2 functions, the supplied arguments are defined by the level 1 functions. The first Up call permutes the *State*, and the most significant  $|R_{squeeze}|$  bytes are held as the hash output. If *l* is smaller than  $R_{squeeze}$  then *L* is used instead.

If the size of the hash is less than the desired value *l*, the *Down* function applies, which as defined in *Squeeze* only flips the eighth most significant bit in the state due to the specific arguments supplied.

The Up function is then called again, and once more the first  $|R_{squeeze}|$  bytes are appended to the hash. The cycle of *Down* followed by Up continues until the desired hash length is obtained.

In every case the phase ends with "UP" when *Squeeze* is called. Figure 10 gives the formal definition for *SqueezeAny*.

Internal interface:  $Y \leftarrow \text{SQUEEZEANY}(\ell, c_U)$   $Y \leftarrow \text{UP}(\min(\ell, R_{\text{squeeze}}), c_U)$ while  $|Y| < \ell$  do  $\text{DOWN}(\epsilon, `00`)$   $Y \leftarrow Y \mid \mid \text{UP}(\min(\ell - |Y|, R_{\text{squeeze}}), `00`)$ return Y

Figure 10. SqueezeAny Function Definition. Source: [5].

## 3. Level 1 Function Calls

Level 1 function calls supply arguments to and invoke the level 2 function calls. As such, their descriptions are curt.

## a. AbsorbKey

*AbsorbKey* is called to bring the secret key into the state. *AbsorbKey* can only be called as part of the initial state instantiation. *AbsorbKey* initializes the state in keyed mode, and applies the defined parameters, R<sub>kin</sub> and R<sub>kout</sub>, to R<sub>absorb</sub> and R<sub>squeeze</sub> (the *Absorb* and *Squeeze* rate every permutation).

The items are supplied to *AbsorbAny* as a single argument. They take the form ( $K \parallel id \parallel enc8(|id|)$ ), where K is the key,  $\parallel$  is the concatenation operator, and enc8(|id|) is the

modulo 256 value of the size of the optional identifier, id. Xoodyak default parameters presume id to be null.

The second argument is  $R_{absorb}$  is always 16 bytes or Xoodyak AEAD, and 0x02 is the color byte for *AbsorbKey*. The counter field is used as another way to absorb a nonce as described in [5]. Figure 11 gives the formal definition for *AbsorbKey*.

Internal interface: ABSORBKEY(K, id, counter), with |K|| id $| \le R_{kin} - 1$ (MODE,  $R_{absorb}$ ,  $R_{squeeze}$ )  $\leftarrow$  (keyed,  $R_{kin}$ ,  $R_{kout}$ ) ABSORBANY(K || id || enc<sub>8</sub>(|id|),  $R_{absorb}$ , '02' (key)) if counter not empty then ABSORBANY(counter, 1, '00')

Figure 11. AbsorbKey Function Definition. Source: [5].

#### b. Absorb

Absorb is the level 1 function the user invokes to absorb a string X into the state. Its only function is to immediately call the level 2 function AbsorbAny, where the arguments are the input string X, the parameter  $R_{absorb}$  as defined in the Cyclist call to AbsorbKey, and '03' for the color byte. Figure 12 gives the formal definition for Absorb.

```

Interface: ABSORB(X)

ABSORBANY(X, R_{absorb}, '03' (absorb))

```

Figure 12. Absorb Function Definition. Source: [5].

## c. Encrypt

The only argument for *Encrypt* is the text to be encrypted. *Encrypt* can only be called in keyed mode. It passes the text to *Crypt* as well as a Boolean 0 to indicate encryption vice decryption. Figure 13 gives the formal definition for *Encrypt*.

# Interface: $C \leftarrow \text{ENCRYPT}(P)$ , with MODE = keyed return CRYPT(P, false)

Figure 13. Encrypt Function Definition. Source: [5].

## d. Decrypt

The only argument for *Decrypt* is the text to be decrypted. It can only be called in keyed mode. It passes the text to *Crypt* as well as a Boolean 1 to indicate decryption vice decryption. Figure 14 gives the formal definition for *Decrypt*.

# Interface: $P \leftarrow \text{Decrypt}(C)$ , with MODE = keyed return Crypt(C, true)

Figure 14. Decrypt Function Definition. Source: [5].

#### e. Squeeze

The only argument in *Squeeze* is the desired hash length in bytes. It passes the hash length and the round constant 0x40 to *SqueezeAny*. Figure 15 gives the formal definition for *Squeeze*.

Interface:  $Y \leftarrow \text{SQUEEZE}(\ell)$ return  $\text{SQUEEZEANY}(\ell, '40' (\text{squeeze}))$

Figure 15. Squeeze Function Definition. Source: [5].

## f. SqueezeKey

The only argument in *SqueezeKey* is the desired hash length in bytes. It can only be called in keyed mode. It passes the hash length and the round constant 0x20 to *SqueezeAny* and exists to generate a key. Figure 16 gives the formal definition for *SqueezeKey*.

# Interface: $Y \leftarrow \text{SQUEEZEKEY}(\ell)$ , with MODE = keyed return $\text{SQUEEZEANY}(\ell, 20^{\circ} \text{ (key)})$

Figure 16. SqueezeKey Function Definition. Source: [5].

## g. Ratchet

*Ratchet* accepts no input. It can only be called in keyed mode. The first argument supplied to *AbsorbAny* is the first  $l_{ratchet}$  bytes of the permuted *State*. Behaviorally, the series of function calls permutes the state with f, then overwrites the  $l_{ratchet}$  most significant bytes in the state with zero. Figure 17 gives the formal definition for *Ratchet*.

# Interface: RATCHET(), with MODE = keyed ABSORBANY(SQUEEZEANY( $\ell_{ratchet}$ , '10' (ratchet)), $R_{absorb}$ , '00')

Figure 17. Ratchet Function Definition. Source: [5].

## 4. Top Level Instance

The instance of Xoodyak is determined by a call to the *Cyclist* function. Initially, state is instanced to be all zeros, and the phase is instanced as up. The mode is set to hash, and  $R_{hash}$  is assigned to be the  $R_{absorb}$  and  $R_{squeeze}$  parameter. In keyed mode, these values are overwritten in the call to *AbsorbKey*, but if there is no supplied key then the state remains in hash mode. Figure 18 gives the *Cyclist* formal definition.

Algorithm 2 Definition of CYCLIST  $[f, R_{hash}, R_{kin}, R_{kout}, \ell_{ratchet}]$

**Instantiation:** cyclist  $\leftarrow$  CYCLIST $[f, R_{\text{hash}}, R_{\text{kin}}, R_{\text{kout}}, \ell_{\text{ratchet}}](K, \text{id}, \text{counter})$ Phase and state: (PHASE, s)  $\leftarrow$  (up, '00<sup>(b')</sup>) Mode and absorb rate: (MODE,  $R_{\text{absorb}}, R_{\text{squeeze}}) \leftarrow$  (hash,  $R_{\text{hash}}, R_{\text{hash}}$ ) **if** K not empty **then** ABSORBKEY(K, id, counter)

Figure 18. Cyclist Function Instantiation. Source: [5].

## E. IMPLEMENTATION

This research implemented the ability to invoke every function call with the opcodes described in the level 1 functions. Function calls are made by supplying an operational code (opcode) to the input ports with the accompanying data. All opcodes are four bits long and expressed in hexadecimal. For example, the hardware will enter the Cyclist function in keyed mode by ingesting opcode 0x01, and *Cyclist* in hash mode by ingesting opcode 0x09.

Broadly speaking, our hardware structure is built around the level 2 functions, the inputs for which are modified depending on the exact function called. Every function except for *Split* is allocated hardware, which is administered by the user. The hardware structure is not able to recognize where one string of information begins or ends, and it is only capable of processing a finite amount of data on every function call. Since this split in data must occur regardless of how long or short a string is, the user is responsible for keeping track of when strings begin or end.<sup>8</sup>

## 1. Instance Parameters

The Xoodyak Implementation operates as a series of function calls. The Xoodyak algorithm allows for some variable length fields, such as the message text. This implementation used fixed length vector lengths based on parameters described in [5] and summarized in Table 6.

<sup>&</sup>lt;sup>8</sup> However, no organization is required on the part of the user apart from properly aligning the data input vector and opcodes. Subsequent calls for the same function {Absorb(X), Absorb(Y)} can be discriminated by inserting a single idle opcode for one clock (on a clock that the hardware is accepting inputs). Without this step, the hardware will process the data as {Absorb(X || Y)}, which is <u>not</u> the same operation because of color bytes and ensuing avalanche effect in the *Permute* hardware.

| Object                     | Length (Bytes) | Length (bits) |

|----------------------------|----------------|---------------|

| R <sub>absorb</sub> (hash) | 16             | 128           |

| R <sub>absorb</sub> (AEAD) | 44             | 352           |

| M <sub>length</sub>        | 24             | 192           |

| Key Size                   | 16             | 128           |

| Nonce                      | 16             | 128           |

| R <sub>sqz</sub>           | 16             | 128           |

Table 6.

Xoodyak Parameter Length Summary. Adapted from [5]

## 2. *State* Machines

Operations are governed through three distinct finite state machines. The first state machine determines whether the state is in hash or keyed mode. The second machine handles function calls. The final state machine handles the "*Shadow State*" which stores the previous function call. The *Shadow State* is important for administering color bytes. The state machine and "shadow state machine" can proceed directly from one function call to another. Returning to the idle state will wipe the shadow state, allowing for an identical function with a broken string. Table 7 summarizes valid opcode combinations.

| Function Call   | Opcode     | Keyed Mode Only |

|-----------------|------------|-----------------|

| Cyclist (keyed) | 1          | -               |

| Cyclist (hash)  | 9          | -               |

| Nonce           | 2          | YES             |

| Absorb          | 3          | -               |

| Encrypt         | 4          | YES             |

| Decrypt         | 5          | YES             |

| Squeeze         | 6          | -               |

| Ratchet         | 7          | YES             |

| SqueezeKey      | 8          | YES             |

| Idle            | All Others | -               |

Table 7. Xoodyak Opcode Decode and Mode Restriction.

The "Nonce" function performs an Absorb with a different parameter length, per Table 6.

## **3.** User Operation of Xoodyak

Xoodyak completes functions in either one clock, four clocks, or 12 clocks depending on the hardware build and the function call. These distinctions are discussed in the next section. These counts do not include startup queuing delays.<sup>9</sup>

#### a. Startup Delays and Timing

There is an additional two-clock startup delay to sample and alter the state machine. Therefore, a function call completes three, six, or 14 clocks after a function call is queued at the front of the module.<sup>10</sup> This means that in all cases the next function will be sampled while the previous function is still running, unless the state machine is in the idle state.

Any function that uses the *Permute* module completes in four or 12 clocks. The four or 12 clocks required for operation depends on the build used.<sup>11</sup> Both approaches fully satisfy the round requirement levied by the Xoodyak algorithm.

Not every function call requires *Permute*, which triggers a one clock operation. Functions that end with an "UP" state as defined by [5] cause the next function called to not use *Permute*. Multiple calls to the same function do not trigger this case. For example, generating a 256-bit digest requires two sequential calls to *Squeeze*. Each call requires *Permute*, and two calls are required, for a total of ten clocks to generate the entire string.<sup>12</sup> A following function such as *Absorb* (or other) will not require *Permute* as such the next input text and opcode will be sampled on the very next clock. Tables 8, 9, and 10 summarize stream clock delays based on function calls.

<sup>&</sup>lt;sup>9</sup> All modules support streaming operations. Accordingly, startup delays are not included in any clock related description outside Ch III.E.3.a, Startup Delays, unless explicitly stated otherwise. CH IV.C.3 refers.

<sup>&</sup>lt;sup>10</sup> Alternatively, two, five, or 13 clocks <u>after</u> the sampling register. That is, if the sampling clock is not counted in the total. If applicable, output texts are provided synchronously on this clock, which is two, five, or 13 clocks after the sampling.

<sup>&</sup>lt;sup>11</sup> Ch III.E.4.b describes how these build differences impact the required clocks. Appendix E contains the full list of builds. Tables 13–16 contain selected builds with both build versions.

<sup>&</sup>lt;sup>12</sup> For the four-clock build: a two-clock startup delay, followed by four clocks of operation for the first call. The subsequent call to Squeeze only requires four clocks through streaming operations, having been sampled on clock 5 while the first Squeeze was operating. Clock 10 generates the last set of output text.

| Function Call   | Opcode |

|-----------------|--------|

| Cyclist (keyed) | 1      |

| Cyclist (hash)  | 9      |

Table 8.Functions with 1-Clock Stream Delays.

| Table 9. | Functions That Make the Next Non-Identical Function Have a 1- |

|----------|---------------------------------------------------------------|

|          | Clock Stream Delay.                                           |

| Function Call  | Opcode |

|----------------|--------|

| Cyclist (hash) | 9      |

| Squeeze        | 6      |

| SqueezeKey     | 8      |

Table 10. Functions with a 4-Clock or 12-clock Stream Delay by Default

| Function Call | Opcode |

|---------------|--------|

| Nonce         | 2      |

| Absorb        | 3      |

| Encrypt       | 4      |

| Decrypt       | 5      |

| Squeeze       | 6      |

| Ratchet       | 7      |

| SqueezeKey    | 8      |

## 4. Structural Datapath

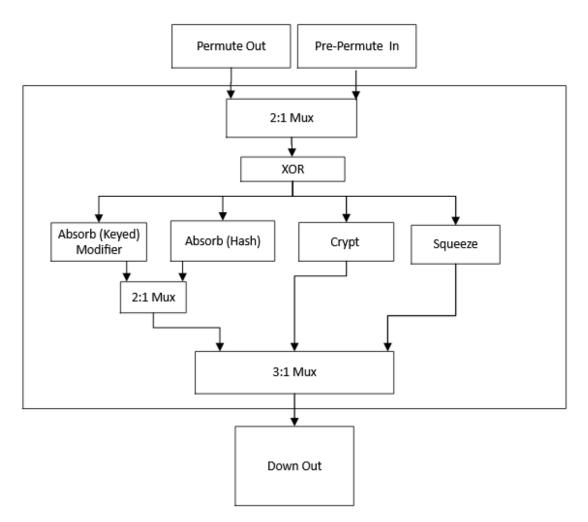

There are three parts to the datapath, Pre-Permute, Permute, and Post-Permute. Each section loosely relates to different stages in the level 2 functions. Hardware in the Pre-Permute module performs exception handling. Pre-Permute, Permute, and Post-Permute collectively perform all functions. The user performs *Split* on the data, but the hardware will track whether a function call is continuous. The user can indicate a string for a function by continuously asserting the same opcode when the hardware completes function calls. This allows the user to handle arbitrary length function calls, provided those lengths are multiples of the parameters specified. The user can provide padding to meet those multiples.

## a. Pre-Permute

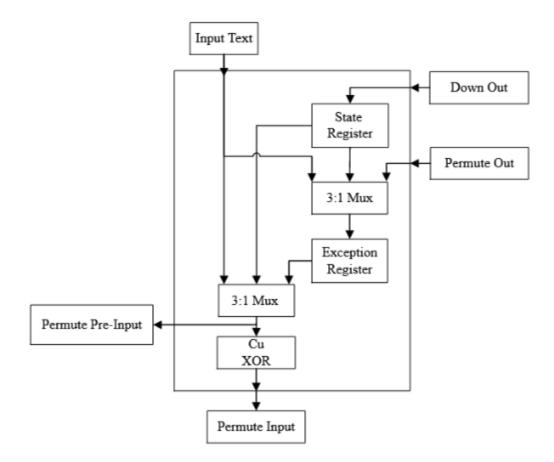

The purpose of the Pre-*Permute* stage is to generate the 384-bit vector that enters the *Permute* module. Figure 19 provides a high-level process overview of the hardware structure that handles the per *Permute* stage. By default, the *State* is the contents of a 384bit vector which is the output of the previous function call. There are several exceptions, and the Pre-*Permute* stage handles all of them in a multiplexer. The exceptions are summarized in the next section. Multiple exceptions cannot occur at the same time, so dedicated exception handling hardware is reused in several cases.

A round constant is then applied to the output, depending on the function call, as described in Algorithm 2 [5]. The round constant is only added for the first permutation of a string.

Figure 19. Pre-Permute Process Diagram

## b. Exception handling

There are two exceptions to handle edge cases. The cause of the edge cases is that the hardware does not track the algorithmic phase - "UP" or "DOWN." Rather, each pass through the hardware accomplishes both the Up and Down functions, which creates issues when one of those functions is not used. There are two ways this can occur. The first way is after a Squeeze function. Recalling Figure 16, see that regardless of the string length l, the phase ends in the "UP" state at the completion of the function call. Since the user is performing the *Split* function, the user delimits the end of the *Squeeze* function by simply providing the next function and associated data. Inside the hardware, the *Shadow State* is shadow squeeze, and the actual state machine is not in the Squeeze state, which triggers the exception. The impact is that the next function call, delimited by the next ingested opcode other than 4'h6 (Squeeze) or 4'h8 (SqueezeKey), will not perform the Up function and associated *Permute*. Additionally, the value held in the *State* register will be invalid, and the value in the exception register will be used instead. We speculate this exception will not be especially relevant, since performing a Squeeze or SqueezeKey is a hash of the existing State, which implies the operation is complete. However, it is included for completeness of operation.

The second exception is in the first *Absorb* function call after *State* instantiation with opcode 4'h9, *Cyclist* (hash). Unlike the hardware keyed mode *Cyclist* function, which also performs the algorithmic *AbsorbKey* function, the hardware hash *Cyclist* function merely only creates a 384-bit vector of all zeros. Accordingly, the first *Absorb* after this only requires an algorithmic *Down* function and is completed in a single clock.<sup>13</sup>

<sup>&</sup>lt;sup>13</sup> We considered including the first hash-based *Absorb* in the *Cyclist* instantiation, requiring the user to supply the first round of *Absorb* data at instantiation. This would theoretically cause a one clock advancement of any function sequence, but we decided against it because this would be combining two different top-level functions at once, which is not consistent with the proposed standard [5]. This is directly in opposition to the associated key absorption innate in the keyed *Cyclist* function, which directly calls the first *Absorb* without further top level involvement and therefore does not trigger an exception under our rules.

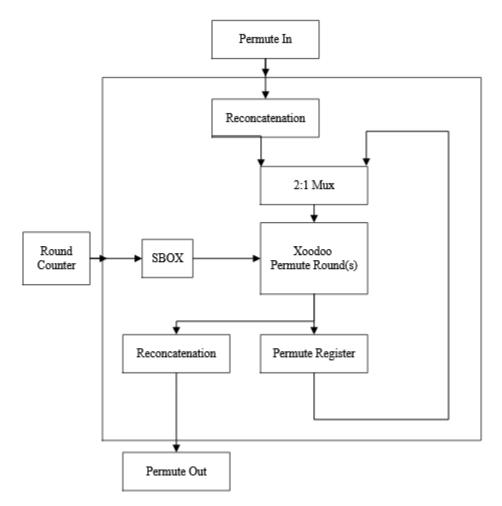

#### c. Permute

The *Permute* module is made up of three parts, a round, round constant vector, and a register. The *Permute* inputs are fed to the *Permute* module and registered every clock. Figure 20 provides a high-level view of this process. Multiple *Permute* rounds can be instanced in sequence. This research specifically built one-*Permute* instances and three-*Permute* instances.<sup>14</sup> 12 rounds must be accomplished in total, and the addition of multiple *Permute* instances reduces the number of clocks required to complete a permutation.

Figure 20. Permute Process Diagram

<sup>&</sup>lt;sup>14</sup> See CH IV for build analysis. See Appendix E for full list of builds.