**Calhoun: The NPS Institutional Archive**

**DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2022-09

# MEDIUM VOLTAGE DC SOLID STATE CIRCUIT BREAKER BENCH TEST

Brandt, Jonathan J.

Monterey, CA; Naval Postgraduate School

https://hdl.handle.net/10945/71047

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

### NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

### **THESIS**

### MEDIUM VOLTAGE DC SOLID STATE CIRCUIT BREAKER BENCH TEST

by

Jonathan J. Brandt

September 2022

Thesis Advisor:

Co-Advisor:

Di Zhang

Yuntao Xu

Approved for public release. Distribution is unlimited.

#### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington, DC, 20503.

| 1. AGENCY USE ONLY (Leave blank)                                               | 2. REPORT DATE September 2022 | 3. REPORT TY | YPE AND DATES COVERED Master's thesis                  |

|--------------------------------------------------------------------------------|-------------------------------|--------------|--------------------------------------------------------|

| 4. TITLE AND SUBTITLE MEDIUM VOLTAGE DC SOLII                                  | O STATE CIRCUIT BREAKER       | R BENCH TEST | 5. FUNDING NUMBERS                                     |

| <b>6. AUTHOR(S)</b> Jonathan J. Bran                                           | dt                            |              |                                                        |

| 7. PERFORMING ORGANIZA<br>Naval Postgraduate School<br>Monterey, CA 93943-5000 | TION NAME(S) AND ADDR         | ESS(ES)      | 8. PERFORMING<br>ORGANIZATION REPORT<br>NUMBER         |

| 9. SPONSORING / MONITOR<br>ADDRESS(ES)<br>N/A                                  | ING AGENCY NAME(S) ANI        | D            | 10. SPONSORING /<br>MONITORING AGENCY<br>REPORT NUMBER |

| 11. SUPPLEMENTARY NOTE official policy or position of the D                    |                               |              | he author and do not reflect the                       |

| <b>12a. DISTRIBUTION / AVAIL</b> Approved for public release. Dist             |                               |              | 12b. DISTRIBUTION CODE<br>A                            |

#### 13. ABSTRACT (maximum 200 words)

Next generation fleets will rely on medium-voltage direct-current (MVDC) electric power distribution systems utilizing high power density and high efficiency components. One key gap to make such MVDC systems feasible is a super-fast, high efficiency, and high-power density protection device. The U.S. Navy has previously developed a 1 kV, 1 kA solid state circuit breaker (SSCB). A new 2 kV, 1.2 kA SSCB has been designed by NPS with collaborating partners that has quadrupled power density. This innovative insulated gate bipolar transistor (IGBT)-based SSCB consists of anti-series IGBT modules, a parallel resistor-capacitor (RC) branch, and an electronically triggered metal-oxide varistor (MOV) branch. The novel electronically controlled MOV is comprised of a MOV in series with a silicon controlled rectifier (SCR) passively triggered during the IGBT turn-off process, improving the trade-off between the leakage current and clamping voltage. The use of a lower IGBT gate voltage allows the elimination of current limiting inductors, increasing the SSCB power density. This thesis focuses on the switching and thermal tests necessary to validate the implemented concepts, and the data will be used for down-selecting technical directions, improving the SSCB performance. The results show that the SSCB is sufficient to interrupt most faults while containing peak current and voltage within design parameters and the efficiency target can be met with comfortable thermal margins.

| 14. SUBJECT TERMS                                  | 15. NUMBER OF                                         |                                                      |                               |

|----------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|-------------------------------|

| medium-voltage direct-currer                       | PAGES                                                 |                                                      |                               |

| bipolar transistor, IGBT, meta                     | 135                                                   |                                                      |                               |

| controlled rectifier, SCR                          | 16. PRICE CODE                                        |                                                      |                               |

| 17. SECURITY CLASSIFICATION OF REPORT Unclassified | 18. SECURITY CLASSIFICATION OF THIS PAGE Unclassified | 19. SECURITY CLASSIFICATION OF ABSTRACT Unclassified | 20. LIMITATION OF<br>ABSTRACT |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18 THIS PAGE INTENTIONALLY LEFT BLANK

#### Approved for public release. Distribution is unlimited.

#### MEDIUM VOLTAGE DC SOLID STATE CIRCUIT BREAKER BENCH TEST

Jonathan J. Brandt Lieutenant, United States Navy BS, Citadel, Military College of South Carolina, 2016

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

### NAVAL POSTGRADUATE SCHOOL September 2022

Approved by: Di Zhang Advisor

> Yuntao Xu Co-Advisor

Douglas J. Fouts Chair, Department of Electrical and Computer Engineering THIS PAGE INTENTIONALLY LEFT BLANK

#### **ABSTRACT**

Next generation fleets will rely on medium-voltage direct-current (MVDC) electric power distribution systems utilizing high power density and high-efficiency components. One key gap to make such MVDC systems feasible is a super-fast, high-efficiency, and high power density protection device. The U.S. Navy has previously developed a 1 kV, 1 kA solid state circuit breaker (SSCB). A new 2 kV, 1.2 kA SSCB has been designed by NPS with collaborating partners that has quadrupled power density. This innovative insulated gate bipolar transistor (IGBT)-based SSCB consists of anti-series IGBT modules, a parallel resistor-capacitor (RC) branch, and an electronically triggered metal-oxide varistor (MOV) branch. The novel electronically controlled MOV is comprised of a MOV in series with a siliconcontrolled rectifier (SCR) passively triggered during the IGBT turn-off process, improving the trade-off between the leakage current and clamping voltage. The use of a lower IGBT gate voltage allows the elimination of current limiting inductors, increasing the SSCB power density. This thesis focuses on the switching and thermal tests necessary to validate the implemented concepts, and the data will be used for down-selecting technical directions, improving the SSCB performance. The results show that the SSCB is sufficient to interrupt most faults while containing peak current and voltage within design parameters and the efficiency target can be met with comfortable thermal margins.

THIS PAGE INTENTIONALLY LEFT BLANK

### Table of Contents

| 1 I   | ntroduction                                 |    |     |    |   |   |   |   |   |   |   |   |   | 1  |

|-------|---------------------------------------------|----|-----|----|---|---|---|---|---|---|---|---|---|----|

| 1.1   | Significance of Research                    |    |     |    |   |   |   |   |   |   |   |   |   | 1  |

| 1.2   | Research Method                             |    |     |    |   |   |   |   |   |   |   |   |   | 3  |

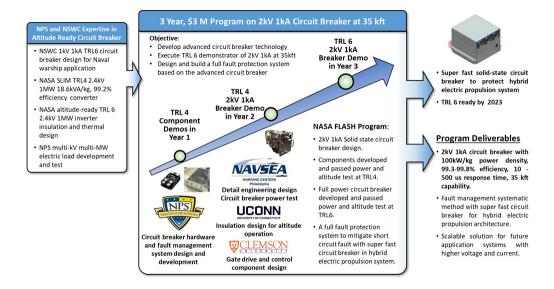

| 1.3   | NASA FLASH Introduction                     |    |     |    |   |   |   |   |   |   |   |   |   | 3  |

| 1.4   | Chapter Overview                            |    |     |    |   |   | • | • | • | • | • |   | • | 5  |

| 2 B   | ackground                                   |    |     |    |   |   |   |   |   |   |   |   |   | 7  |

| 2.1   | Solid State Circuit Breaker Fundamentals.   |    |     |    |   |   |   |   |   |   |   |   |   | 7  |

| 2.2   | SSCB Design Considerations                  |    |     |    |   |   |   |   |   |   |   |   |   | 9  |

| 2.2.1 | Solid State Circuit Breaker Functionality . |    |     |    |   |   |   |   |   |   |   |   |   | 12 |

| 2.3   | SSCB Hardware Design Improvements           | •  |     |    |   |   | • | • | • |   |   |   | • | 19 |

| 3 S   | witching Performance Test                   |    |     |    |   |   |   |   |   |   |   |   |   | 25 |

| 3.1   | Test Setup                                  |    |     |    |   |   |   |   |   |   |   |   |   | 25 |

| 3.1.1 | Hardware Selection                          |    |     |    |   |   |   |   |   |   |   |   |   | 26 |

| 3.1.2 | Instrumentation Selection                   |    |     |    |   |   |   |   |   |   |   |   |   | 27 |

| 3.1.3 | Switching Test Layout                       |    |     |    |   |   |   |   |   |   |   |   |   | 29 |

| 3.2   | Switching Performance Test                  |    |     |    |   |   |   |   |   |   |   |   |   | 30 |

| 3.2.1 | Benchmark Switching Performance Test .      |    |     |    |   |   |   |   |   |   |   |   |   | 31 |

| 3.2.2 | Reduced Gate Voltage Switching Performan    | ce | Tes | t. |   |   |   |   |   |   |   | • |   | 35 |

|       | Bus Bar Connection Configurations           |    |     |    |   |   |   |   |   |   |   |   |   | 49 |

|       | Desaturation Tuning                         |    |     |    |   |   |   |   |   |   |   |   |   | 58 |

| 3.2.5 | High Temperature Switching Test             |    |     |    |   |   |   |   |   |   |   |   |   | 65 |

| 3.2.6 | MOV Performance Improvements                | •  |     |    | • | • | • |   | • | • | • | • | • | 77 |

| 4 T   | hermal Performance Test                     |    |     |    |   |   |   |   |   |   |   |   |   | 83 |

| 4.1   | Test Setup                                  |    |     |    |   |   |   |   |   |   |   |   |   | 83 |

| 4.1.1 | Hardware Selection                          |    |     |    |   |   |   |   |   |   |   |   |   | 84 |

| 4.1.2 | Instrumentation Selection                   |    |     |    |   |   |   |   |   |   |   |   |   | 91 |

|       | Thermal Test Layout                         |    |     |    |   |   |   |   |   |   |   |   |   | 93 |

| Initia | al Distribution List                         |   |   |   |   |       |   |   |   |   |   |   | 11: |

|--------|----------------------------------------------|---|---|---|---|-------|---|---|---|---|---|---|-----|

| List o | of References                                |   |   |   |   |       |   |   |   |   |   |   | 11  |

| 5.2    | Future Work                                  |   |   | • | • | •     | • | ٠ | • | • | • | • | 10  |

| 5.1.2  | Thermal Performance Evaluation               |   |   |   | • | <br>• | • | • | • | • |   |   | 10  |

| 5.1.1  | Switching Performance Characterization .     |   |   |   |   |       |   |   |   |   |   |   | 10  |

| 5.1    | Conclusions                                  |   |   |   |   |       |   |   |   |   |   |   | 10  |

| 5 C    | Conclusions and Future Work                  |   |   |   |   |       |   |   |   |   |   |   | 10  |

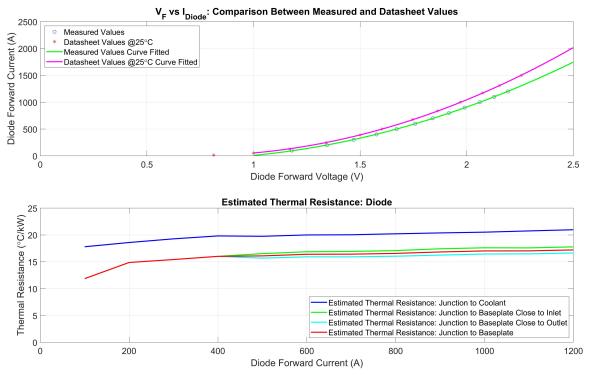

| 4.3    | Diode Thermal Test                           | • | • |   |   |       | • | ٠ | • | • | • |   | 10  |

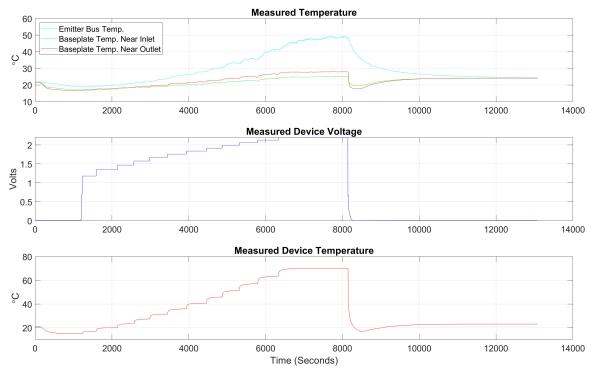

| 4.2.2  | $12\ V\ V_{GE}\ Operational\ Test . . . . .$ |   |   |   |   |       |   |   |   |   |   |   | 9   |

| 4.2.1  | $15~V~V_{GE}~Benchmark~Test~~.~~.~~.~~.$     |   |   |   |   |       |   |   |   |   |   |   | 9   |

| 4.2    | IGBT Thermal Test                            |   |   |   |   |       |   |   |   |   |   |   | 9   |

### List of Figures

| Figure 1.1 | Three Year Timeline for SSCB Development and Testing                                                                                                                                                              | 5  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1 | Generic "CEEC" SSCB Topology                                                                                                                                                                                      | 10 |

| Figure 2.2 | A Basic Fault on One Leg of the SSCB                                                                                                                                                                              | 11 |

| Figure 2.3 | Design Case Fault Where One SSCB is Removed From the System                                                                                                                                                       | 12 |

| Figure 2.4 | IGBT Operating Curves for Various Gate Voltages                                                                                                                                                                   | 13 |

| Figure 2.5 | I-V Curves for Diode and IGBT                                                                                                                                                                                     | 16 |

| Figure 2.6 | MOV Clamped SSCB Voltage During Nominal Operation                                                                                                                                                                 | 18 |

| Figure 2.7 | SSCB Design Without a Current Limiting Inductor                                                                                                                                                                   | 20 |

| Figure 2.8 | MOV Clamped SSCB Voltage with IGBT in Current Saturated Active Region Mode of Operation                                                                                                                           | 21 |

| Figure 2.9 | Electronic Triggered MOV Design                                                                                                                                                                                   | 22 |

| Figure 3.1 | Nominal Switching Test Configuration Including Hardware, Instrumentation, and Controls                                                                                                                            | 26 |

| Figure 3.2 | Nominal Switching Test Voltage and Current Measurement Locations                                                                                                                                                  | 28 |

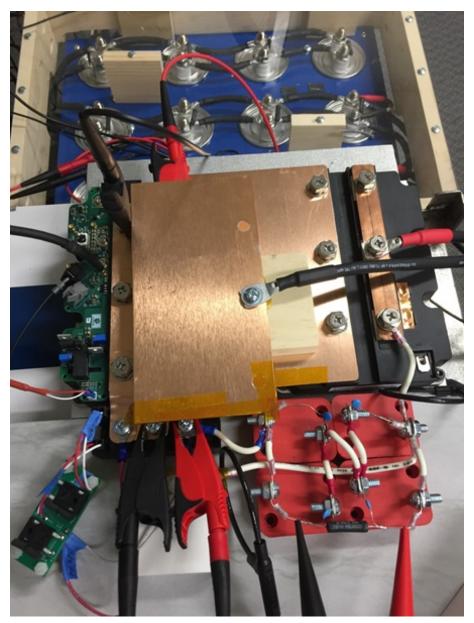

| Figure 3.3 | Hardware Assembled Testing Setup for Switching Performance Test                                                                                                                                                   | 30 |

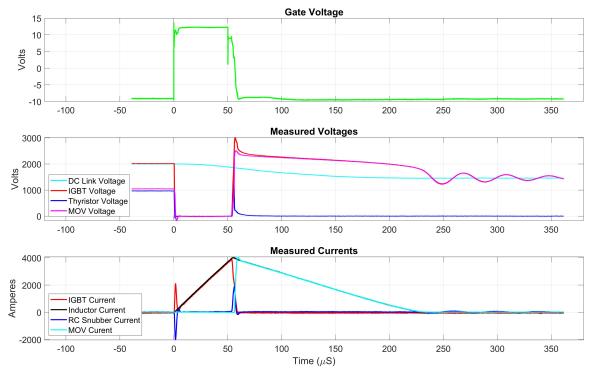

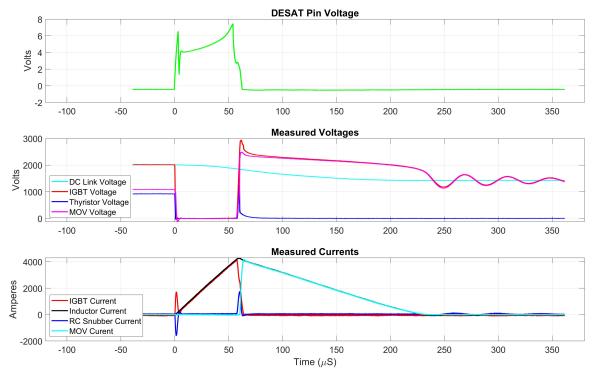

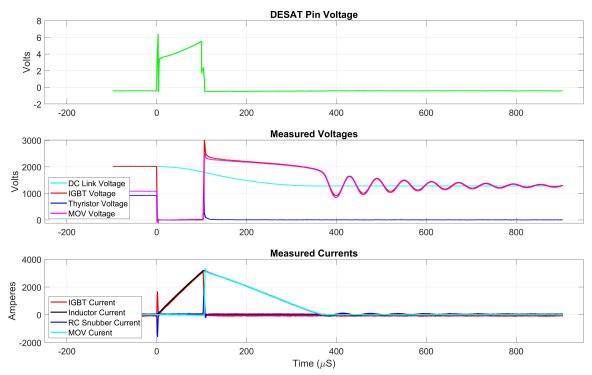

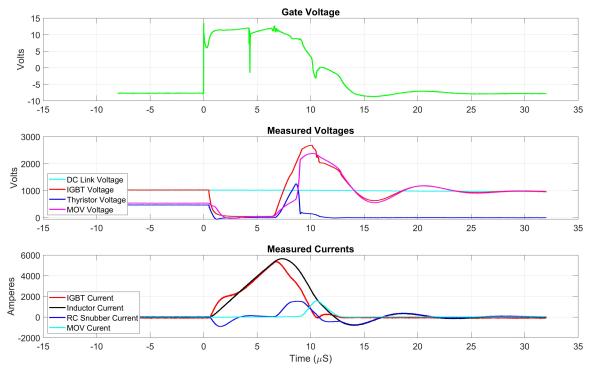

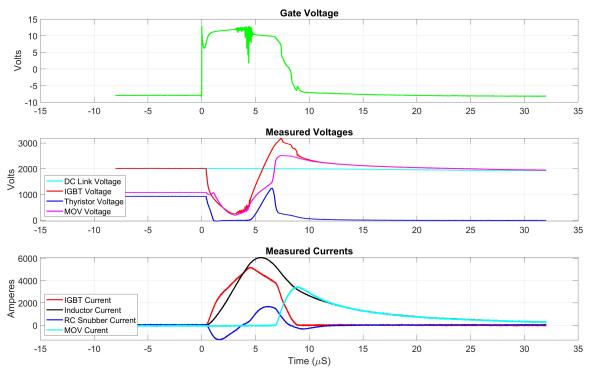

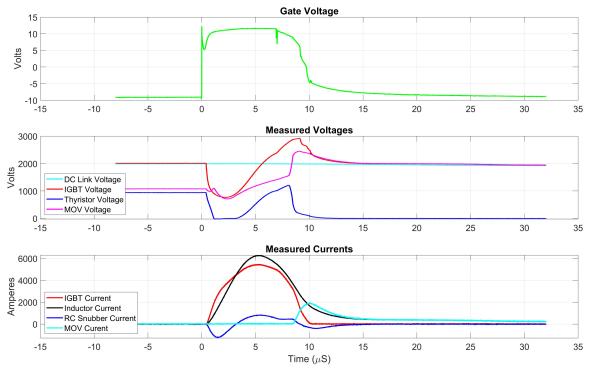

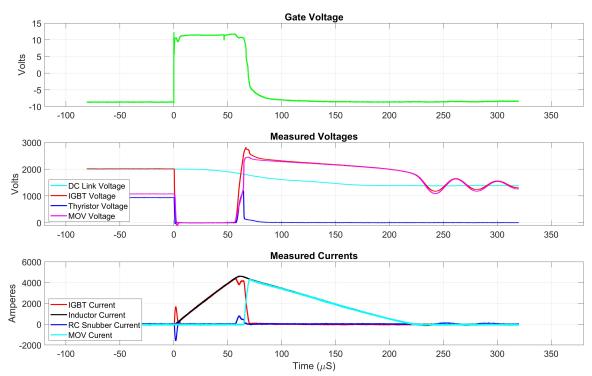

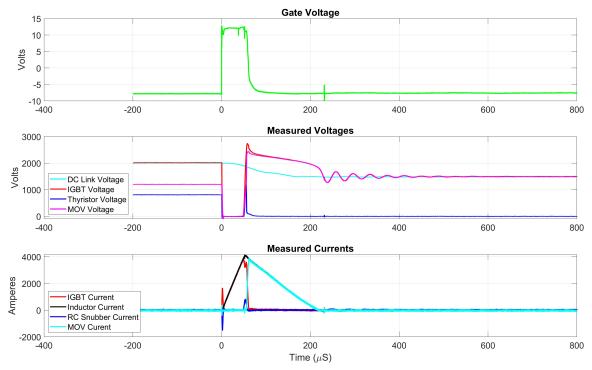

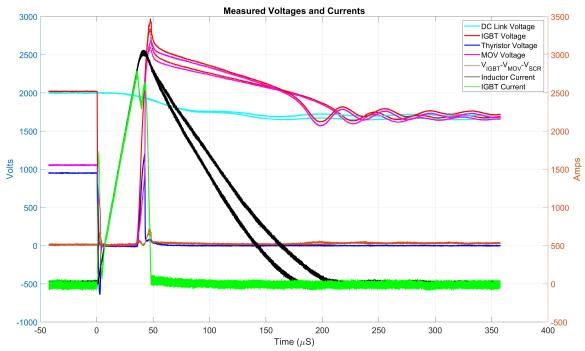

| Figure 3.4 | Benchmark Full Switch Test Transient Response, $V_{sys}$ =2000 V, $V_{GE}$ =15 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ $L_{sys}$ =25 $\mu$ H           | 33 |

| Figure 3.5 | Benchmark Full Switch Test Zoomed In Transient Response, $V_{sys}$ =2000 V, $V_{GE}$ =15 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ $L_{sys}$ =25 $\mu$ H | 34 |

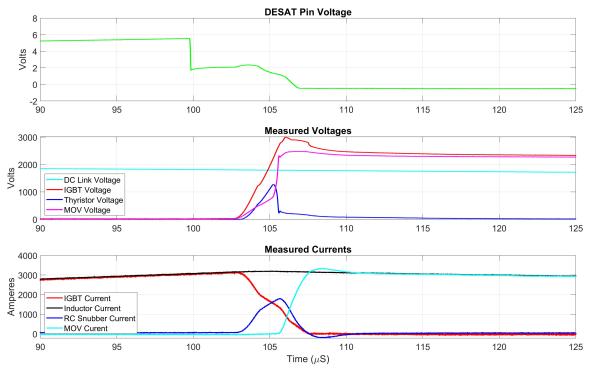

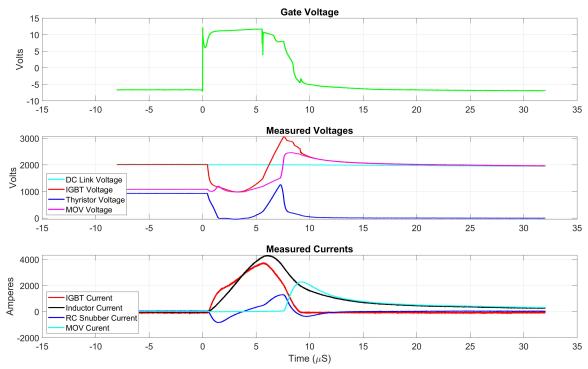

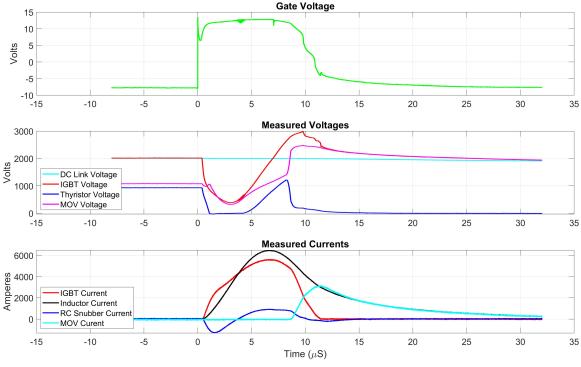

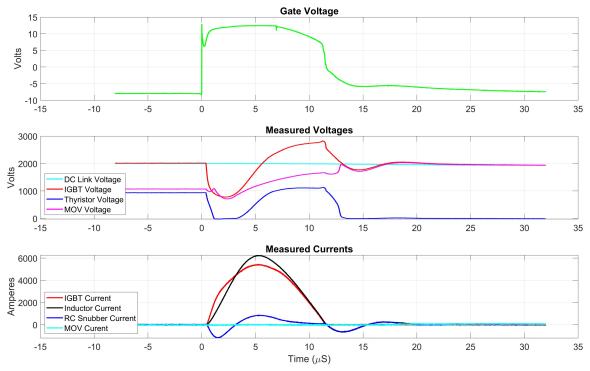

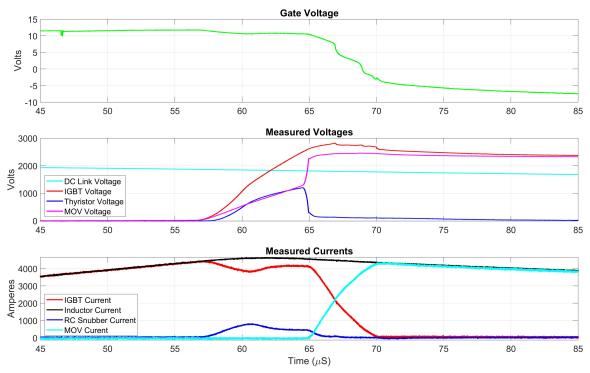

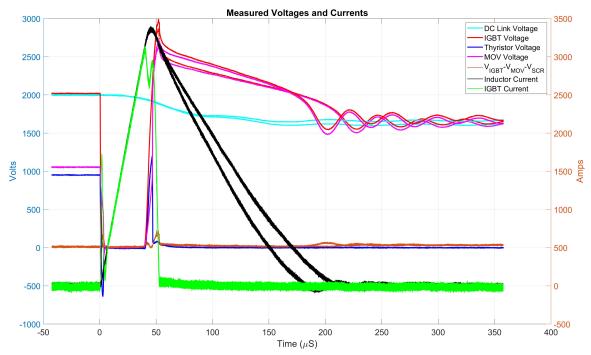

| Figure 3.6 | Full Switch Test Transient Response, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =25 $\mu$ H.                  | 37 |

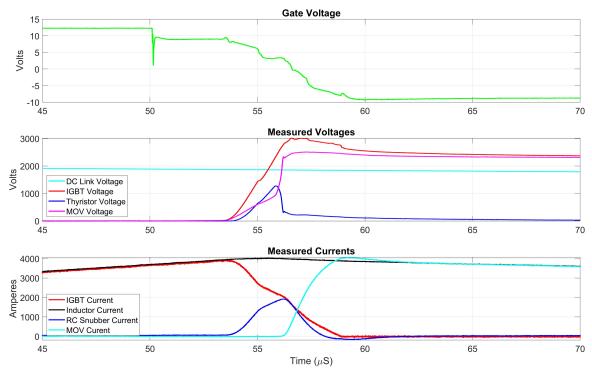

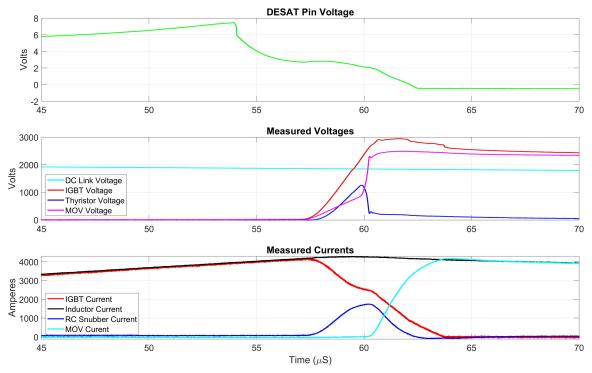

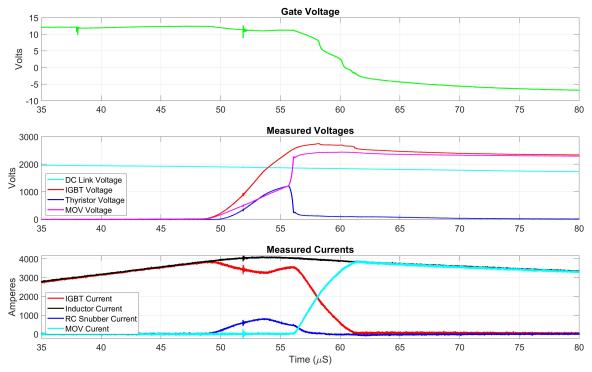

| Figure 3.7  | Full Switch Test Zoomed In Transient Response, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =25 $\mu$ H                                          | 38 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

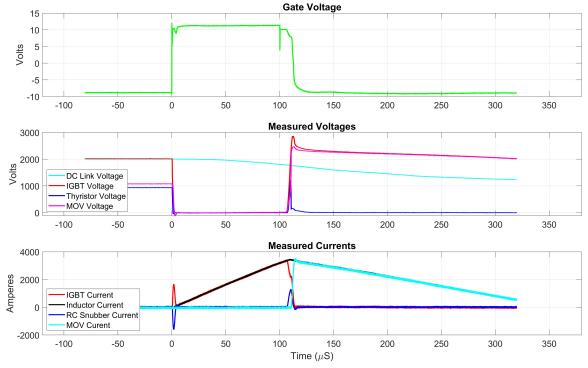

| Figure 3.8  | Full Switch Test Transient Response, V <sub>sys</sub> =2000 V, V <sub>GE</sub> =12 V, R <sub>on</sub> =0.3 $\Omega$ , C <sub>blanking</sub> =6800 pF, R <sub>STO</sub> =4 $\Omega$ , R <sub>off</sub> =4 $\Omega$ , L <sub>sys</sub> =50 $\mu$ H . | 39 |

| Figure 3.9  | Full Switch Test Zoomed In Transient Response, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =50 $\mu$ H                                          | 40 |

| Figure 3.10 | Full Switch Test Transient Response, $V_{sys}$ =1600 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =2 $\mu H$ .                                                   | 42 |

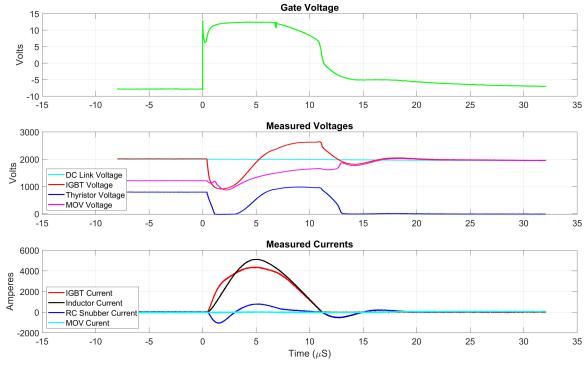

| Figure 3.11 | Full Switch Test Zoomed In Transient Response, $V_{sys}$ =1600 V, $V_{GE}$ =10 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =2 $\mu$ H                                           | 44 |

| Figure 3.12 | Full Switch Test Zoomed In Transient Response, $V_{sys}$ =1000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =1 $\mu$ H                                           | 46 |

| Figure 3.13 | Full Switch Test Zoomed In Transient Response, $V_{sys}$ =2000 V, $V_{GE}$ =10 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =1 $\mu$ H                                           | 48 |

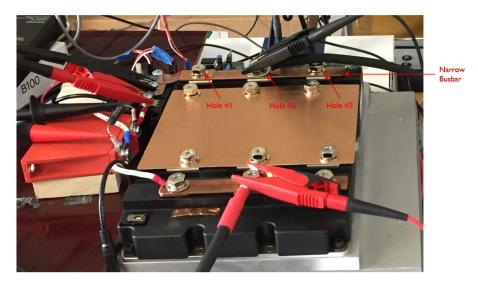

| Figure 3.14 | SSCB Configuration with Narrow Emitter Bus Bar                                                                                                                                                                                                     | 50 |

| Figure 3.15 | Narrow Bus Bar, "Hole #2" Zoomed In Transient Response, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ $L_{sys}$ =1 $\mu$ H                                    | 53 |

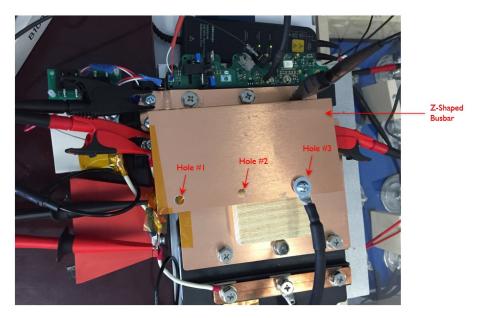

| Figure 3.16 | SSCB Configuration with Z-Shaped Emitter Bus Bar                                                                                                                                                                                                   | 54 |

| Figure 3.17 | Z-Shaped Bus Bar, "Hole #2" Zoomed In Transient Response, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =1 $\mu$ H                                | 57 |

| Figure 3.18 | "Hole #3," $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =10 Ω, $R_{off}$ =4 Ω, $L_{sys}$ =1 $\mu H$                                                                                                     | 60 |

| Figure 3.19 | "Hole #3," $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =10 Ω, $R_{off}$ =4 Ω, $L_{sys}$ =25 $\mu$ H                                                                                                    | 61 |

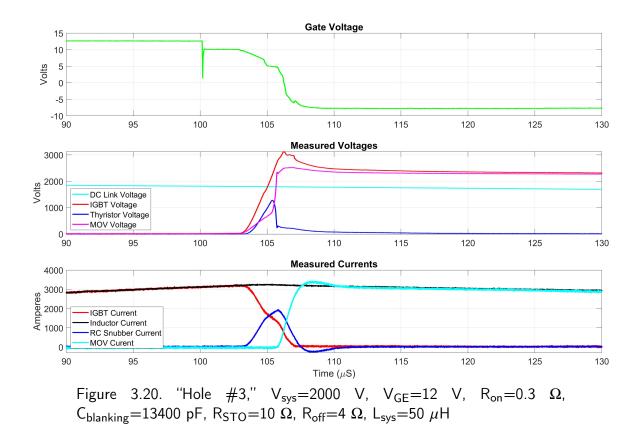

| Figure 3.20 | "Hole #3," $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =13400 pF, $R_{STO}$ =10 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =50 $\mu H$                                                                             | 62      |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 3.21 | Minimizing Total Inductance by Relocating Capacitor Bank, $L_{total}$ 0.65 $\mu H$                                                                                                                                                                  | 63      |

| Figure 3.22 | $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =10 Ω, $R_{off}$ =4 Ω, $L_{total}$ =0.65 $\mu$ H                                                                                                            | 65      |

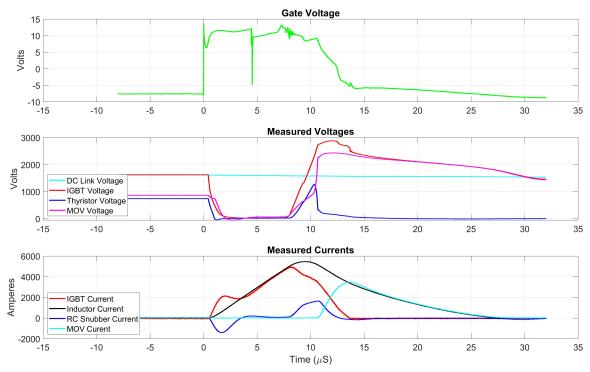

| Figure 3.23 | Room Temperature, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =1340 pF, $R_{STO}$ =22 $\Omega$ , $R_{off}$ =10 $\Omega$ , $L_{total}$ =0.65 $\mu$ H                                                                  | 0<br>67 |

| Figure 3.24 | Room Temperature, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =1340 pF, $R_{STO}$ =22 $\Omega$ , $R_{off}$ =10 $\Omega$ , $L_{sys}$ =25 $\mu$ H                                                                      | 0<br>68 |

| Figure 3.25 | Room Temperature Zoomed In Transient Response, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =13400 pF, $R_{STO}$ =22 $\Omega$ , $R_{off}$ =10 $\Omega$ , $L_{sys}$ =25 $\mu$ H                                        | 69      |

| Figure 3.26 | Room Temperature, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =1340 pF, $R_{STO}$ =22 $\Omega$ , $R_{off}$ =10 $\Omega$ , $L_{sys}$ =50 $\mu H$                                                                      | 0<br>71 |

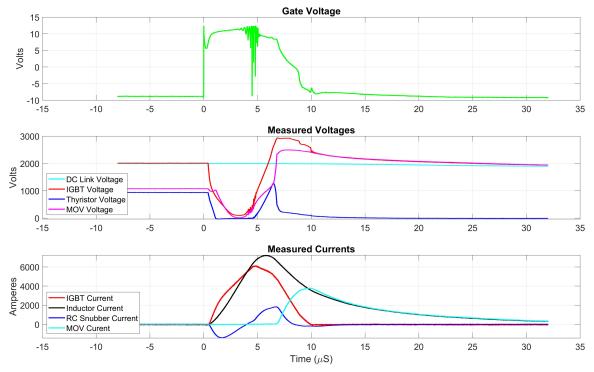

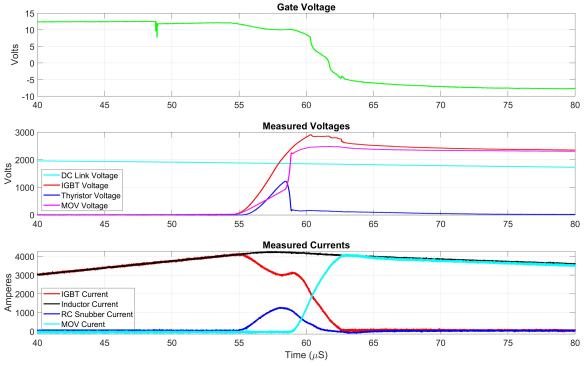

| Figure 3.27 | $T_{\rm j}$ 100 °C, $V_{\rm sys}$ =2000 V, $V_{\rm GE}$ =12 V, $R_{\rm on}$ =0.3 Ω, $C_{\rm blanking}$ =13400 pF, $R_{\rm STO}$ =22 Ω, $R_{\rm off}$ =10 Ω, $L_{\rm total}$ =0.65 $\mu H$                                                           | 72      |

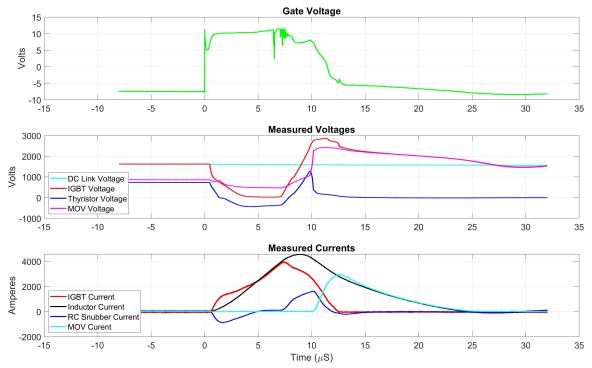

| Figure 3.28 | $T_j$ =100 °C, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =22 Ω, $R_{off}$ =10 Ω, $L_{sys}$ =25 $\mu$ H                                                                                                | 74      |

| Figure 3.29 | Zoomed In Transient Response, $T_j$ =100 °C, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =13400 pF, $R_{STO}$ =22 $\Omega$ , $R_{off}$ =10 $\Omega$ , $L_{sys}$ =25 $\mu$ H                                          | 75      |

| Figure 3.30 | $T_j$ =100 °C, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =22 Ω, $R_{off}$ =10 Ω, $L_{sys}$ =50 $\mu$ H                                                                                                | 76      |

| Figure 3.31 | Four MOVs in 2P2S Configuration                                                                                                                                                                                                                     | 78      |

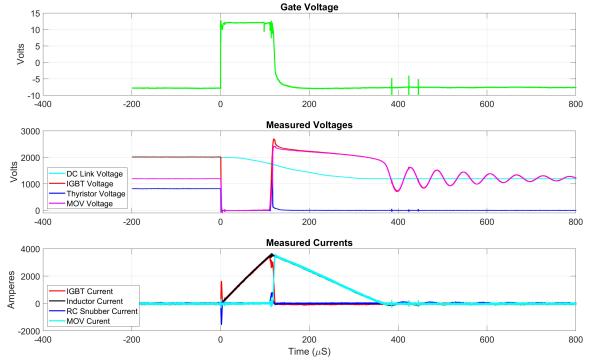

| Figure 3.32 | 2P2S Response, V <sub>sys</sub> =2000 V, V <sub>GE</sub> =12 V, R <sub>on</sub> =0.3 Ω, C <sub>blanking</sub> =13400 pF, R <sub>STO</sub> =22 Ω, R <sub>off</sub> =10 Ω, L <sub>sys</sub> =25 μH, C <sub>MOV</sub> =3300 pF, t <sub>on</sub> =20 μs | 80      |

| Figure 3.33 | 2P2S Response, $V_{sys}$ =2000 V, $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =22 Ω, $R_{off}$ =10 Ω, $L_{sys}$ =25 $\mu$ H, $C_{MOV}$ =3300 pF, $t_{on}$ =25 $\mu$ s                                                      | 81      |

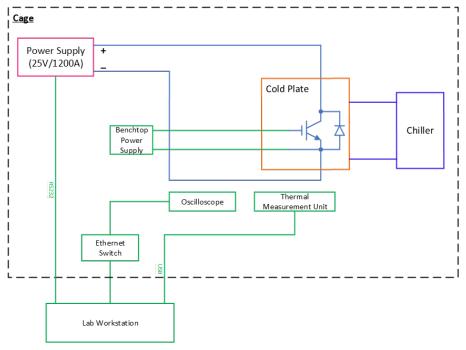

| Figure 4.1  | Nominal Thermal Test Configuration Including Hardware, Instrumentation, and Controls | 84  |

|-------------|--------------------------------------------------------------------------------------|-----|

| Figure 4.2  | IGBT Module with Modified Bus Bar Connection Plate                                   | 85  |

| Figure 4.3  | IGBT Module with Bus Bars Connection Plate Removed, Chips Exposed                    | 86  |

| Figure 4.4  | IGBT Module Chip Closeup                                                             | 86  |

| Figure 4.5  | Chip Temperature Measurement with Fiber Optic Temperature Probe                      | 87  |

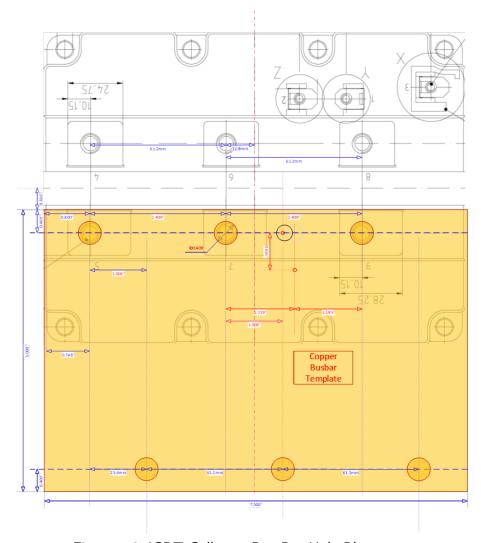

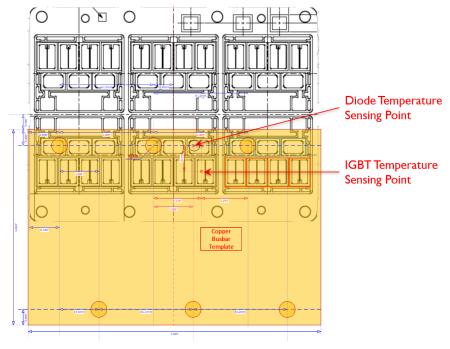

| Figure 4.6  | IGBT Collector Bus Bar Hole Placement                                                | 88  |

| Figure 4.7  | IGBT Modified Collector Bus Bar and IGBT Chip Placement                              | 89  |

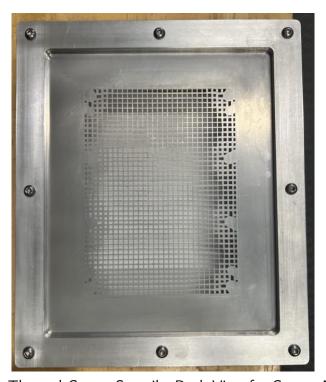

| Figure 4.8  | Thermal Grease Stencil - Back View for Grease Application                            | 90  |

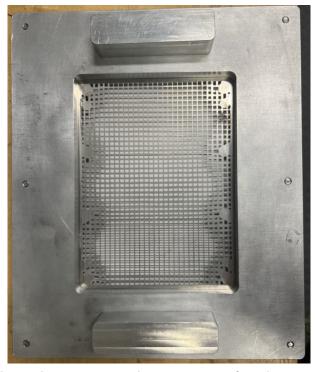

| Figure 4.9  | Thermal Grease Stencil - Front View for Aligning IGBT Module                         | 91  |

| Figure 4.10 | Instrumentation Configuration for Thermal Performance Test                           | 93  |

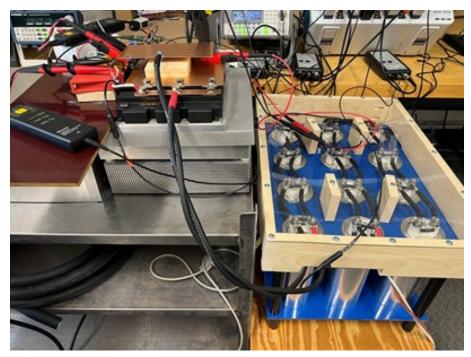

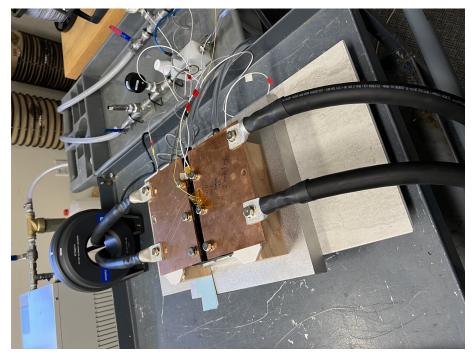

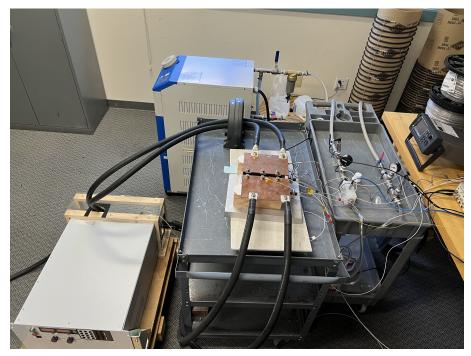

| Figure 4.11 | Hardware Assembled Testing Setup for Thermal Performance Test                        | 94  |

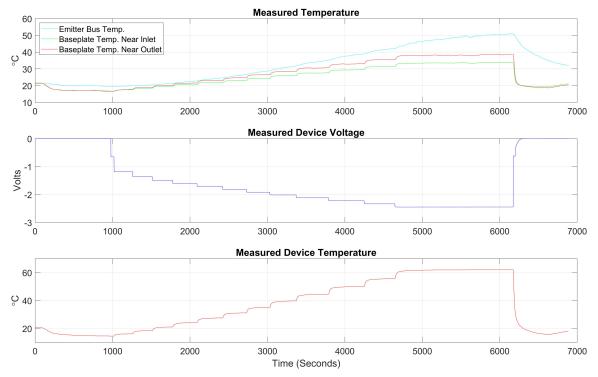

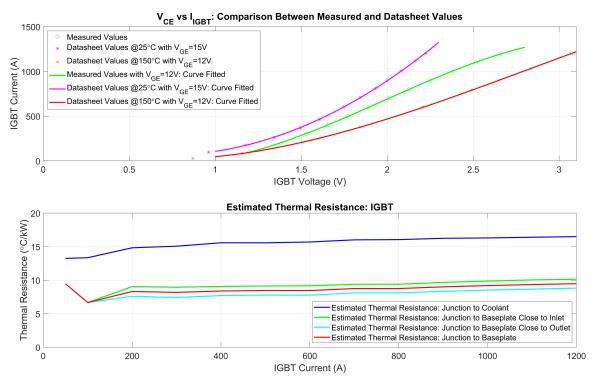

| Figure 4.12 | $V_{GE}$ =15 V IGBT Thermal Performance Test Recorded Data                           | 96  |

| Figure 4.13 | $V_{\text{GE}}$ =15 V IGBT Thermal Performance Test Postprocessed Data .             | 97  |

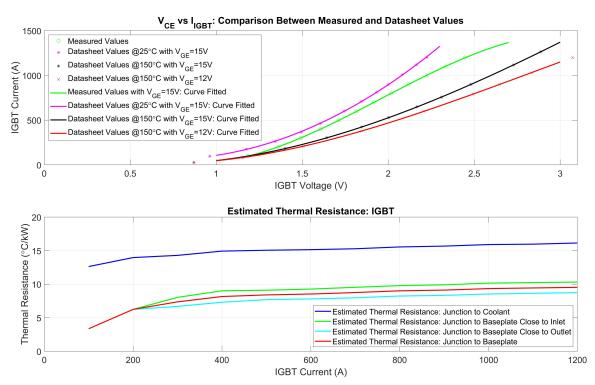

| Figure 4.14 | $V_{GE}$ =12 V Thermal Performance Test Recorded Data                                | 100 |

| Figure 4.15 | $V_{GE}$ =12 V Thermal Performance Test Postprocessed Data                           | 101 |

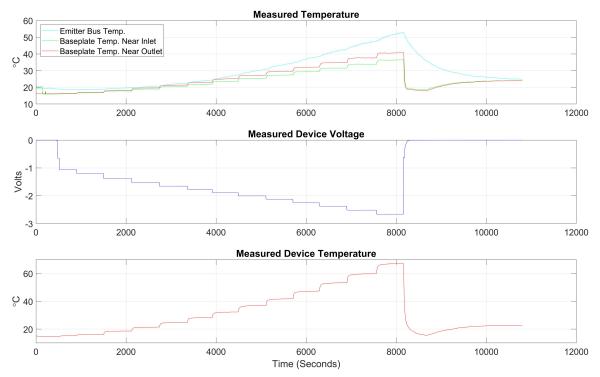

| Figure 4.16 | $V_{GE}$ =-8 V Diode Thermal Performance Test Recorded Data                          | 104 |

| Figure 4.17 | V <sub>GE</sub> =-8 V Diode Thermal Performance Test Postprocessed Data.             | 105 |

### List of Tables

| Table 3.1  | $V_{GE}$ =15 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ $L_{sys}$ =25 $\mu$ H                                                                                                                            | 32 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2  | $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =6800 pF, $R_{STO}$ =4 Ω, $R_{off}$ =4 Ω, $L_{sys}$ =25 $\mu$ H and 50 $\mu$ H                                                                                                                                   | 36 |

| Table 3.3  | $V_{GE} = 12 \text{ V}, R_{on} = 0.3 \Omega, C_{blanking} = 6800 \text{ pF}, R_{STO} = 4 \Omega, R_{off} = 4 \Omega, L_{sys} = 2 \mu \text{H} \dots \dots$ | 41 |

| Table 3.4  | $V_{GE} = 10 \text{ V}, R_{on} = 0.3 \Omega, C_{blanking} = 6800 \text{ pF}, R_{STO} = 4 \Omega, R_{off} = 4 \Omega, L_{sys} = 2 \mu \text{H} \dots \dots$ | 43 |

| Table 3.5  | $V_{GE}=12 \text{ V}, R_{on}=0.3 \Omega, C_{blanking}=6800 \text{ pF}, R_{STO}=4 \Omega, R_{off}=4 \Omega, L_{sys}=1 $ $\mu\text{H}$                                                                                                                             | 45 |

| Table 3.6  | $V_{GE}=10 \text{ V}, R_{on}=0.3 \Omega, C_{blanking}=6800 \text{ pF}, R_{STO}=4 \Omega, R_{off}=4 \Omega, L_{sys}=1 $ $\mu\text{H}$                                                                                                                             | 47 |

| Table 3.7  | Narrow Bus Bar, "Hole #1," $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =1 $\mu$ H                                                                                                                | 50 |

| Table 3.8  | Narrow Bus Bar, "Hole #2," $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =1 $\mu$ H                                                                                                                | 51 |

| Table 3.9  | Narrow Bus Bar, "Hole #3," $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =1 $\mu$ H                                                                                                                | 52 |

| Table 3.10 | Z-Shaped Bus Bar, "Hole #1," $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =1 $\mu$ H                                                                                                              | 55 |

| Table 3.11 | Z-Shaped Bus Bar, "Hole #2," $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =1 $\mu$ H                                                                                                              | 56 |

| Table 3.12 | Z-Shaped Bus Bar, "Hole #3," $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =6800 pF, $R_{STO}$ =4 $\Omega$ , $R_{off}$ =4 $\Omega$ , $L_{sys}$ =1 $\mu$ H                                                                                                              | 56 |

| Table 3.13 | $V_{GE}$ =12 V, "Hole #3," $R_{on}$ =0.3 Ω, $R_{off}$ =4 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =10 Ω, $L_{sys}$ =1 $\mu$ H, $t_{on}$ 10 $\mu$ s                                                                                                                 | 59 |

|            |                                                                                                                                                                                                                                                                  |    |

| Table 3.14 | $V_{GE}=12$ V, $R_{on}=0.3$ $\Omega$ , $C_{blanking}=13400$ pF, $R_{STO}=10$ $\Omega$ , $R_{off}=4$ $\Omega$ , $L_{total}=0.65$ $\mu$ H, $t_{on}$ 10 $\mu$ s                                                         | 64  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.15 | Room Temperature, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =13400 pF, $R_{STO}$ =22 $\Omega$ , $R_{off}$ =10 $\Omega$ , $L_{total}$ =0.65 $\mu$ H, $t_{on}$ =10 $\mu$ s                               | 66  |

| Table 3.16 | Room Temperature, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =13400 pF, $R_{STO}$ =22 $\Omega$ , $R_{off}$ =10 $\Omega$ , $L_{sys}$ =25 $\mu$ H, $t_{on}$ =100 $\mu$ s                                  | 68  |

| Table 3.17 | Room Temperature, $V_{GE}$ =12 V, $R_{on}$ =0.3 $\Omega$ , $C_{blanking}$ =13400 pF, $R_{STO}$ =22 $\Omega$ , $R_{off}$ =10 $\Omega$ , $L_{sys}$ =50 $\mu H$                                                         | 70  |

| Table 3.18 | T <sub>j</sub> 100 °C, V <sub>GE</sub> =12 V, R <sub>on</sub> =0.3 Ω, C <sub>blanking</sub> =13400 pF, R <sub>STO</sub> =22 Ω, R <sub>off</sub> =10 Ω, L <sub>total</sub> =0.65 $\mu$ H, t <sub>on</sub> =10 $\mu$ s | 72  |

| Table 3.19 | $T_j$ =100 °C, $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =22 Ω, $R_{off}$ =10 Ω, $L_{sys}$ =25 $\mu$ H, $t_{on}$ =100 $\mu$ s                                                             | 73  |

| Table 3.20 | $T_j$ =100 °C, $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =22 Ω, $R_{off}$ =10 Ω, $L_{sys}$ =50 $\mu$ H, $t_{on}$ =100 $\mu$ s                                                             | 76  |

| Table 3.21 | 2P2S MOV configuration, $V_{GE}$ =12 V, $R_{on}$ =0.3 Ω, $C_{blanking}$ =13400 pF, $R_{STO}$ =22 Ω, $R_{off}$ =22 Ω, $L_{sys}$ =25 $\mu$ H, $C_{MOV}$ =3300 pF                                                       | 79  |

| Table 4.1  | IGBT Thermal Test, $V_{GE}$ =15 V, $I_{C}$ =100-1200 A                                                                                                                                                               | 95  |

| Table 4.2  | IGBT Thermal Test, $V_{GE}$ =12 V, $I_{C}$ =100-1200 A                                                                                                                                                               | 99  |

| Table 4.3  | Diode Thermal Test, V <sub>GE</sub> =-8 V, I <sub>F</sub> =100-1200 A                                                                                                                                                | 103 |

### List of Acronyms and Abbreviations

**AC** Alternating Current

**BAA** Broad Agency Announcement

**BOD** Breakover Diode

**CB** Circuit Breaker

**DC** Direct Current

**DLO** Diesel Locomotive Cable

**EMI** Electromagnetic Interference

FLASH Fast Light-weight Altitude-Ready Solid State Circuit Breaker for Hybrid

**Electric Propulsion**

**GPM** Gallons per Minute

**IGBT** Insulated Gate Bipolar Transistor

**IGCT** Integrated Gate Commutated Thyristor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

**MOV** Metal Oxide Varistor

**MVDC** Medium Voltage Direct Current

MW megawatt

NASA National Aeronautics and Space Administration

**NEAT** NASA Electric Aircraft Testbed

**NPS** Naval Postgraduate School

**ONR** Office of Naval Research

**RC** Resistor-Capacitor

**RTD** Resistance Temperature Detector

**SCR** Silicon Controlled Rectifier

**SSCB** Solid State Circuit Breaker

**STO** Soft Turn Off

TVS Transient Voltage Suppressor

### Acknowledgments

I'd like to thank Dr. Di Zhang for welcoming me into this project. The opportunity to work hands-on in the development of this SSCB was immensely rewarding and enjoyable. I cannot think of a better project to learn more about power electronics while enjoying the process along the way.

I'd like to thank Dr. Yuntao Xu for the wealth of knowledge and experience you brought into the lab and our thesis discussions. Your attention to detail, need for clarity and accuracy, and the ability to communicate complex ideas made understanding the breadth of material achievable and enjoyable. The time spent together in the lab designing, building, and testing the circuitry was such a delight.

I'd like to thank Mr. Bob Broadston for navigating the NPS bureaucracy and getting the high power lab approved and ready for use. Your assistance in acquiring and assembling the hardware and various components for testing was most appreciated.

I'd like to thank Mr. John Mobley from the MAE machine shop for his immense technical knowledge and capabilities in achieving our design goals. Your creativity and assistance made each of the crazy requests we brought you for modifying pieces of equipment for testing, as well as machining necessary components, made completing this thesis possible.

Finally, I'd like to thank my amazing wife, Edith, and our three kids. Your love and support have been everything I could have ever hoped. Whether it's giving me encouragement to continue struggling through my thesis, supporting another sea tour, or something as simple as playing Uno during breakfast, having you in my life has been the greatest joy.

THIS PAGE INTENTIONALLY LEFT BLANK

## CHAPTER 1: Introduction

Medium Voltage Direct Current (MVDC) architectures for power distribution systems are becoming more attractive as industries are realizing the impacts of high-efficiency, high-power density, Direct Current (DC) distribution systems. MVDC distribution systems have been implemented or researched in maritime vessels [1]–[8], DC microgrids [9], [10], and electrified aircraft [11]–[13]. The U.S. Navy demand signal started as early as 2013 with Office of Naval Research (ONR) Broad Agency Announcement (BAA) calling for research into MVDC systems [14].

The rising importance of MVDC systems has led to research into the protection devices used between electric power sources, the distribution buses, and the loads [15]. In Alternating Current (AC) systems, a mechanical Circuit Breaker (CB) is typically used which can open contacts and interrupt fault current at zero crossings of the AC currents . DC power systems do not inherently have a zero current crossing, and must therefore, utilize a fault interruption system that can handle high voltage and high current simultaneously. Solid State Circuit Breaker (SSCB) technology can manage this fault interruption with no moving parts, no arc flash, and at rates far superior to their legacy counterparts [9], [15], [16].

### 1.1 Significance of Research

The SSCB tested in this study is a high-power density, high-efficiency, and high-reliability design with a power rating of 2.4 MW for hybrid-electric aircraft applications. Due to its benefits, such a SSCB can also be applied in U.S. naval vessels, DC microgrids, and other systems utilizing DC distribution systems. The compactness and low loss of the SSCB can provide designers with increased design freedom and flexibility.

An MVDC distribution system relies upon connecting AC generators to the DC bus through various power electronics elements, such as three phase rectifier and inverters [7], [8]. Through the use of power converters, the speed of the generators is decoupled from the load conditions, including the load level and required motor speed. In other words, the generators may operate at any speed to achieve the highest system efficiency regardless of the power

requirements of the loads [2], [3]. In addition, the generator does not need to work at the harmonics of 50 or 60 Hz. This will further enhance U.S. Navy capabilities by reducing the acoustic signature of the ship [17].

On critical systems, two electric sources are provided for reliability to ensure protection against loss of power. In an AC system, when two parallel sources of electric power are combined, in order to minimize the associated current surge when the CB is closed, the amplitudes, phase angle, and frequency of the voltages on the two sides of the CB must be matched. Critical DC power systems technology has previously utilized auctioneering diodes, providing power from one of at least two DC sources to the load, depending on the operating source with the highest voltage at the time less the voltage drop across the diode [18]. These auctioneering diodes and the critical loads themselves still need fault protection provided by an SSCB. However, without an AC source with its inherent large impedance, the total system impedance will be reduced, and the MVDC system and SSCB need to account for a potentially higher surge current developing as a result [19]. The DC distribution system can also benefit from reduced power cabling size as the AC distribution system is affected by the skin effect of transmission cables and loads have no reactive current component, limiting the total system current to only the real component transmitted through the entire power cable [17].

MVDC research interest was expressed by ONR in the 2013 BAA as well as in the Technology Development Roadmap [4], [14]. Further guidance and study has been conducted with efforts for interface standards for naval vessels [20]. These efforts have been necessary for describing the future of U.S. Navy MVDC distribution and giving guidance to future research. This direction has resulted in developments and improvements in electric propulsion, pulsed power loads, and large DC loads on a growing MVDC bus [7], [8], [21].

In addition to researches into naval applications, MVDC distribution has been explored for aviation applications [9], [12], [13]. Similar advantages that have been capitalized in maritime applications may also be utilized in aviation development. High power densities are necessary due to the weight limitations of an airframe for high system efficiency, as well as space constraints. However, added challenges exist due to operating through lower atmospheric pressures [13].

Advances in SSCB technologies have made the use of MVDC distribution possible. Improvements in the voltage blocking and current carrying capabilities have made Si Insulated Gate Bipolar Transistor (IGBT) selection feasible at useful power levels [22]. This has enabled MW capable devices for power distribution, bus coupling, and load protection [9].

#### 1.2 Research Method

SSCB technology requires gating circuitry to control the on-state and off-state of the power electronics devices, a method to clamp the peak voltage and dissipate inductive energy within the system during the turn-off process, and the current carrying devices under normal operating conditions. The system developed and tested in this research can simulate a rigid DC bus supplying load currents through the SSCB. The SSCB is tested to verify the voltage blocking, current carrying, thermal management, and fault current interruption capabilities. Testing of the SSCB included controlling the current carrying devices, modifications and improvements to the voltage clamping circuitry, and methods to reduce overall inductance within the SSCB for peak voltage limitation. Two different tests are conducted: a switching performance test to quantify the fault protection capabilities of the SSCB and a thermal performance test to quantify thermal efficiency properties of the SSCB. The switching performance test is a high voltage, high current transient test performed in an iterative process that improves various components and functions throughout the SSCB as well as improving the dynamic performance of the SSCB. The thermal test is a low voltage, high current continuous test performed to evaluate the thermal performance of the IGBT, the free-wheeling diode, the cold plate of the SSCB and the cooling system. The physical hardware of the system was assembled and tested within an interlocked safety cage due to the high voltage and current present throughout the testing.

### 1.3 NASA FLASH Introduction

The National Aeronautics and Space Administration (NASA) Fast Light-weight Altitude-Ready Solid State Circuit Breaker for Hybrid Electric Propulsion (FLASH) SSCB development began in early 2020 [23]. This proposal offered a simple and elegant solution for achieving an SSCB with nominal specifications for a coupling device in a hybrid-electric, subsonic aircraft. The plan detailed a 3 year, 3 phase project to advance existing technologies

in a novel implementation to achieve a 2 kV, 1.2 kA SSCB rated for 35 000 feet altitude. This advanced SSCB would continue to promote U.S. Navy deployment of new technologies on aircraft and promote further applications in maritime vessels and DC grids requiring MVDC distribution and high power DC loads [4], [23]. This thesis focused on the second phase of this development: a 2 kV, 1.2 kA SSCB prototype, down-selecting the ideal components to meet or exceed design specifications and deliver a ready-to-test product for NASA Electric Aircraft Testbed (NEAT).

The Naval Postgraduate School (NPS) design proposed to NASA was for a Si semiconductor device that utilized "advanced insulation, control, and packaging technologies" to achieve a novel SSCB for hybrid-electric propulsion aircraft [23]. To make this device suitable for aircraft, it needs to have high power density and high efficiency due to aircraft weight and size limitations. The project would expand upon current U.S. Navy research efforts on MVDC SSCBs that were only in the 1 MW range and provide a 2.4 MW solution with higher power densities than previously achieved [4]. The design criteria included: 2 kV DC voltage, 1.2 kA DC current, 99.5% efficiency, 100 kW/kg specific power, altitude capability at 35 000 ft, and a response time in the tens of µs [23] and is shown in Figure 1.1.

Figure 1.1. Three Year Timeline for SSCB Development and Testing. Source: [23].

This three year project, specifically the second phase, was the impetus for the hardware benchmark testing performed in Chapter 3 and Chapter 4.

### 1.4 Chapter Overview

Chapter 2 discusses the topology and operating principles of the SSCB as well as the NASA FLASH SSCB design improvement theory. Chapter 3 discusses the fault performance switching test used for the SSCB including the hardware, instrumentation, test setup and procedure as well as the results of the test and improvement iterations. Chapter 4 discusses the thermal efficiency performance test used for the SSCB including the hardware, instrumentation, test setup and procedure as well as the results of the test iterations. Finally, Chapter 5 summarizes the testing results and presents ideas for future MVDC SSCB research.

THIS PAGE INTENTIONALLY LEFT BLANK

# CHAPTER 2: Background

In this chapter, the SSCB is introduced. A detailed description of SSCB topology and operating principles are discussed. Understanding the individual components and their functions are essential for the operation as a whole of the SSCB. Finally, the improvements proposed for an SSCB for an MVDC distribution system on a hybrid-electric aircraft are discussed which are the basis for this research project.

#### 2.1 Solid State Circuit Breaker Fundamentals

SSCBs are semiconductor-based power and load protection devices that have much faster fault interruption capability compared with their legacy, mechanical counterparts. These semiconductor devices can interrupt fault currents without arcing due to no moving parts, allowing for longer interruption lifetime and less required maintenance [9]. Their prevalence has grown from the laboratory to commercial and military applications through advances in MVDC technologies. The range of applications continues to grow as power distribution systems are branching from AC to DC distribution methods. The shift in distribution systems has been driven by increased demand for fuel efficiency, more rapid power demand shifts, and ease of maintenance [3], [5], [6], [10]. In military applications, the newest classes of ships utilize electric propulsion engine rooms, DC distribution systems, and pulsed power loads on the DC bus which all require SSCB technology to interface the components of the system [4], [7], [8], [17], [21]. The high-power density, high efficiency, and high reliability of these components have made MVDC distribution and the SSCB essential for the future naval force. In addition to naval vessels, SSCBs are being developed for use in aircraft. Along with reducing carbon emissions and achieving higher fuel efficiencies, the requirements from large DC loads are demanding improvements upon SSCBs [13].

The legacy mechanical circuit breaker used in AC systems relies upon mechanical contacts that are separated to interrupt the system currents from source to load. This mechanical interruption is possible with minimal arcing due to a natural zero crossing of the AC current. In higher power systems, a mechanical circuit breaker may also include an arc chute, which

allows for any arc generated during power interruption to be dissipated through the high resistance chute. Additionally, the mechanical circuit breaker relies upon an air gap to provide galvanic isolation, removing the voltage from one side of the contacts to the other. This system, due to the mechanical actuation of large contacts for interruption, as well as the need to wait for a natural zero crossing, can take as long as tens of milliseconds for fault protection to occur. The mechanical actuation causes wear and tear on moving parts, and the arcs generated can pit the contacts over time, requiring additional maintenance to repair and replace these components.

The legacy AC mechanical circuit breaker is insufficient for MVDC distribution systems as there are no inherent zero current crossings in DC systems. Any interruption of current by these devices will generate severe arcs, requiring larger arc chutes than seen on an equivalent AC system. An SSCB utilized in MVDC applications prevents arc generations through the use of solid-state power electronic devices. The current interruption by these devices has no moving parts, eliminating the process by which an arc is generated. To dissipate the inductive energy within the system, a voltage clamping device is used that rapidly converts the energy into heat.

The inductive energy mainly comes from system line inductance, the current limiting devices, and parasitic inductance within the solid-state devices [11]. The basic equation describing the inductance, voltage, and current relationship is described as

$$di/dt = \frac{V_{sys}}{L_{sys} + L_{CB}} \tag{2.1}$$

where  $L_{sys}$  is the system line inductance and  $L_{CB}$  is the current limiting inductance added to the SSCB and any parasitic inductance within the SSCB control circuitry. The peak fault current achieved during fault interruption is defined as

$$I_{pk} = I_{th} + \frac{V_{sys}}{L_{sys} + L_{CB}} * t_d$$

(2.2)

where  $I_{th}$  is the threshold current for fault detection, and  $t_d$  is the response time from fault detection to current interruption. Based on Equation 2.2, if  $L_{sys}$  is close to zero in the worst case, a current limiting inductor must be installed in the SSCB to limit di/dt, such that the peak current will not exceed a maximum threshold within  $t_d$ . Although a lower  $I_{th}$  and  $t_d$

can help to limit the fault current, allowing the protection system to respond to a system fault earlier and faster, the impact is limited if the system current rising rate is very high. In addition, a lower I<sub>th</sub> or t<sub>d</sub> could make the SSCB sensitive to the system noise, especially in a harsh Electromagnetic Interference (EMI) environment, such as the converter based high power system.

If the fault current is interrupted by the semiconductor device directly, a transient over-voltage can damage the SSCB. The transient over-voltage can be estimated as

$$V_{SSCB} = V_{sys} + L_{total} * di/dt$$

(2.3)

where the system inductance,  $L_{total}$  is the algebraic sum of system inductance and SSCB parasitic and installed inductance. For example, if the total inductance is  $10 \,\mu\text{H}$  and the di/dt is  $1 \,\text{kA/}\mu\text{s}$ , such a transient over-voltage is  $10 \,\text{kV}$ , which is likely in excess of design parameters. To overcome this issue, a voltage clamping circuit, such as a Metal Oxide Varistor (MOV), is connected in parallel with the SSCB to limit the maximum voltage experienced by the circuit.

### 2.2 SSCB Design Considerations

An SSCB consists of three main elements: the current carrying and interrupting device, the fault current limiting device, and the voltage clamping and energy dissipation circuit. Typically, the current carrying and interrupting device is an IGBT, Metal Oxide Semiconductor Field Effect Transistor (MOSFET), or Integrated Gate Commutated Thyristor (IGCT) [9]. These semiconductor devices have seen improvements over the years that have led to higher voltage and higher current carrying capabilities while reducing on-state power losses, making them the backbone of MVDC electrical distribution systems and supporting newer high power loads. While the details and intricacies vary within a given SSCB topology, these components are generally universal to any given system. Other components include passive or active sensing and controlling devices, remote operating and communications devices, or additional semiconductor devices to overcome previous inadequacies in voltage blocking, current carrying, or energy dissipation effects [9], [10].

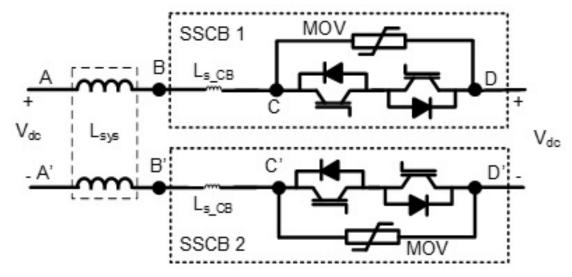

Because the IGBT itself can only conduct current in one direction, an anti-parallel diode is

placed from the IGBT emitter to the IGBT collector. This allows for bidirectional current conduction. However, this configuration only allows voltage blockage in the forward direction when the IGBT is in the off-state. To ensure voltage blockage in both directions, two anti-series IGBTs are necessary. Without the second IGBT in an anti-series configuration, the IGBT would only be able to block voltage in the forward direction, as the anti-parallel diode becomes forward biased if a negative voltage was applied across the IGBT as seen from collector to emitter. The IGBTs are placed in a configuration where the conduction path in either direction goes from emitter to collector of one IGBT through the diode, then collector to emitter through the second IGBT in the on-state. This is referred to as an "ECCE" configuration. The second configuration is where the emitters of the IGBTs are connected, referred to as an "CEEC" configuration, and is shown in Figure 2.1. Both configurations are functionally the same with current conduction through one IGBT and one diode.

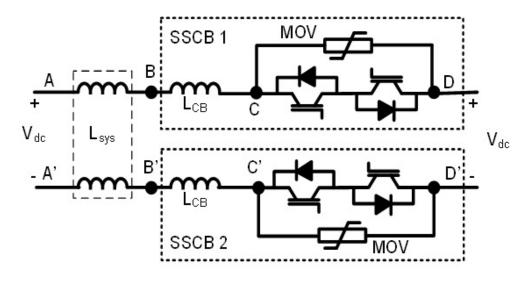

Figure 2.1. Generic "CEEC" SSCB Topology

The two anti-series IGBTs with anti-parallel diodes are connected with a parallel MOV branch. The MOV acts as the energy dissipation circuitry, providing a path for current commutation when the SSCB is turned off. Additionally, the MOV branch provides for voltage clamping, acting in a highly non-linear fashion when dissipating the inductive energy of the system. Also shown in Figure 2.1 is a series connected, current limiting inductor.

The inductor, when installed, aids the SSCB in limiting the current rate of change during a fault. This device yields additional time for the SSCB to detect and clear a fault current while minimizing the peak current experienced during the fault. However, the inductor adds additional weight to the system, dramatically lowering the SSCB power to weight ratio, or, the specific power. Additionally, because the inductor is in line with the SSCB, it will carry full system current when operational, adding further losses to the system, reducing the SSCB efficiency.  $L_{\rm sys}$  is the system inductance of the MVDC system determined mainly by the length and type of cabling used.  $L_{\rm CB}$  is the parasitic inductance of the SSCB as well as any additional current limiting inductor.

To ensure single-point fault protection, demonstrated in Figure 2.2, IGBTs are placed in the anti-parallel, anti-series configuration as shown in Figure 2.1. In Figure 2.1, an SSCB is placed on each pole. This layout does demand four IGBTs within a single conduction loop, increasing the amount of conduction losses throughout the system, affecting the total system efficiency. However, this configuration can allow the system to continuously operate at full power with single point ground fault.

Figure 2.2. A Basic Fault on One Leg of the SSCB

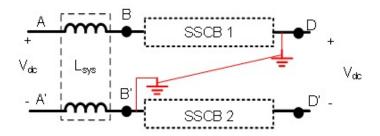

In a critical system on board an aircraft, for example, the system must be capable of continual operation at full power with single point ground fault. For this reason, an SSCB is installed on each pole of the MVDC distribution legs. Should a single point fault occur, one SSCB would be sufficient to interrupt that fault as shown in Figure 2.2. In this case, both SSCBs would share the voltage blocking from the source to the fault. Should a second fault on the opposite pole occur, this second fault may bypass one of the two SSCBs in the system, requiring a single SSCB to interrupt the fault current and block all system voltage. Shown

in Figure 2.3, one fault occurs downstream of the positive pole SSCB and a second fault occurs on the upstream side of the negative pole SSCB. This fault bypasses the negative pole SSCB as viewed in Figure 2.3.

Figure 2.3. Design Case Fault Where One SSCB is Removed From the System

This is the fault each SSCB needs to be designed to handle. Thus, the IGBT and the auxiliary system components must be rated sufficiently to handle the total system voltage as well as any additional inductive voltage experienced during transient fault protection. To reduce cost and weight, the voltage rating of the device should be minimized to limit conduction losses from the SSCB.

### 2.2.1 Solid State Circuit Breaker Functionality

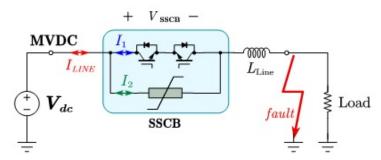

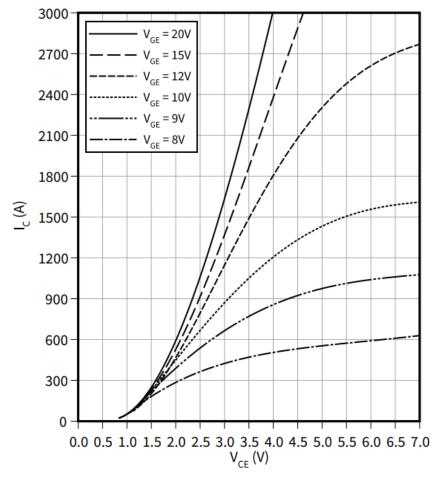

To enable the IGBT-based SSCB, a positive voltage, called gate voltage, is supplied to the gate terminal of the IGBT which allows the device to conduct in the forward direction. This is referred to as the IGBT on-state. When the IGBT is carrying current,  $I_C$ , the voltage across the IGBT,  $V_{CE}$ , will increase correspondingly. The voltage and current relationship is non-linear which is heavily affected by applied gate voltage,  $V_{GE}$ , as is shown in Figure 2.4, and is referenced to a 150 °C junction temperature. Due to the physics in developing a conduction channel, the higher the gate voltage applied, the lower the resistivity within the IGBT channel. In turn, this results in lower conduction loss.

Figure 2.4. IGBT Operating Curves for Various Gate Voltages. Source: [24].

The IGBT in an SSCB normally operates in the saturation region when the load current is within its rated range, and the voltage drop across the device is only a few volts. However, once the current is sufficiently high, the IGBT will exit the saturation region and enter the active region. Consequently, the IGBT voltage will increase dramatically with the load current, until the IGBT reaches the saturation current level, which appears as a flattened curve in Figure 2.4. However, a small change in gate voltage in the active region can result in massive shifts in the saturation current level.

To turn off the IGBT, the gate voltage is removed, or forced to a negative value. As the voltage potential is removed from the gate, or a negative voltage is applied, the conduction channel

rapidly narrows until the current is reduced to zero. However, the inherent inductance within the system will continue to drive the current. As the IGBT is turned off, the current is commutated to the energy dissipation component, generally a MOV.

The MOV performs two functions: it clamps the voltage rise due to the inductance of the system as described in Equation 2.1 as well as dissipates the inductive energy into heat. A MOV can clamp the voltage similar to back-to-back zener diodes. When the voltage across the MOV is low, the resistance internal to the MOV is very high, mirroring an open circuit, allowing very little leakage current through the device. As the voltage across the MOV increases, the MOV resistance decreases. Thus, limited voltage will appear across the MOV when it is carrying high fault current. In other words, the MOV clamps the voltage across the IGBT, so the IGBT does not experience excessive voltages described in Equation 2.3, which may result in punch through of the solid-state device, causing failure.

Since the clamping voltage of the MOV is higher than the DC bus voltage, the voltage difference will drive the system fault current down eventually clearing the fault. During the fault clearing process, the current of the MOV can be expressed as

$$i_{MOV} = i_{peak} - \frac{V_{clamp} - V_{DC}}{L_{sys} + L_{CB}} * t_{clear}$$

(2.4)

where  $L_{sys}$  and  $L_{CB}$  are the system and SSCB inductances respectively,  $V_{clamp}$  is the clamping voltage of the MOV,  $i_{peak}$  is the peak fault current, and  $t_{clear}$  is the time to clear the fault.

Since the MOV is carrying high fault current and withstanding high clamping voltage at the same time, the MOV generates high power loss which can only be absorbed by the MOV itself. Such dissipated energy will heat the MOV internally, causing degradation or even failure of the metal-oxide material. A single event with sufficient energy or several events with sufficient accumulated energy in a short period may cause the same catastrophic effect.

If the clamping voltage is considered approximately constant, the total energy absorbed by the MOV can be calculated as

$$E_{MOV} = \frac{1}{2} * (L_{sys} + L_{CB}) * I_{peak}^{2} * \frac{V_{clamp}}{V_{clamp} - V_{DC}}$$

(2.5)

where the inductance, voltage, and current are defined the same as in Equation 2.4. By

fixing the system operating voltage, and selecting an appropriate clamping voltage, the energy dissipated through the MOV is proportional to the sum of the inductances and the square of the peak current. Minimizing the energy dissipated in the MOV will result in less required maintenance to replace a MOV prior to failure, generating longer useful lifetime of a MOV and the SSCB.

Assisting the MOV in operation, a Resistor-Capacitor (RC) snubber may be included. The introduction of a capacitive element into the circuit limits the voltage rate of change during the turn-off transient expressed as

$$i_C = (C_{snubber} + C_{CB}) * dv/dt$$

(2.6)

where  $C_{snubber}$  is the RC snubber capacitance and  $C_{CB}$  is the parasitic capacitance within the SSCB. An RC snubber cannot effectively limit the peak voltage alone, because of the low energy density of the capacitor. In addition, the RC snubber may cause an oscillation in the voltage across the IGBT due to the interaction with the system inductance. Thus, an RC snubber is generally used to limit the transient voltage rising rate only, and the peak SSCB voltage is clamped by the MOV.

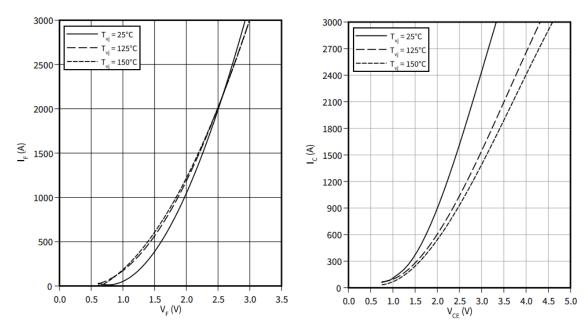

During normal operation, the voltage across the SSCB is determined by the on-state IGBT and diode voltage drops. Each of these devices experiences a non-linear voltage rise with respect to the conducted current. Figure 2.5 shows the nominal I-V curves for the forward biased diode and the on-state IGBT at different operating temperatures. The IGBT has a positive temperature coefficient, resulting in a higher  $V_{CE}$  at higher temperatures for the same  $I_C$ , whereas the diode experiences a negative temperature coefficient in the rated load current range of the SSCB, resulting in lower  $V_F$  at higher temperatures for the same  $I_F$  [24].

Figure 2.5. I-V Curves for Diode and IGBT. Source: [24].

For the 3.3 kV module in [24], when a 1200 A flows through the SSCB at 25  $^{\circ}$ C with V<sub>GE</sub>=15 V, the voltage drop across the IGBT and the diode are 2.3 V and 2.2 V respectively. As the temperature goes up, the voltage drop across the IGBT goes up while the voltage drop across the diode slightly goes down. This keeps the on-state voltage in one SSCB relatively constant near 4.5 to 5 VDC.

Since the IGBT module is not switched continuously, the efficiency of the SSCB depends on the conduction losses of the IGBT and diode which are determined by the load current and applied gate voltages. The gate voltage also determines the point at which the IGBT transitions from the saturation region, where the voltage across the IGBT is relatively low, to the active region, where the voltage across the IGBT is significantly high. For example, at 150 °C, when 15 V applied to the gate, the IGBT will saturate at 6.4 kA. Due to the positive temperature coefficient explained above, at lower temperatures, this saturation current would be at even higher values. At 150 °C, with 12 V gate voltage, the IGBT will start to exit the saturation region at 2.7 kA. At lower temperatures, such transition will occur at a higher current. During a fault condition, the current through the IGBT will first rise rapidly, but will eventually be limited to the current saturation level of the IGBT. Therefore, the peak

fault current can be limited and remain constant even without a current limiting inductor until the control circuitry turns off the IGBT.

A lower gate voltage can reduce the peak fault current. However, by operating at a lower gate voltage, the IGBT experiences higher conduction losses. From Figure 2.4, for a target of 1200 A, a 15 V gate, which is typically recommended by the devices vendors, would lead to a 2.8  $V_{CE}$  drop across the IGBT. At the same current, a gate of 12 V increases the  $V_{CE}$  to a 3.1 V. In other words, this reduced gate voltage would introduce an additional 360 W of power losses internally to the IGBT when operating at nominal system voltage and current values. For a nominal 2.4 MW MVDC system operating at 2 kV and 1.2 kA, the 360 W of power loss introduced in the IGBT would only represent a 0.03% increase in system losses through two operating SSCBs. This loss is negligible for a targeted efficiency of 99.5%. Especially, the additional loss can be partially compensated by the elimination of the current limiting inductor introduced in Section 2.3.

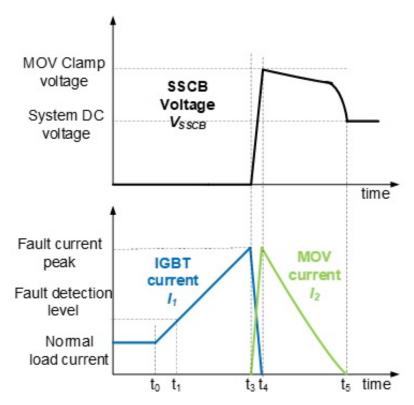

The typical switching waveforms of a traditional SSCB are shown in Figure 2.6. The top figure depicts the waveform of the voltage across SSCB,  $V_{SSCB}$ , and the bottom figure depicts the waveforms of the current flowing through the IGBT,  $I_1$ , and the current through the MOV,  $I_2$ . As shown in Figure 2.6, before  $t_0$ , the system is under normal operation,  $V_{SSCB}$  is close to zero, and the system current only flows through the IGBT. At  $t_0$ , a short circuit fault occurs, and the IGBT current will increase rapidly. The rising rate is determined by the DC bus voltage,  $V_{DC}$ , the value of system inductance,  $L_{sys}$ , and the inductance of the current limiting inductor,  $L_{CB}$ , as described in Equation 2.1. Once the fault current exceeds the predefined protection threshold,  $I_{th}$ , at  $t_1$ , the fault protection scheme is activated. As the protection is activated, the fault current will continue to increase until the IGBT is turned off at  $t_3$  and the fault current is commutated from IGBT to MOV from  $t_3$  to  $t_4$ . All the energy in the system is dissipated through the MOV from  $t_4$  to  $t_5$  where no further current flows and the SSCB blocks nominal bus voltage.

Figure 2.6. MOV Clamped SSCB Voltage During Nominal Operation

When the IGBT begins to turn off, the current is commutated through the RC and MOV parallel branches where it is converted into heat. The voltage across the SSCB is reduced from the peak until no further current flows, and the SSCB voltage equals the system voltage described in Equation 2.3. This interruption process is shown in Figure 2.6 from  $t_3$  to  $t_5$ . This voltage limiting process is handled entirely by the MOV. Without sufficient design margin, the MOV may be subjected to excessive energy dissipation, described in Equation 2.5, causing catastrophic failure of the MOV. The peak current amplitude and clamping duration determine the selection of the appropriate MOV for the voltage clamping and energy dissipation portion of the SSCB.

Protection of the IGBT module is provided by the gating circuitry through a number of components. The most critical protection function is called desaturation protection. As mentioned above, the IGBT will exit the saturation region when high current saturates the

device, causing the voltage across the IGBT to increase. When the IGBT is turned on, the blanking capacitor, C<sub>blanking</sub>, will begin to charge. The charging rate is determined by an RC time constant. The charging process stops when the IGBT enters the saturation region and V<sub>CE</sub> drops below the voltage of the blanking capacitor. During a fault as I<sub>C</sub> increases, the IGBT voltage increases as well, resuming the charging of the blanking capacitor when V<sub>CE</sub> rises above the voltage across the blanking capacitor. Once the voltage of the blanking capacitor is higher than a preset value, for example 8 V, the gate drive will turn off the IGBT. Proper tuning of the blanking capacitor is necessary to guarantee a proper detection process to prevent inadvertent protections when turning on an IGBT or due to system noise. The Soft Turn Off (STO) resistor,  $R_{STO}$ , provides a soft turn-off effect for the IGBT module by using a resistance typically higher than that used for the normal turn-off process. A higher R<sub>STO</sub> results in a longer time to discharge the IGBT gate capacitance, resulting in a slower IGBT turn-off process. This reduces the di/dt during the turn-off transient, lowering peak IGBT voltage. The other two components within the gating circuitry that control the transient behavior of the IGBT are the turn-on, Ron, and turn-off, Roff, resistors. Ron and Roff control the rate at which the internal capacitances of an IGBT module are charged and discharged, respectively, under normal operation conditions, thus affecting the switching time of the device. As is the case with the R<sub>STO</sub>, a higher turn-on resistance will result in a higher RC time constant, which results in a longer time to turn on the module. This slows down the switching transient from the off to the on state. R<sub>off</sub> performs the same function during the on to off transition.

Resetting the SSCB is as simple as ensuring the fault is cleared, and resupplying the positive gating voltage to the IGBT, turning the SSCB back on. Because there are no moving parts and no closing springs to recharge, the SSCB is rapidly ready to return to operation.

## 2.3 SSCB Hardware Design Improvements

The traditional MVDC SSCB utilizes a current limiting device in the path to reduce the fault current rising rate during fault conditions. An inductor, shown in Figure 2.1, acts to limit the rate of change of current rise through the device. This component adds weight, occupies more space, and reduces the power efficiency and specific power of the SSCB. By reducing the gate voltage and allowing the IGBT to enter the active region during fault

interruption, the SSCB can achieve the same fault interruption capabilities without the bulky inductor [11] and is shown in Figure 2.7.

Figure 2.7. SSCB Design Without a Current Limiting Inductor

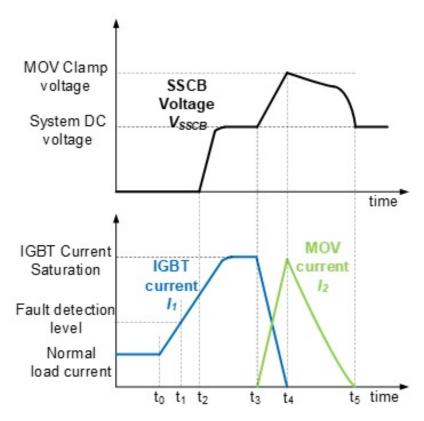

With reduced  $V_{GE}$ , the IGBT exits the saturation region and enters the active region at lower current levels, causing an extreme non-linear change in the I-V characteristics shown in Figure 2.4. The system response to this change in operating behavior is shown in Figure 2.8.

Figure 2.8. MOV Clamped SSCB Voltage with IGBT in Current Saturated Active Region Mode of Operation

As shown in Figure 2.4, a reduced gate voltage will lower the current level when the IGBT starts to enter the active region. When a fault condition occurs, the rise in current is similar to Figure 2.6 with a much higher slope. However, instead of the current continuing to rise until IGBT is turned off, I<sub>C</sub> will saturate and be held nearly constant. This can be seen in the period between t<sub>2</sub> and t<sub>3</sub> in Figure 2.8. In this period, SSCB voltage rises until it reaches the system DC bus voltage. Once the IGBT is turned off, the MOV branch is able to clamp the rise in peak voltage, dissipate the current into heat, and return the SSCB to nominal system voltage.

The MOV is a highly nonlinear device that, in the standby region when the voltage across the MOV is low, appears as a large resistor with low leakage currents in the nA to  $\mu$ A range. In contrast to the high energy rating during transients, the continuous power rating of the device is very low, generally less than 1 W. Therefore, the maximum continuous DC

operating voltage must be higher than the steady state DC voltage. Ideally, the clamping voltage of the MOV should be as close to the nominal DC bus voltage as possible. However, the MOV can only clamp the peak voltage around two to three times the DC bus voltage. For example, a V172BB60 MOV can block up to 2150 VDC continuously, which is higher than 2 kV DC bus. However, the clamping voltage of the MOV when carrying 5 kA is 5 kV. Thus, a 6.5 kV IGBT module must be used to handle the transient voltage, resulting in a higher power loss and cost.

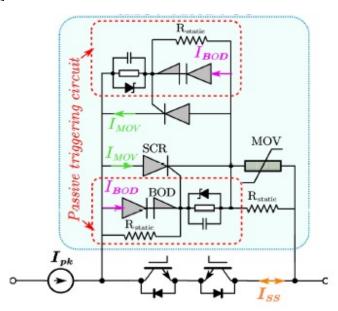

To reduce the peak voltage, a novel voltage clamping circuit is used, as shown in Figure 2.9, which combines mature and reliable Silicon Controlled Rectifier (SCR) technologies with the traditional MOV to reduce the peak clamping voltage. The electronically triggered MOV utilizes an SCR triggered by Breakover Diode (BOD) pairs where the BOD, with an advantage of a sharp breakover voltage, assists the MOV in the standby period improving the maximum blocking voltage of the electronically triggered MOV unit. The SCR, capable of supporting a high pulse current, provides rapid fault current commutation by inserting the MOV into the circuit for fault current dissipation. Additionally, the BOD provides a passive triggering mechanism for the SCR gate, eliminating the need to design separate gate drive circuitry [25].

Figure 2.9. Electronic Triggered MOV Design. Source: [25].

Conduction through the MOV branch is initiated though an SCR that is gated on during current commutation. The gating process happens as the voltage rises as current is commutated to the RC snubber during the initial IGBT turn-off transient, raising the voltage in the SSCB explained in Equation 2.6 to a predetermined level, triggering a BOD, which in turn triggers the SCR. As the SCR is triggered, a path for commutation through the MOV is opened. After that, the MOV clamps the SSCB voltage, drives the fault current to zero, and brings the SSCB voltage to system voltage as described in Equation 2.1 and Equation 2.3.

With the novel voltage clamping design, the voltage rating of the IGBT can be reduced significantly, which can improve the system efficiency. In addition, because there is no need to connected multiple MOVs in parallel to limit the peak voltage, the specific power and power density of the SSCB is also improved compared with the traditional design.

These two major changes are the backbone of this thesis: the function of the current limiting inductor is realized with reduced gate voltage and the peak SSCB voltage is reduced to only 1.5 times higher than system DC voltage with a novel voltage clamping circuit. It is critical to verify the feasibility of the new technologies through a series of experiments.

THIS PAGE INTENTIONALLY LEFT BLANK

# CHAPTER 3: Switching Performance Test

# 3.1 Test Setup

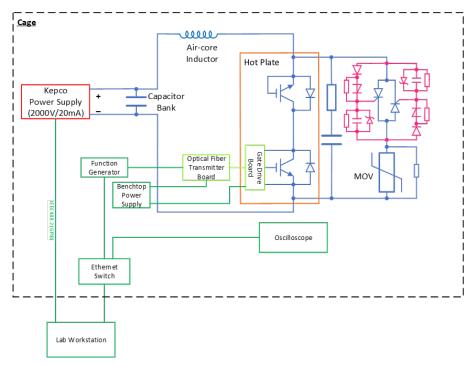

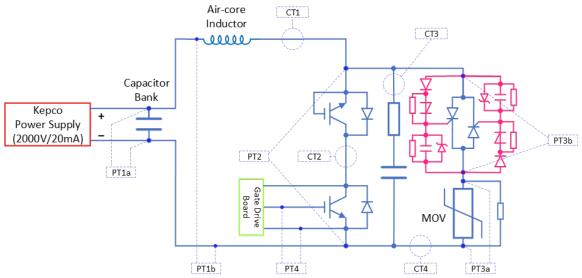

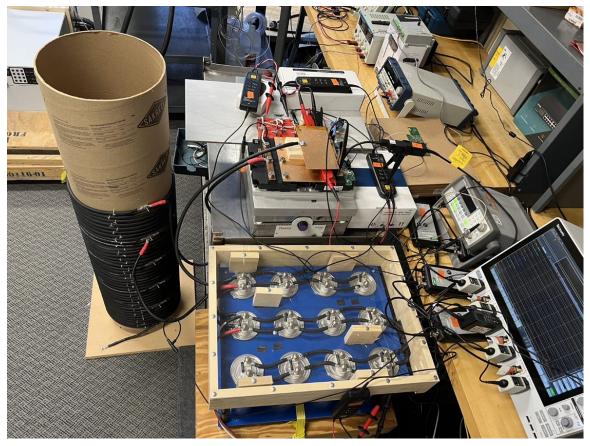

The SSCB system design consists of four IGBT modules arranged in an anti-series, anti-parallel fashion that allows for two-way conduction and bipolar voltage blocking, as well as fault interruption from most line to line short circuit faults and double ground faults. These IGBTs are the current carrying components of the SSCB which also includes the gate control circuitry, fault detection and interruption circuity, and energy dissipation components. The typical MVDC system consists of a rigid DC bus provided by a battery, for example, system inductance from the power cabling or transmission lines, and the DC load, such as motor drives. A nominal test design was developed to simulate a rigid DC bus, transmission line inductance, an SSCB to include control, interruption, and energy dissipation circuitry, and the instrumentation necessary to monitor the circuit variables. The design can be seen in Figure 3.1. Each component of the test setup was selected to meet or exceed required parameters of the NASA FLASH SSCB design.

Figure 3.1. Nominal Switching Test Configuration Including Hardware, Instrumentation, and Controls

The test was designed to simulate the system involving the MVDC distribution bus, one pole of the SSCB, and the related system inductance. Additionally, the required instrumentation and control equipment is included.

#### 3.1.1 Hardware Selection

To simulate a rigid DC bus, a 816  $\mu$ F capacitor bank was selected utilizing 12 capacitors in parallel [26]. This capacitor bank was rated for 2.1 kVDC, exceeding the 2 kVDC bus requirement. The capacitor bank was connected to a DC power supply capable of charging the capacitor bank to the nominal DC bus voltage. A power supply was selected to provide 2 kVDC charging to the capacitor bank, resupplying the system following fault simulation. The power supply was unable to provide any appreciable amount of current during the fault to affect the system performance, limited to 20 mA of output current [27]. The system inductance was simulated utilizing an air-core inductor, with 2 kVDC Diesel Locomotive Cable (DLO) cable [28]. Taps were provided throughout the inductor to allow selection of inductance at 25  $\mu$ H intervals. This allowed for testing from a minimum inductance of